【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验

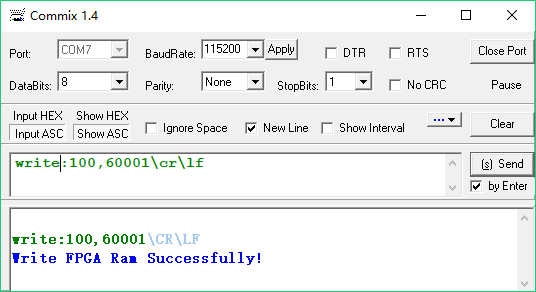

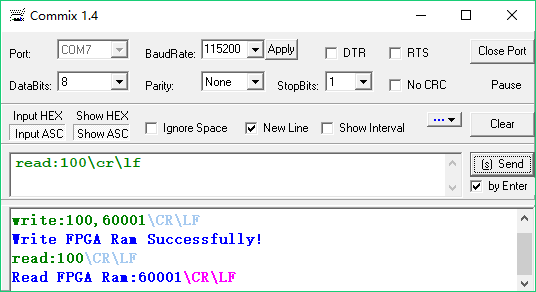

实验现象:

写RAM命令格式:write:地址(0-255),数据(0-65535)\cr\lf

读RAM命令格式:read:地址(0-255)\cr\lf

核心代码:

int main(void)

{ /* USER CODE BEGIN 1 */

int i;

int address,data;

char error_flag = ;

char receive_data[];

char buffer[];

char *p;

/* USER CODE END 1 */ /* MCU Configuration----------------------------------------------------------*/ /* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init(); /* USER CODE BEGIN Init */ /* USER CODE END Init */ /* Configure the system clock */

SystemClock_Config(); /* USER CODE BEGIN SysInit */ /* USER CODE END SysInit */ /* Initialize all configured peripherals */

MX_GPIO_Init();

MX_USART6_UART_Init();

MX_FMC_Init(); /* USER CODE BEGIN 2 */

usart6.initialize();

usart6.printf("Hello, I am iCore4!\r\n"); /* USER CODE END 2 */ /* Infinite loop */

/* USER CODE BEGIN WHILE */

while ()

{

/* USER CODE END WHILE */ /* USER CODE BEGIN 3 */

if(usart6.receive_ok_flag == ){

usart6.receive_ok_flag = ;

memset(receive_data,,sizeof(receive_data));

memset(buffer,,sizeof(buffer));

for(i = ;i < ;i ++){

receive_data[i] = usart6.receive_buffer[i];

}

p = receive_data;

i = ;

while(*p != ':'){ //»ñÈ¡²Ù×÷ÃüÁwrite or read£©

buffer[i++] = *p++;

if(i > sizeof(buffer))i = ;

}

for(i = ;i < sizeof(buffer);i++){//½«ÃüÁîת»¯ÎªÐ¡Ð´×Ö·û

buffer[i] = tolower(buffer[i]);

}

if(memcmp(buffer,"write",strlen("write")) == ){//Ö´ÐÐд²Ù×÷

error_flag = ;

p++;

address = atoi(p);

if(address > )error_flag = ;

p++;

p = strchr(p,',');

if(p == NULL)error_flag = ;

if(!error_flag){

p++;

data = atoi(p);

if(data > )error_flag = ; if(!error_flag){

fpga_write(address,data);

usart6.printf("Write FPGA Ram Successfully!");

}

}

}else{

if(memcmp(buffer,"read",strlen("read")) == ){//Ö´ÐжÁ²Ù×÷

error_flag = ;

p++;

address = atoi(p);

if(address > )error_flag = ;

p++;

if(strchr(p,','))error_flag = ;

if(!error_flag){

data = fpga_read(address);

usart6.printf("Read FPGA Ram:%d\r\n",data);

}

}else{

error_flag = ;

}

}

if(error_flag){

LED_RED_ON;

LED_GREEN_OFF;

usart6.printf("Bad Command!\r\n");

}else{

LED_RED_OFF;

LED_GREEN_ON;

}

}

}

/* USER CODE END 3 */ }

module ram_ctrl(

input clk_100m,

input rst_n,

input wr_n,

input rd_n,

input cs0,

input [:]ab,

inout [:]db,

output led_red,

output led_green,

output led_blue

);

//----------------------------clk------------------------------//

wire wr,rd;

wire [:]data_out; assign wr = wr_n | cs0;

assign rd = rd_n | cs0; reg wr_0,wr_1;

always@(posedge clk_100m or negedge rst_n)

if(!rst_n)

begin

wr_0 <= 'd1;

wr_1 <= 'd1;

end

else

{wr_1,wr_0} <= {wr_0,wr}; wire clk = !wr_1 | !rd;

assign db = !rd ? data_out:'hzzzz; //----------------------------ram------------------------------//

ram u1(

.clock(clk),

.wren(!wr),

.rden(!rd),

.address(ab),

.data(db),

.q(data_out)

); //----------------------------led_ctrl-------------------------//

reg led;

always@(posedge clk or negedge rst_n)

if(!rst_n)

led <= 'd1;

else

led <= ~led; assign {led_red,led_green,led_blue} = {'d1,led,1'd1}; endmodule

源代码下载链接:

链接:http://pan.baidu.com/s/1pKZTJAj 密码:pkf7

iCore4链接:

【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验的更多相关文章

- 【iCore1S 双核心板_FPGA】例程十二:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module single_port_ram( input CLK_12M, input WR, input RD, input CS0, inout [:]DB, input ...

- 【iCore3 双核心板_FPGA】实验十八:基于单口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1i58Ssvz iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore3 双核心板】例程十五:USB_CDC实验——高速数据传输

实验指导书及代码包下载: http://pan.baidu.com/s/1gemYjz9 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore4 双核心板_FPGA】例程十:FSMC总线通信实验——复用地址模式

实验原理: STM32F767上自带FMC控制器,本实验将通过FMC总线的地址复用模式实现STM32与FPGA 之间通信,FPGA内部建立RAM块,FPGA桥接STM32和RAM块,本实验通过FSMC ...

- 【iCore4 双核心板_FPGA】例程十四:基于I2C的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,通过串口精灵给ARM发送数据从而给FPGA发送数据 ,会接收到字符GINGKO. 3.通过串口精灵发送命令可以控制ARM·L ...

- 【iCore4 双核心板_FPGA】例程十一:FSMC总线通信实验——独立地址模式

实验原理: STM32F767上自带FMC控制器,本实验将通过FMC总线的地址独立模式实现STM32与FPGA 之间通信,FPGA内部建立RAM块,FPGA桥接STM32和RAM块,本实验通过FSMC ...

随机推荐

- P2399 non hates math

P2399 non hates math将分数化成小数的模拟题,把循环减掉就可以了.1.1(234)*10^4==11234.234*10^1==11.2349999*(1.1(234))==1122 ...

- Spring Boot 项目实战(一)Maven 多模块项目搭建

一.前言 最近公司项目准备开始重构,框架选定为 Spring Boot ,本篇主要记录了在 IDEA 中搭建 Spring Boot Maven 多模块项目的过程. 二.软件及硬件环境 macOS S ...

- JavaNIO快速入门

NIO是Jdk中非常重要的一个组成部分,基于它的Netty开源框架可以很方便的开发高性能.高可靠性的网络服务器和客户端程序.本文将就其核心基础类型Channel, Buffer, Selector进行 ...

- 每日踩坑 2019-04-08 VS2015未能找到路径“…\bin\roslyn\csc.exe”的解决方案

使用 Nuget 安装 Microsoft.CodeDom.Providers.DotNetCompilerPlatform 包即可. VS2017都是用 roslyn 编译, VS2015原本的编译 ...

- bzoj3545: [ONTAK2010]Peaks 重构树 主席树

题目链接 bzoj3545: [ONTAK2010]Peaks 题解 套路重构树上主席树 代码 #include<cstdio> #include<algorithm> #de ...

- Python3高级基础(2)

1 Python3模拟数据结构 1.1 栈 栈是计算机中经典的数据结构,简单的说,栈就是限制在一端进行插入删除操作的线性表.栈有两种最重要的操作,即pop(从栈顶弹出一个元素)和push(将一个元素进 ...

- 2016年3月12日Android学习笔记

1. //此句不能忘,否则onFling左右滑动不起作用 mLlExamView.setLongClickable(true); mLlExamView.setOnTouchListener(new ...

- The superclass "javax.servlet.http.HttpServlet" was not found on the Java Build

https://jingyan.baidu.com/album/f79b7cb34f40569144023ef9.html?picindex=1

- Codeforces Round #404 (Div. 2) D. Anton and School - 2 数学

D. Anton and School - 2 题目连接: http://codeforces.com/contest/785/problem/D Description As you probabl ...

- [前端] 记录工作中遇到的各种问题(Bug,总结,记录)

最近一年,在开发实践过程中遇到了不少问题,大多都能得到解决 部分知其原理,部分只能做到解决问题,而半年前遇到的问题,或多或少都忘得差不多了 是该记录一下一些问题,防止再遇到就得再查资料了 1. 浏览器 ...