PLL

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利 用锁相环路就可以实现这个目的。

功能:VCO有一个初始的振荡频率,通过设置两个DIV的分频系数可以达到PLL分频或倍频的效果。

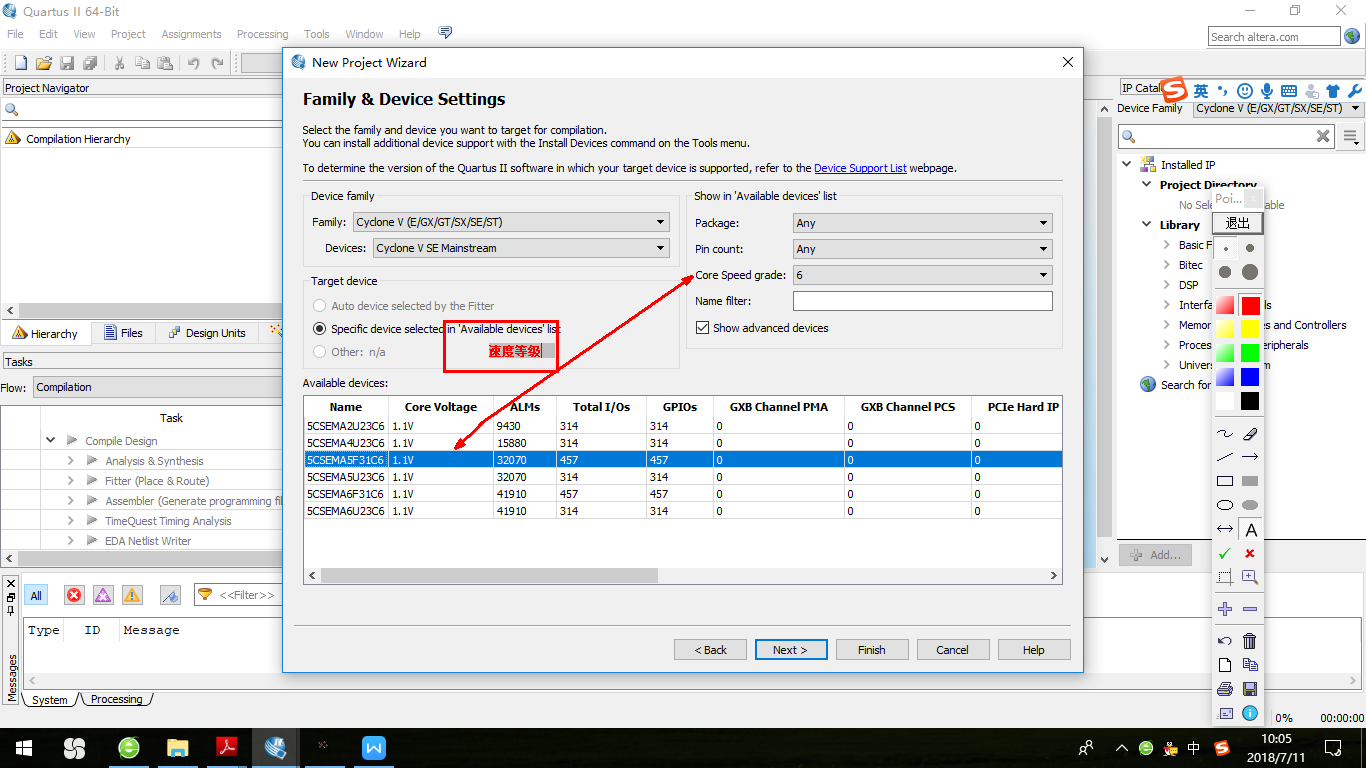

FPGA的PLL IP核配置步骤如下

在IP核中查找pll,选择

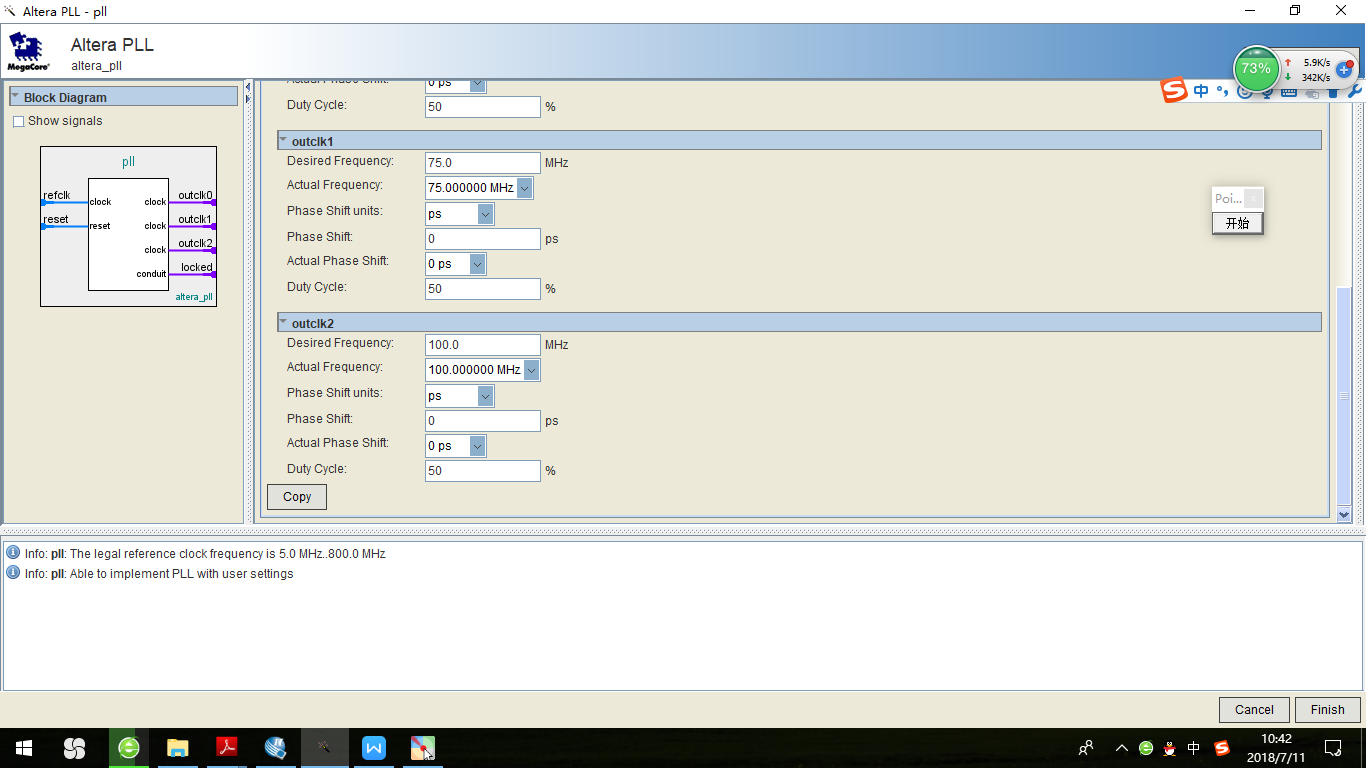

FINISH结束PLL的设置。

50HZ分频为25,75,100;

控制led程序;此段程序为顶层;

module PLL_LED(

Clk,

Rst_n,

LED

); input Clk;

input Rst_n;

output [:]LED; wire c0; //25M

wire c1; //75M

wire c2; //100M wire locked; pll pll(

.rst(~Rst_n),

.refclk(Clk),

.outclk_0(c0),

.outclk_1(c1),

.outclk_2(c2),

.locked(locked)

); counter

#(

.CNT_MAX('d24_999_999)

)

counter0(

.Clk(c0),

.Rst_n(Rst_n),

.led(LED[])

); counter

#(

.CNT_MAX('d24_999_999)

)

counter1(

.Clk(c1),

.Rst_n(Rst_n),

.led(LED[])

); counter

#(

.CNT_MAX('d24_999_999)

)

counter2(

.Clk(c2),

.Rst_n(Rst_n),

.led(LED[])

); counter

#(

.CNT_MAX('d24_999_999)

)

counter3(

.Clk(Clk),

.Rst_n(Rst_n),

.led(LED[])

); endmodule

计数器程序

module counter(

Clk,

Rst_n,

led

); input Clk; //系统时钟

input Rst_n; //全局复位,低电平复位 output reg led; //led输出 reg [:]cnt; //定义计数器寄存器 parameter CNT_MAX = 'd24_999_999; //计数器计数进程

always@(posedge Clk or negedge Rst_n)

if(Rst_n == 'b0)

cnt <= 'd0;

else if(cnt == CNT_MAX)

cnt <= 'd0;

else

cnt <= cnt + 'b1; //led输出控制进程

always@(posedge Clk or negedge Rst_n)

if(Rst_n == 'b0)

led <= 'b1;

else if(cnt == CNT_MAX)

led <= ~led;

else

led <= led; endmodule 编写正确的testbench

`timescale 1ns/1ps

`define clk_period module pll_tb; //source define

reg areset;

reg Clk; //probe define

wire c0;

wire c1;

wire c2;

wire locked; //instant user module pll pll(

.rst(areset),

.refclk(Clk),

.outclk_0(c0),

.outclk_1(c1),

.outclk_2(c2),

.locked(locked)

);

//generater clock

initial Clk = ;

always #(`clk_period/)Clk = ~Clk; initial begin

areset = 'b1;

#(`clk_period * + );

areset = 'b0;

#(`clk_period * + );

$stop;

end endmodule

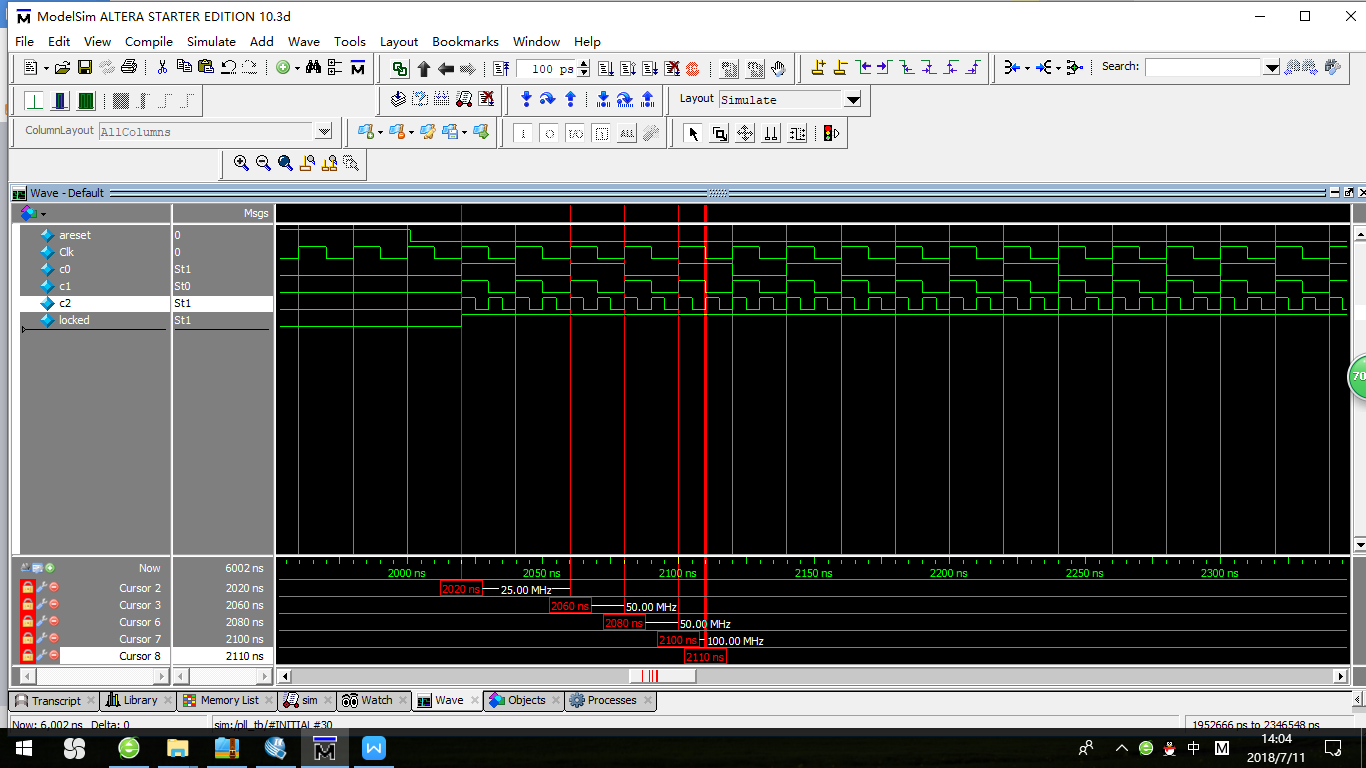

图中可以看出PLL设置成功;

观察led程序

`timescale 1ns/1ps

`define clk_period module PLL_LED_tb; //source define reg Clk;

reg Rst_n; //probe define wire [:]LED; //instant user module

PLL_LED PLL_LED(

.Clk(Clk),

.Rst_n(Rst_n),

.LED(LED)

); defparam PLL_LED.counter0.CNT_MAX = ;

defparam PLL_LED.counter1.CNT_MAX = ;

defparam PLL_LED.counter2.CNT_MAX = ;

defparam PLL_LED.counter3.CNT_MAX = ; //generater clock

initial Clk = ;

always #(`clk_period/)Clk = ~Clk; initial begin

Rst_n = 'b0;

#(`clk_period * + );

Rst_n = 'b1;

#(`clk_period * );

$stop;

end endmodule

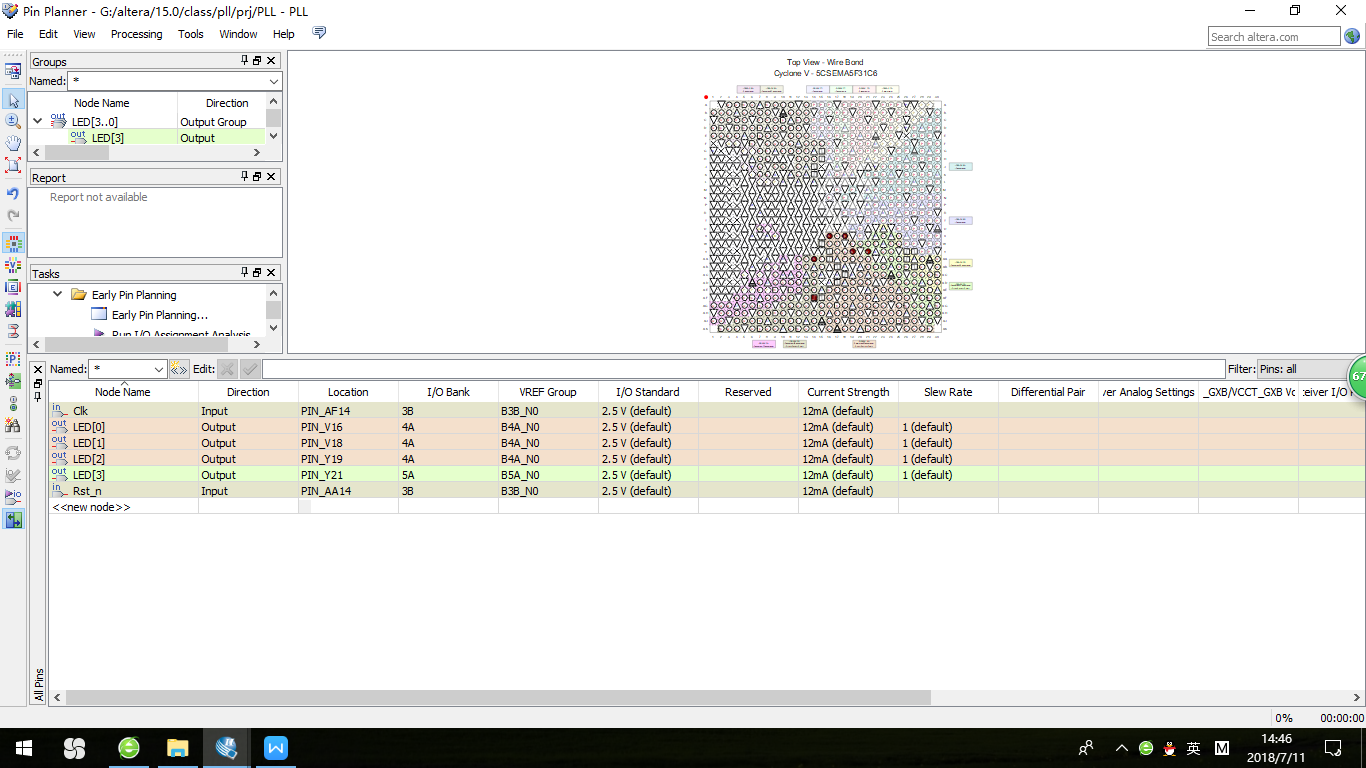

分配引脚

锁相环相关知识可参考博客:

具体讲解:

http://blog.sina.com.cn/s/blog_7656589b01016cfz.html

https://wenku.baidu.com/view/c404cfdbbceb19e8b9f6ba35.html

PLL的更多相关文章

- [Xilinx]Modelsim独立仿真Vivado生成的PLL核

EDA Tools: 1.Vivado 2015.1(64-bit) 2.Modelsim SE-64 10.1c Time: 2016.05.26 ------------------------- ...

- [Altera]PLL仿真

EDA Tools: 1.Quartus II 13.1(64-bit) 2.Modelsim SE-64 10.1c Time: 2016.05.05 ----------------------- ...

- PLL失锁

2016-07-05 现象:在低温(-30度以下)下,射频锁定信号出现周(大约20ms)期性高低电平的变化,由于MCU检测一次需要的时间很长(大于500ms), 大概总是检测不到失锁状态,所以不会出现 ...

- pll及其modesim仿真

100mhz输入时钟,pll层40mhz和200zhm 进入quartus,建立工程,新建图形文件,导入pll模块,设定pll相关参数. 完成pll模块的建立,并生成pll.v文件 建立modes ...

- Quartus 软件的使用之PLL的使用

练习使用Altera FPGA 内的 PLL IP核: 思路:将clk_50M倍频到clk_100M,然后观察100M时钟. 1.生成PLL的核例化文件,然后调用. 点击NEXT之后,等一会会跳出如下 ...

- clock gating and PLL

一个gating的clock是指:clock network除了包含inverter和buffer外,还有其他logic. PrimeTime会自动的对gating input进行setup和hold ...

- Form_通过Custom.pll新增菜单项(案例)

2014-05-31 Created By BaoXinjian

- 58.xilinx原语DCM,PLL的使用

DCM_BASE 基本数字时钟管理模块的缩写,是相伴和频率可配置的数字锁相环电路,常用于FPGA系统中复杂的时钟管理.如需要频率和相位动态配置,则可以选用DCM_ADV原语,如需要相位动态偏移,可使用 ...

- 52.ISE中的PLL时钟输入

在manaul mode中选择PLL PLL的输入时钟可以是全局时钟,也可以是普通IO引脚. 1.PLL的输入时钟是全局时钟的情况. pll_xx pll_xx ( .clkin ( clkin ), ...

- xilinx FPGA普通IO作PLL时钟输入

本帖转自于 :http://www.cnblogs.com/jamesnt/p/3535073.html 在xilinx ZC7020的片子上做的实验; [结论] 普通IO不能直接作PLL的时钟输入, ...

随机推荐

- 获取WEB图片

public string GetJpgFile(string strFileServerPath ,string strReportDir) { string strPath = "&qu ...

- day5 字典 dict

数据类型划分:可变数据类型,不可变数据类型不可变数据类型:元组,数字,布尔,str, == 可哈希可变数据类型:list , dict, set == 不可哈希dict的 key 必须是不可变数据类型 ...

- 字符串问题----去掉字符串中连续出现K个0的子串

去掉字符串中连续出现K个0的子串 给定一个字符串str,和一个整数k, 如果str中正好有连续K 个'0'字符出现,把连续的 k 个 '0'去掉,返回处理后的子串. [解题思路] 1. 定义两个变量, ...

- LeetCode 852. 山脉数组的峰顶索引 (二分)

题目链接:https://leetcode-cn.com/problems/peak-index-in-a-mountain-array/ 我们把符合下列属性的数组 A 称作山脉: A.length ...

- Android中的内存管理机制以及正确的使用方式

概述 从操作系统的角度来说,内存就是一块数据存储区域,属于可被操作系统调度的资源.现代多任务(进程)的操作系统中,内存管理尤为重要,操作系统需要为每一个进程合理的分配内存资源,所以可以从两方面来理解操 ...

- Django models 关联(一对多,多对多,一对一)

参考:https://blog.csdn.net/houyanhua1/article/details/84953388

- Codeforces 1304F2 Animal Observation (hard version) 代码(dp滑动窗口线段树区间更新优化)

https://codeforces.com/contest/1304/problem/F2 #include<bits/stdc++.h> using namespace std; ; ...

- jQuery---弹幕效果

弹幕效果 <!doctype html> <html> <head> <meta charset="utf-8"> <titl ...

- npm vs yarn

npm yarn npm install yarn npm install react --save yarn add react npm uninstall react --save yarn re ...

- R语言函数化编程笔记1

R语言函数化编程笔记1 notes:有一个不错的网站叫做stack overflow,有问题可以从上面找或者搜索答案,会有大佬相助. 在github上面可以找到很多R的扩展包,如果自己额修改被接受,那 ...