Verilog 奇数分频

代码:

module odd_div( );

parameter DIV_PARA = ; //分频系数,3即3分频

parameter DIV_PARA_2 = DIV_PARA >> ;

reg clk, rstn, clk_div_pos, clk_div_neg;

wire clk_div_out;

reg [:] cnt; initial begin

clk <= ;

rstn <= ;

# rstn <= ;

end always begin

# clk <= ;

# clk <= ;

end // 计数循环

always@(posedge clk or negedge rstn) begin

if (!rstn) begin

cnt <= 'd0;

end

else

if (cnt < (DIV_PARA-))

cnt <= cnt + ;

else

cnt <= ;

end

// 上升沿触发

always@(posedge clk or negedge rstn) begin

if (!rstn) begin

clk_div_pos <= ;

end

else begin

if (cnt < DIV_PARA_2)

clk_div_pos <= ;

else

clk_div_pos <= ;

end

end

// 下降沿触发

always@(negedge clk or negedge rstn) begin

if (!rstn) begin

clk_div_neg <= ;

end

else begin

if (cnt < DIV_PARA_2)

clk_div_neg <= ;

else

clk_div_neg <= ;

end

end

// 生成分频信号

assign clk_div_out = clk_div_pos | clk_div_neg; endmodule

这个代码比较简单,而且为了仿真方便,将dut和bench写在一个模块了。。。。

代码设计思路来自这个帖子 https://blog.csdn.net/lt66ds/article/details/10035187

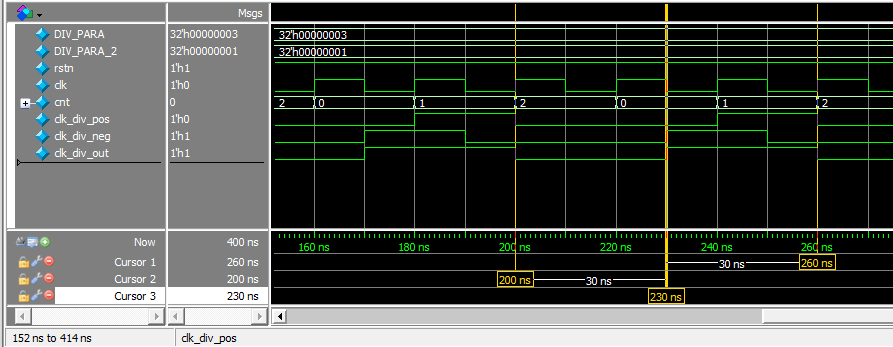

DIV_PARA参数设置分频系数,MoldelSIm仿真图如下

3分频:

DIV_PARA = 3

原时钟周期20ns,分频后的时钟周期为60ns,占空比为50%

5分频:

DIV_PARA = 5

原时钟周期20ns,分频后的时钟周期为100ns,占空比为50%

Verilog 奇数分频的更多相关文章

- verilog 奇数分频设计

module tw(clk,k_or,k1,k2); input clk; output k_or,k1,k2; reg [2:0] c1,c2; reg m1,m2; initial begin c ...

- FPGA三分频,五分频,奇数分频

我们在做FPGA设计时,有时会用到时钟频率奇数分频的频率,例如笔者FPGA的晶振为50M,当我们需要10M的时钟时,一种方式可以使用DCM或PLL获取,系统会内部分频到10M,但其实VERILOG内部 ...

- FPGA奇数分频

在FPGA设计中,分频是很常用的一个基本功能,一般来说,如果需要偶数分频即2次幂的整数倍,这个就很简单了,如2.4.8.16.32.64等这些以2的整数倍的. 这里说的是奇数倍分频,如时钟是100MH ...

- verilog实现奇数倍分频

在学习FPGA的过程中,最简单最基本的实验应该就是分频器了, 同时分频器也是FPGA设计中使用频率非常高的基本设计之一, 尽管在芯片厂家提供的IDE中集成了锁相环IP, 如altera 的PLL,Xi ...

- 【Verilog】verilog实现奇数次分频

实现占空比为50%的N倍奇数分频:首先进行上升沿触发进行模N计数,计数到某一个值时进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%的奇数n分频时钟.再者 同时进行下降沿触发的 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

- 基于verilog的分频器设计(奇偶分频原理及其电路实现:上)

在一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率太高)进行分频.分频器主要分为奇数分频,偶数分频,半整数分频和小数分频,在对时钟要求不是很严格的FPGA系统中 ...

- verilog分频模块设计

verilog设计: 分频器的设计: 分频器就是将一个时钟源的频率降低的过程(可以通过观察分频之后周期中包含几个原时钟周期来看是几分频),分频分为基数分频也分为偶数分频, 偶数分频的代码如下:(其中就 ...

- Verilog 任意(奇数/偶数)分频器

参加过一次笔试,让实现3分频,楼主当时是懵逼的,脑子里只知道同时利用上升沿和下降沿,本来写对了,慌张面试,脑子不管用了,(因为是手写,只能用脑子仿真)后来又给改错了,捂脸... 还是逻辑不清晰,现在自 ...

随机推荐

- 在线制作GIF图片项目愿景与范围

在线制作GIF图片项目愿景与范围 a. 业务需求 a.1 背景 在当今社会中,随着聊天软件和web网站的普及,原创动画制作越来越吸引人们的眼球,一个好的动态图片,可能就会为你的网站或本人赢得更多人的认 ...

- mocha、chai、sinon和istanbul实现100%单元测试覆盖率

敏捷软件开发中,最重要实践的就是测试驱动开发,在单元测试层面,我们试着实现一个重要的指标就是测试覆盖率.测试覆盖率衡量我们的代码是否已经全部被测试到了. 但是指标本身不是目的,借助测试覆盖率检查,我们 ...

- Prometheus Node_exporter metrics 之 Basic CPU / Mem / Disk Info

Basic CPU / Mem / Disk Info 1. CPU Cores 物理 CPU 的核数 cat /proc/cpuinfo| grep "cpu cores"| u ...

- Java简单的数据库连接

package test.postgre; import java.sql.Connection; import java.sql.DriverManager; import java.sql.Res ...

- Sqlite 语句 记录

//string ComId = "select Max(ComId) AS ComId from Card order by ComId ";//位数一样可以直接MAx stri ...

- 退出全屏监听ESC事件

fullscreenchange事件 fullscreenchange:当窗口大小改变时触发 isFullscreen:全局变量 window.addEventListener("fulls ...

- controller断点进入失败:包路径问题

controller 接受前端参数的方法(前端要有传值给controller的方法,后台要有接收值得方法) 1.@RequestParam 接收表单参数 2.@RequestBody 接收json字符 ...

- 一、HTML概述 二、web相关的概念 三、HTML的常用标签

一.HTML概述###<1>概念 HTML:Hypertext Markup Language,超文本 标记语言,用来描述网页的一种语言. 非编程语言,由浏览器直接解释运行. ###< ...

- Mina使用总结(三)MinaClient

简单的Mina客户端代码MinaSimpleClient.java: package com.bypay.mina.client; import java.net.InetSocketAddress; ...

- MySQL IFNULL基本用法

MySQL IFNULL函数是MySQL控制流函数之一,它接受两个参数,如果不是NULL,则返回第一个参数. 否则,IFNULL函数返回第二个参数. 两个参数可以是文字值或表达式. 以下说明了IFNU ...