FPGA奇数分频

在FPGA设计中,分频是很常用的一个基本功能,一般来说,如果需要偶数分频即2次幂的整数倍,这个就很简单了,如2、4、8、16、32、64等这些以2的整数倍的。

这里说的是奇数倍分频,如时钟是100MHz,需要一个20MHz的输出频率,那么就需要5次分频,那么问题来了,安装2分频的方法:100/2=50,50/2=25,只能等到一个25MHz的频率,显然这种方法是不可行的,那么就需要奇数分频了。

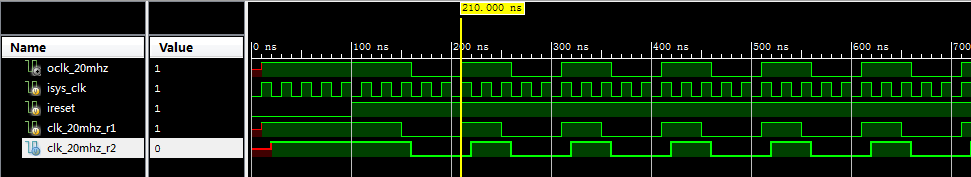

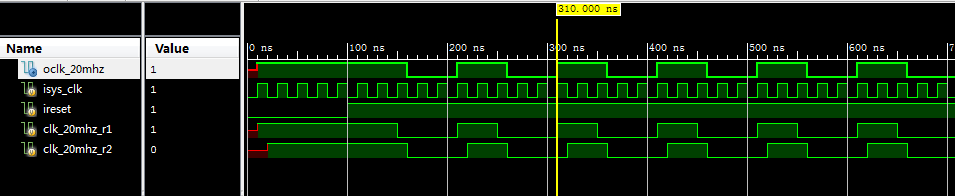

1、做个模为5的计数器,

2、做两个个信号a,b。在模1的计数下,前2个周期信号a为高电平,后3个周期信号a为低电平。

3、用时钟的下降沿将信号a延时一个节拍,得到信号b。

4、信号a或b运算输出时钟,即得到占空比为1:1的5分频20MHz时钟频率。

程序中a为clk_20mhz_r1,b为clk_20mhz_r2。

module system_clk

(

input isys_clk,

input ireset,

output oclk_20mhz

);

reg [2:0] cnt_20mhz;

reg clk_20mhz_r1;

reg clk_20mhz_r2;

always @(posedge isys_clk or negedge ireset)

begin

if(!ireset)

cnt_20mhz <= 3'd0;

else if( cnt_20mhz >= 3'd4)

cnt_20mhz <= 3'd0;

else

cnt_20mhz <= cnt_20mhz + 1'b1;

end

always @(posedge isys_clk )

begin

if( cnt_20mhz < 3'd2)

clk_20mhz_r1 <= 1'b1;

else

clk_20mhz_r1 <= 1'b0;

end

always @(negedge isys_clk)

begin

clk_20mhz_r2 <= clk_20mhz_r1;

end

assign oclk_20mhz = clk_20mhz_r1 | clk_20mhz_r2;

endmodule

FPGA奇数分频的更多相关文章

- FPGA三分频,五分频,奇数分频

我们在做FPGA设计时,有时会用到时钟频率奇数分频的频率,例如笔者FPGA的晶振为50M,当我们需要10M的时钟时,一种方式可以使用DCM或PLL获取,系统会内部分频到10M,但其实VERILOG内部 ...

- FPGA时钟分频(转)

http://www.cnblogs.com/fpga/archive/2009/10/24/1589318.html 占空比为50%的分频 偶数分频比较简单 比如N分频,那么计数到N/2-1,然后时 ...

- verilog 奇数分频设计

module tw(clk,k_or,k1,k2); input clk; output k_or,k1,k2; reg [2:0] c1,c2; reg m1,m2; initial begin c ...

- Verilog 奇数分频

代码: module odd_div( ); ; //分频系数,3即3分频 ; reg clk, rstn, clk_div_pos, clk_div_neg; wire clk_div_out; : ...

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- verilog实现奇数倍分频

在学习FPGA的过程中,最简单最基本的实验应该就是分频器了, 同时分频器也是FPGA设计中使用频率非常高的基本设计之一, 尽管在芯片厂家提供的IDE中集成了锁相环IP, 如altera 的PLL,Xi ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- 【Verilog】verilog实现奇数次分频

实现占空比为50%的N倍奇数分频:首先进行上升沿触发进行模N计数,计数到某一个值时进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%的奇数n分频时钟.再者 同时进行下降沿触发的 ...

- 基于verilog的分频器设计(奇偶分频原理及其电路实现:上)

在一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率太高)进行分频.分频器主要分为奇数分频,偶数分频,半整数分频和小数分频,在对时钟要求不是很严格的FPGA系统中 ...

随机推荐

- Fireeye火眼公司发布报告,评论中国网络间谍活动

2013年10月2日,Fireeye火眼公司发布报告,评论中国网络间谍活动-Fireeye(美 国火眼公司)发布报告<世界网络大战:理解网络攻击背后的国家意图>(World War C: ...

- DDOS的攻击原理和防护指南(转)

DDOS的攻击原理和防护指南 作者:冰盾防火墙 网站:www.bingdun.com 日期:2008-01-07 我们现在来分析DDOS的攻击原理. 首先,DDOS是英文Distribut ...

- phonegap 框架详解

首先, 来看一下phonegap 初始化流程以及Native 与 JS 交互流程图. 说明:socket server模式下, phonegap.js 源码实现的采用1 毫秒执行一次XHR请求, 当 ...

- webApp--cordova 系列1

1.在node,npm 可用的前提下 npm install -g cordova 大约10分钟后装完,cmd中输入cordova -v 验证是否安装成功 2.cordova项目打包是用ant完成, ...

- HDU 4768 (二分区间---涨姿势)

题意:告诉n组A,B,C,按照A + k * C生成等差数列,问这n组数列中哪个数字出现了奇数次以及出现了几次,题目保证最多只会出现一个这种数字. 分析:读完题并没有思路,后来知道是二分区间,枚举是哪 ...

- logback配置错误邮件发送

配置logback发送error级别日志到指定邮箱 需要导入jar包:janino.jar <property name="smtpHost" value="smt ...

- Glossary

Glossary term terminology Certificate authority A norganization that authorizes a certificate. Certi ...

- 数据库使用fmdb

#import "SQLdataManger.h" #import "FMDatabaseAdditions.h" static SQLdataManger * ...

- 国内较快的maven镜像

原文网址:http://www.cnblogs.com/dingyingsi/p/3856456.html 国内连接maven官方的仓库更新依赖库,网速一般很慢,收集一些国内快速的maven仓库镜像以 ...

- div弹出层的效果带关闭按钮

下面我做的这个是个进度条的弹出层 <style type="text/css"> #tuxiang { width: 57px; } /*div弹出框的css*/ .t ...