如何保证FPGA PCIe唤醒能满足PC的100ms 的时间要求(Autonomous Mode)?

原创By DeeZeng [ Intel FPGA笔记 ]

PC 需要PCIe设备在 100ms 内启动,这样PC 才能扫描到PCIe 设备。对于 FPGA PCIe 板卡,同样也需要满足这个时间要求。

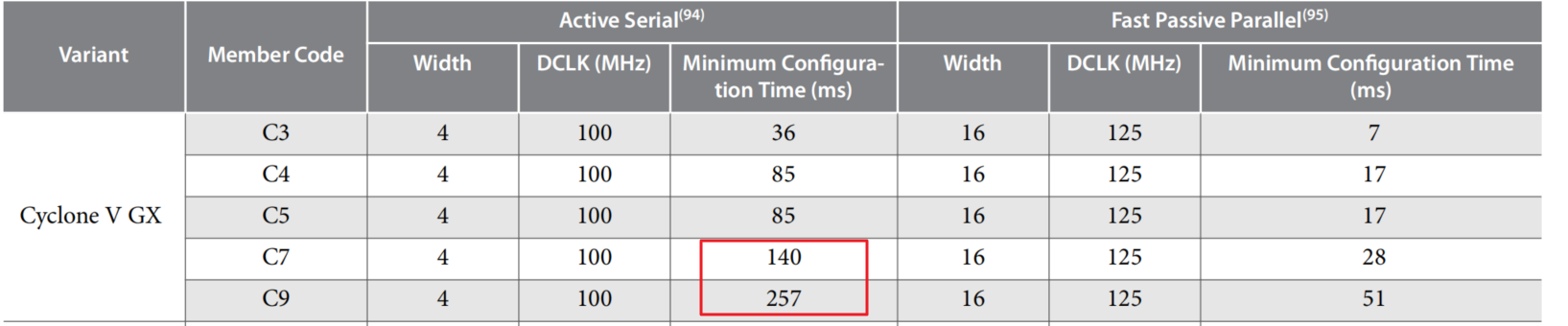

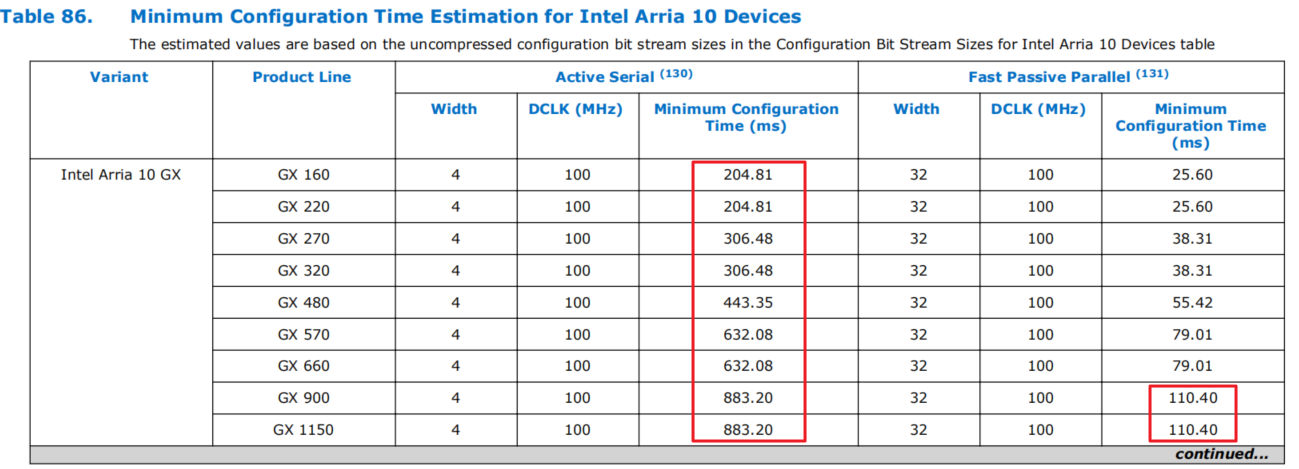

Intel FPGA系列是基于sram的,也就是掉电丢失,所以会需要配置器件。配置模式有很多种,以我们常见的 ASx4 和 FPP为例:

1. ASx4 :只需要一颗 EPCS/PECQ 即可配置

2. FPP : 需要一个额外外部Host 用来搬移 配置数据,由于是并行 x8 x16 x32,配置时间会少很多。

如下抽出两张 Cyclone V 和 Arria 10 的 AS FPP 配置时间差异

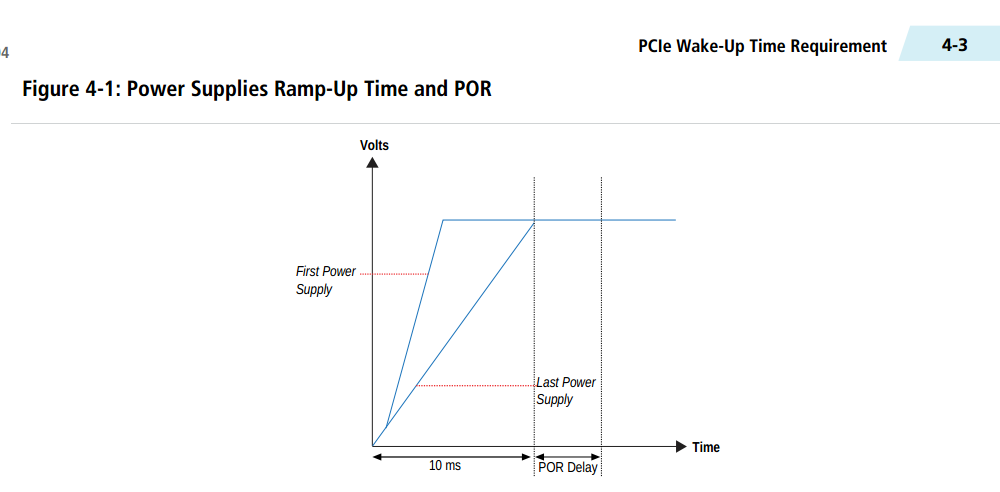

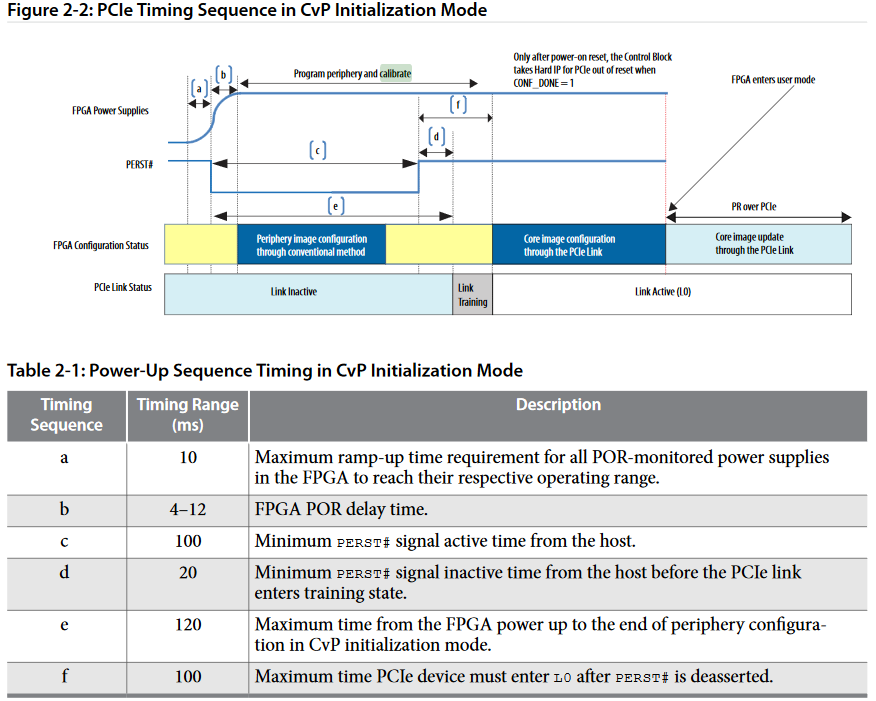

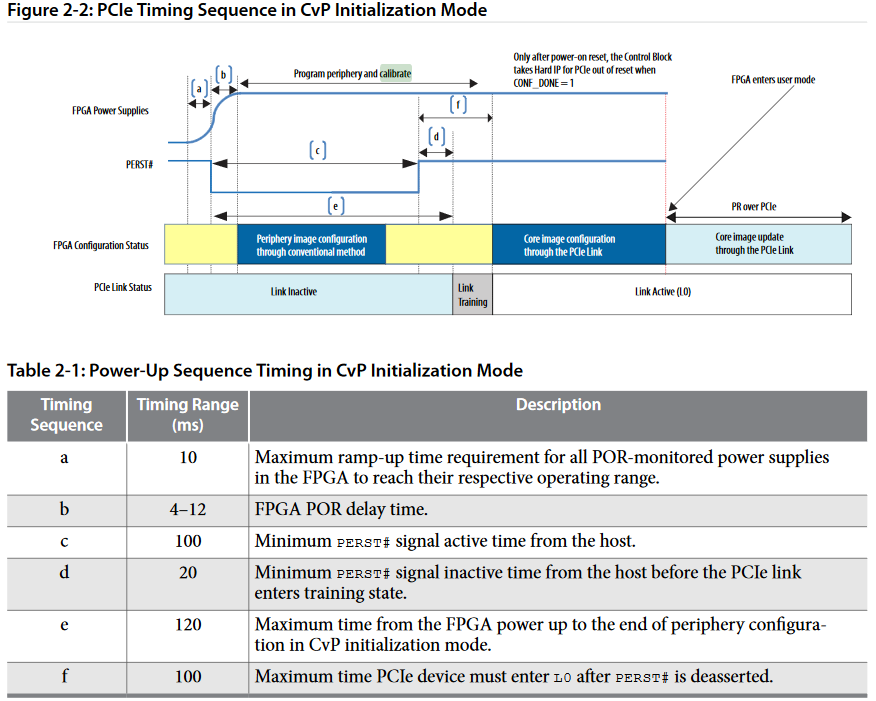

PCIe 100ms 或FPGA 120 ms 的时间(请具体分析之后给出的 Figure 2-2 ,Table 2-1图片),可不单纯包含FPGA configuration Time,还包含Ramp Time ,POR Time等。

减去这两项时间,那FPGA configuration 80 ms 左右的都有点不保险了。

也就是当我们 Cyclone V 逻辑资源大的器件,或Arria10 器件,当使用AS x4模式的时候,PCIe应用会满足不了唤醒时间!

(Arria10的最大两个器件,甚至FPP32时间也满足不了)

而实际硬件设计或板子必须或已经采用 EPCQ方案了(毕竟很多情况只会用一颗EPCQ,而不用FPP的 外部Host+并行Flash)

那如何解决呢?

- 外接供电,先于 Host 开机。 (好吧,这用起来几多麻烦)

- PCIe供电,Host 开机两次。(重启FPGA不需要再配置)

- Autonomous PCIe HIP Mode (注意要器件支持这个功能)

什么是Autonomous PCIe HIP模式?

Autonomous 模式对满足PCIe 100ms 唤醒时间非常有用。Intel FPGA设备会先接收periphery image,然后再接收 Core image.

配置完Core image 后,FPGA进入user mode. 在Autonomous HIP 模式下,PCIe Hard IP 在periphery image配置完后就能工作,

完成Link Training 后,PCIe Hard IP 就能响应 host, 从而减少唤醒时间。 而不用等到 Core image 配置完进入user mode才开始。

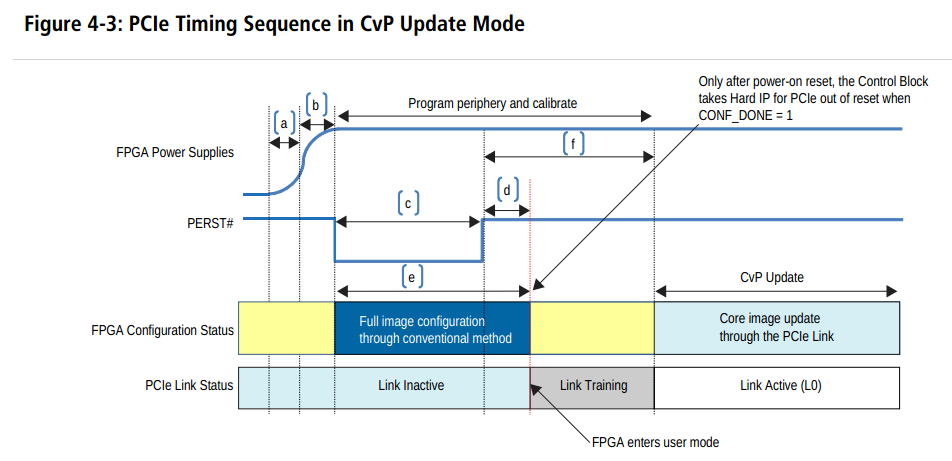

Autonomous PCIe HIP Mode 和 CvP 的模式是类似的,如下以CVP的两张图类比说明Autonomous PCIe HIP Mode 与否的差异。

PCIe Active的 时间 = a(ramp time) + b (POR) + Program and calibrate

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_a10_cvp_prop.pdf

1. Autonomous PCIe HIP Mode : 只需 program Periphery image ,Hard PCIe就起来了。

2. 非Autonomous PCIe HIP Mode : 需要Program Full image ,Hard PCIe才起来。

所以使能Autonomous PCIe HIP Mode 可以减少 (Full image - Periphery image)数量的Config bits,大大缩短时间。

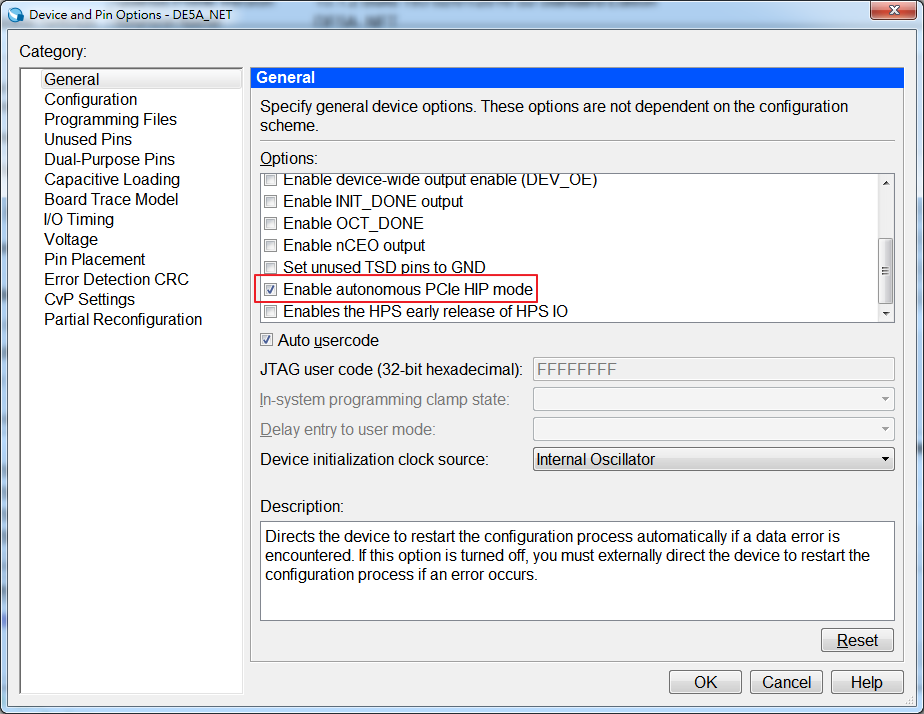

这么有用,那如何设置 Autonomous 模式呢?简单,在 Quartus 工程中设置勾选一下即可。

Cyclone V,Arria V 和 Stratix V 以及之后出来的 Arria 10 ,Stratix 10 等 都支持 autonomous PCIe HIP Mode.

注意: 1. PCIe Hard IP。 2. 支持这个功能的器件。

这样开机无法找到PCIe,重启才能找到的案例。打开这个模式之后,第一次开机就能直接找到PCIe啦。

What? 担心打开了Autonomous PCIe HIP Mode还是无法满足 PCIe的唤醒100ms时间要求?

那我们来进行一次具体计算,看如何计算这些时间

以 Arria10 1150的器件,使用AS x4 来计算(其他系列计算类似)

PCIe Active的时间 = a(ramp time) + b (POR) + Program and calibrate

1. Ramp Time: Ramp Time 这是FPGA开发板 Power 电路决定的

假设10ms

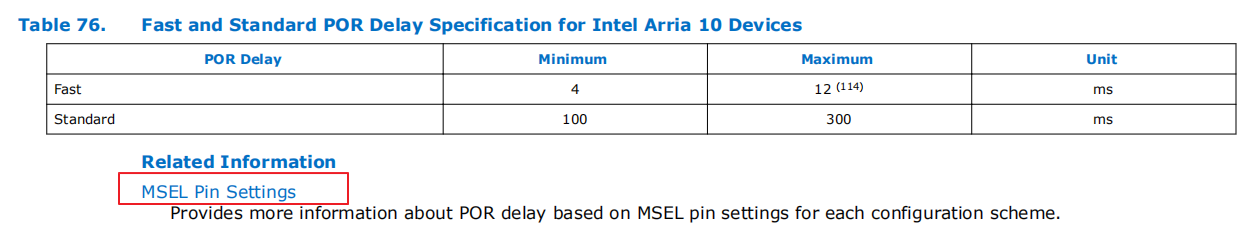

2. POR delay: 这个delay是,POR电路监控的所有Power都起来了,然后delay一个时间用以保证,FPGA准备好被配置。

可以看到 Fast POR 和 Standard POR 是有很大差异的,我们必须设置MSEL,将POR切到 Fast

这里算 fast 的 12ms

3. Program and calibrate

3.1 Program periphery image

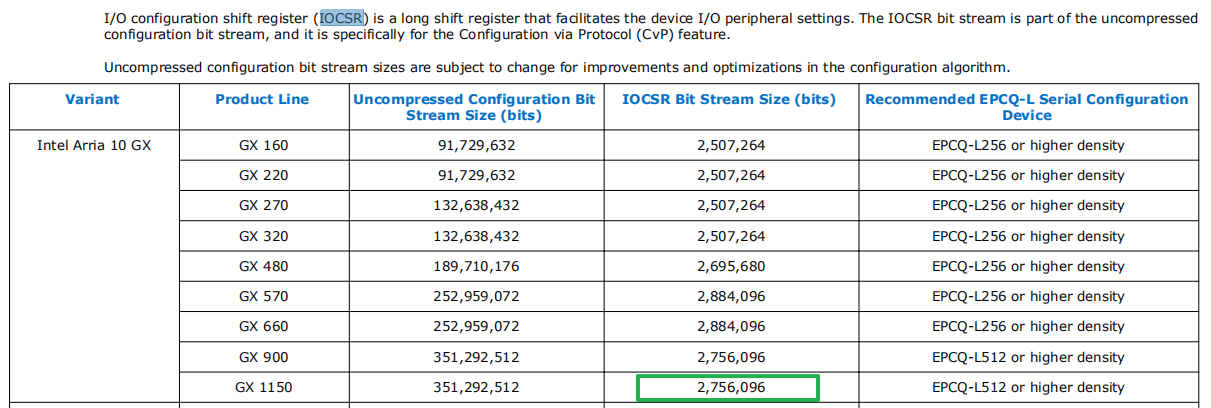

为计算配置periphery image的时间:

这里 Configuration File size 我们用 periphery image : Datasheet中CvP的IOCSR数据 2756096

Number of data line 用 AS x4 的 4

DCLK 用 AS 的 100MHz

config time = 2756096/4* (1/100MHz) = 6.9 ms (远小于 full image 的 800+ ms)

3.2 Calibrate

Transceiver calibration begins with the bottom PCIe IP core on eachside of the device. Consequently, this IP core has a faster wake up time

这个时间在 A10 是有一个nios硬核ip 会进行calibration,从bottom的开始。时间花费应该不多。

所以打开 Autonomous Mode总时间为: 10 + 12 + 6.7 + 少量Calibrate时间 ≈ 30ms ,很简单就满足PCIe唤醒时间要求。

重复一下这张图: 我们Arria10 1150K,用ASx4的EPCQ config periphery image 都只需要 7ms 不到,那这张图的timing应该很好满足了。

不过硬件的 Ramp Time应该是影响的,如果超了10ms (别超),也许就是 和 ramp+POR+config 的时间加起来和 120ms 对比了

是否会算了呢?

按上面的计算,A10 最大器件用ASx4 也没问题。

这样 Arria10 以下28nm以上的器件直接打开 Autonomous PCIe HIP Mode 就好哟。

如何保证FPGA PCIe唤醒能满足PC的100ms 的时间要求(Autonomous Mode)?的更多相关文章

- 推荐 的FPGA设计经验(3) 物理实现和时间闭环优化

Optimizing Physical Implementation and Timing Closure Planning Physical Implementation When planning ...

- HC-08 BLE资料

1.1 特点简介 HC-08蓝牙串口通信模块是新一代的基于Bluetooth Specification V4.0 BLE蓝牙协议的数传模块.无线工作频段为 2.4GHz ISM,调制方式是 GFSK ...

- PC和FPGA间的串口通信实现

应用笔记 V1.0 2015/03/26 PC和FPGA间的串口通信实现 概述 本文将介绍PC和FPGA间的串口通信实现的基本思路和Verilog代码,对于通信而言,收发双方都要有相应的控制. ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- 基于WDF的PCI/PCIe接口卡Windows驱动程序(4)- 驱动程序代码(源文件)

原文出处:http://www.cnblogs.com/jacklu/p/4687325.html 本篇文章将对PCIe驱动程序的源文件代码作详细解释与说明.整个WDF驱动程序工程共包含4个头文件(已 ...

- PCIE_DMA实例四:xapp1052在Xilinx 7系列(KC705/VC709)FPGA上的移植

PCIE_DMA实例四:xapp1052在Xilinx 7系列(KC705/VC709)FPGA上的移植 一:前言 这段时间有个朋友加微信请求帮忙调试一块PCIe采集卡.该采集卡使用xilinx xc ...

- FPGA开发流程

需求说明:Verilog设计 内容 :FPGA开发基本流程及注意事项 来自 :时间的诗 原文来自:http://www.dzsc.com/data/2015-3-16/1080 ...

- 基于FPGA Manager的Zynq PL程序写入方案

本文主要描述了如何在Linux系统启动以后,在线将bitstream文件更新到ZYNQ PL的过程及方法.相关内容主要译自xilinx-wiki,其中官网给出了两种方法,分别为Device Tree ...

- FPGA资源平民化的新晋- F9 技术解析

FPGA (现场可编程门阵列)由于其硬件并行加速能力和可编程特性,在传统通信领域和IC设计领域大放异彩.一路走来,FPGA并非一个新兴的硬件器件,由于其开发门槛过高,硬件加速算法的发布和部署保护要求非 ...

随机推荐

- HDU 4059:The Boss on Mars(数学公式+容斥原理)

http://acm.hdu.edu.cn/showproblem.php?pid=4059 题意:给出一个n,求1~n里面与n互质的数的四次方的和是多少. 思路:不知道1~n的每个数的四次方的求和公 ...

- 自定义docker镜像

1.拉去centos当作基础镜像 2.重要!!!必须使用超级权限启动: docker run --privileged -ti --name latestCenos centos /usr/sbin ...

- 关于ArrayList的扩容机制

关于ArrayList的扩容机制 ArrayList作为List接口常用的一个实现类,其底层数据接口由数组实现,可以保证O(1) 复杂度的随机查找, 在增删效率上不如LinkedList,但是在查询效 ...

- 微信小程序 CSS border-radius元素 overflow:hidden失效问题 iPhone ios 苹果兼容问题 伪类元素

同事找我解决一个问题 说安卓圆角没问题 苹果上失效了 我一看 其实就是没做兼容上图给你们看看 有没有看出来 其实就是父级设置圆角属性失效 父元素使用border-radius和overflow:hid ...

- 使用nexus搭建npm私服

第一步,下载nexus 下载链接: https://pan.baidu.com/s/1GOYi2M3nT4Wcy7JEYmnqdA 提取码: a9hf 第二步,解压缩 我下载的是nexus-3.16. ...

- Bzoj 4582 [Usaco2016 Open] Diamond Collector 题解

4582: [Usaco2016 Open]Diamond Collector Time Limit: 10 Sec Memory Limit: 128 MBSubmit: 204 Solved: ...

- 20131222-Dom省市加载-第二十七天

[1]省市选择 <head> <title></title> <script type="text/javascript"> win ...

- Java编程思想:泛型方法

import java.util.*; public class Test { public static void main(String[] args) { // GenericMethods.t ...

- py+selenium IE 用driver.close()却把两个窗口都关了【已解决】

环境:py3 selenium unittest 测试浏览器:IE10 目标:在单个文件中,有多个用例,执行完A用例,由于打开了新的窗口,必须关闭新的窗口,才不会影响下一条用例的执行. 问题:按例 ...

- TensorFlow笔记-初识

深度学习: 转换编程的思维(和传统的机器学习的编程方式不太一样) 测试链接 TensorFlow的安装 CPU版本: 只支持程序在CPU上计算/运算,默认运行就是CPU上运行 卸载: pip unin ...