07-逻辑仿真工具VCS-Post processing with VCD+ files

逻辑仿真工具-VCS

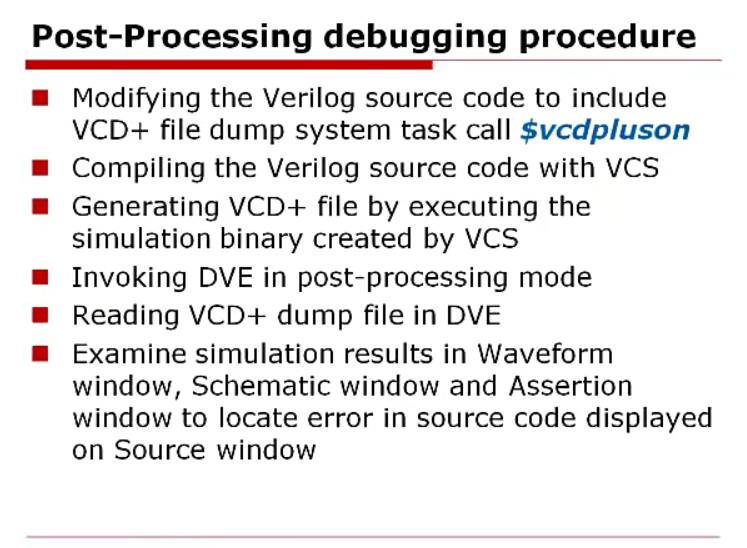

- 编译完成不会产生波形,仿真完成之后,生成波形文件,通过dve产看波形

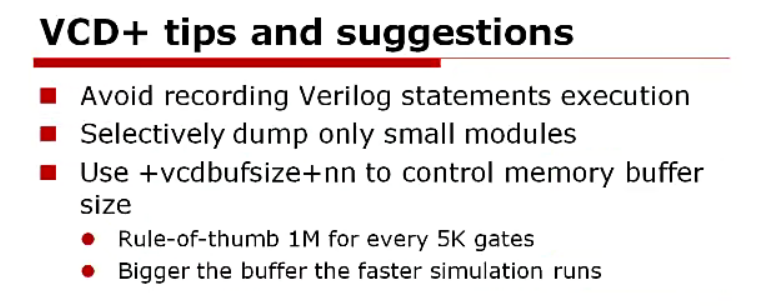

- vcd是波形文件的格式,但是所占的内存比较大,后面出现了vpd(VCD+)波形文件

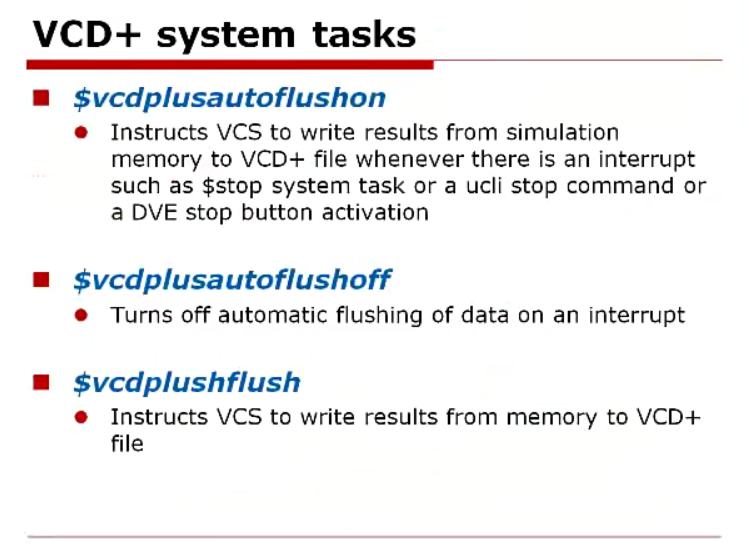

- 将一些系统函数嵌入到源代码中,VCS不会自动保存波形文件

- Dump波形,就是将仿真波形记录下来

1.后处理考虑的因素

- 在设计的初期或者验证平台搭建初期保存波形,随着项目进行就不会保存波形文件

2.什么时候进行post-processing

3.什么是VCD+

- DVE只支持VCD+文件,

4.波形产生函数

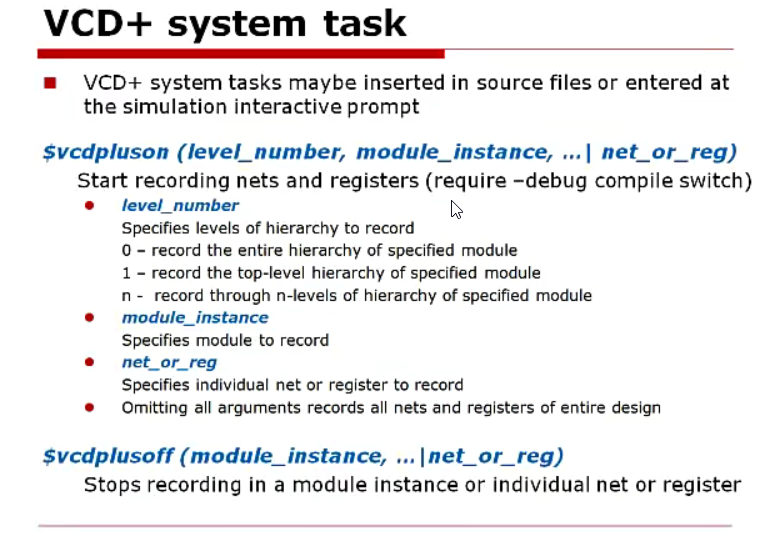

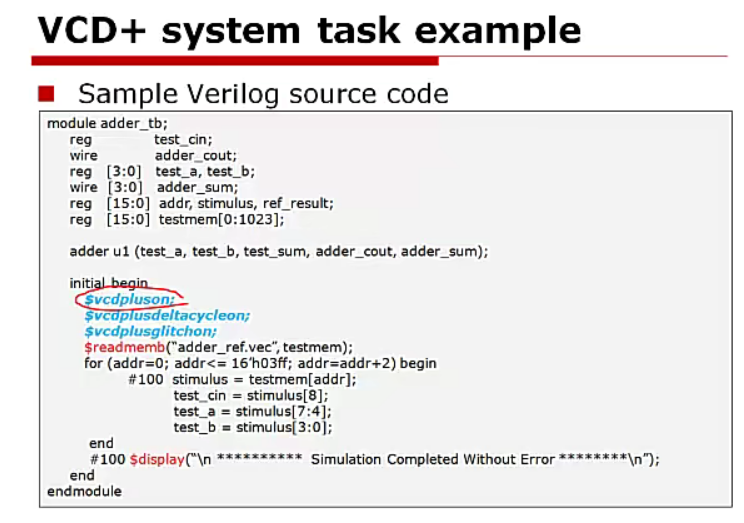

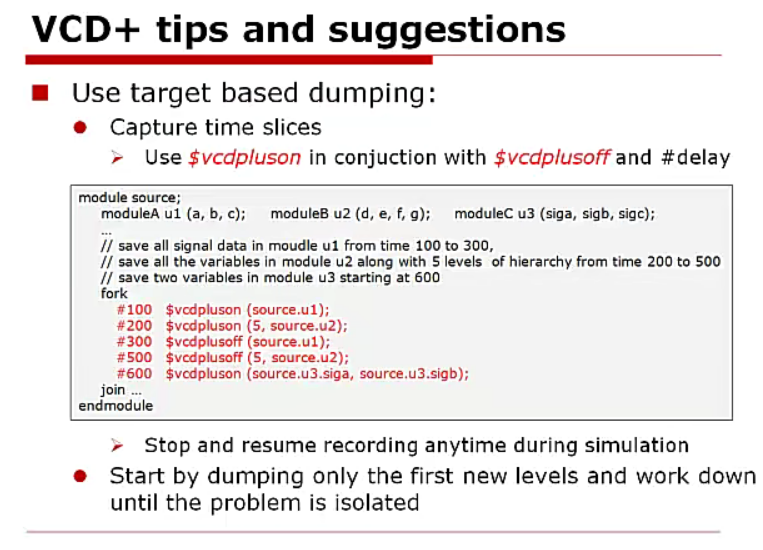

在verilog中代码,嵌入$vcdpluson()函数dump波形

不带参数,将所在的module波形以及包含的子模块的波形都保存

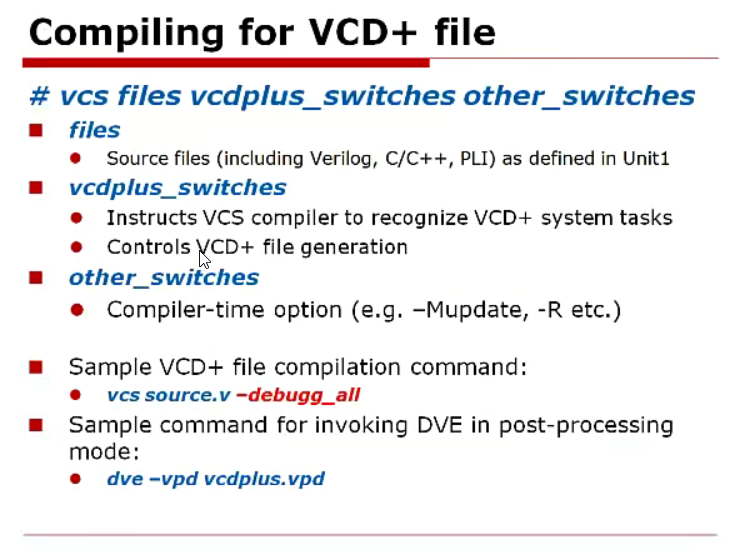

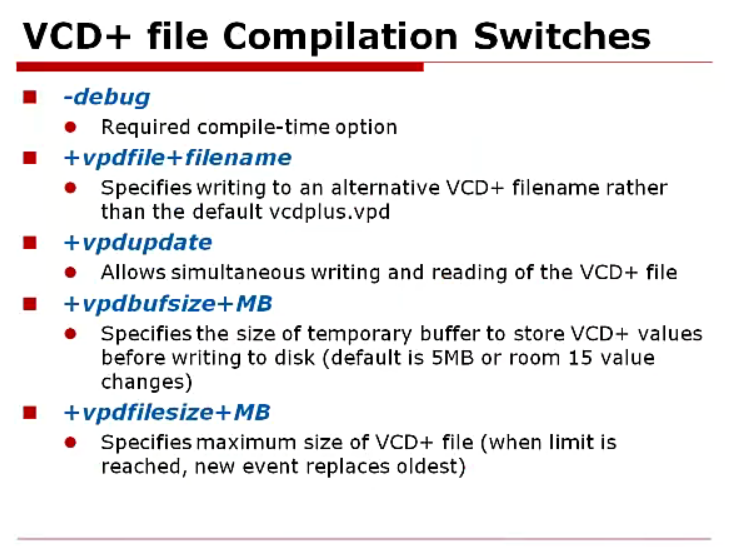

5.编译选项

- +vpdfile+filenames -- 重命名产生的波形文件

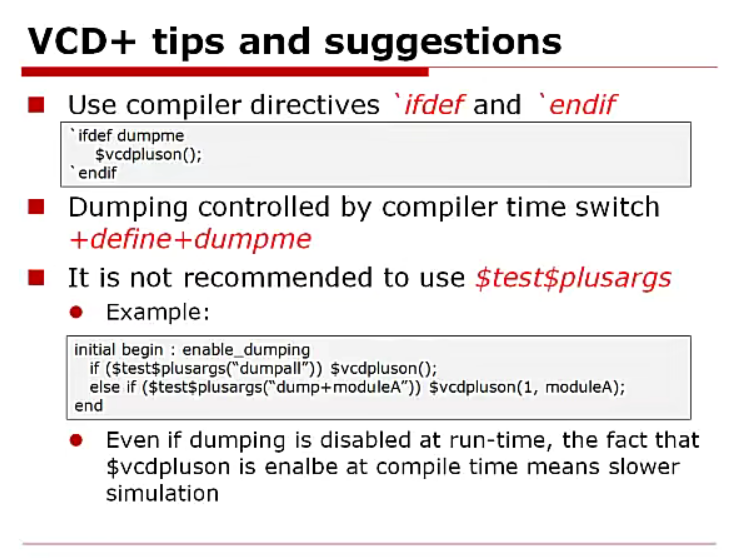

- `ifdef 条件编译

- $values$plusargs

6.使用Makefile进行VCS后处理

Makefile文件

# 产生的二进制可执行文件

OUTPUT = simv_fsm_moore

# 进行宏定义,用于条件编译

ALL_DEFINE = +define+DUMP_VPD

# vpd file name

VPD_NAME = +vpdfile+${OUTPUT}.vpd

# compile command

VCS = vcs -sverilog +v2k -timescale = 1ns/1ns

-debug_all

+vcs+flush+all

${ALL_DEFINE}

${VPD_NAME}

-o ${OUTPUT}

-l compile.log

# simulation command

SIM = ./${OUTPUT}

${VPD_NAME}

-l ${OUTPUT}.log

# start compile

com:

${VCS} -f file_list.f

# start simulation

sim:

${SIM}

#start clean

rm -rf ./csrc *.daidir ./csrc *.log *.vpd *.vdb simv* *.key *race.out*

file_list.f

-timescale = 1ns/1ns

// Macro define

// +define+INC_COUNTER

// Source file

./rtl/fsm_moore.v

//testbench

./tb/fsm_top.v

./tb/hello.c

- make clean -- 删除当前目录下产生的仿真文件

- make com -- 执行编译

- dve & -- 打开图形化界面-->file-->找到xx.vpd文件

- dve -vpd xxx.vpd & -- 打开图形化界面,并且将波形文件加载进去

// verilog

initial begin

`ifdef DUMP_ME

$vcdpluson(); // 不加参数,dump所有波形

$vcdpluson(1,fsm_top); //只记录top层的波形

`endif

end

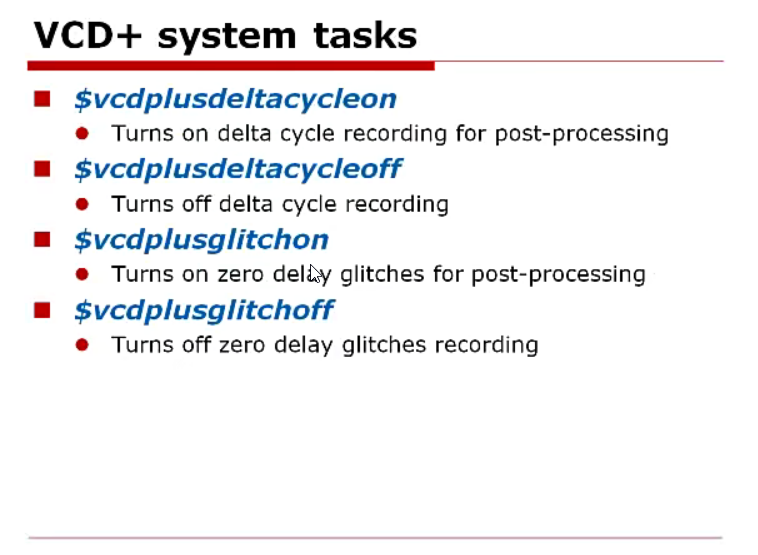

- VCS默认是不会记录数组波形的

- 使用$vcdplusmemon(); dump数组的波形

dump数组的波形

// 在top层中定义了mem

reg [7:0] mem[0:15]

// 使用$readmemh()函数进行初始化

initial begin

$readmemh('./data/src.txt',mem); // 将src.txt文件内容加载到mem中

for(i = 0;i<16;i = i+1) begin

$display("mem[%2d]" = "%8h",i,mem[i]); // 打印数组的内容

end

end

src.txt内容

@0000

7

6

4

7

a

b

@0009

11

12

13

// 使用 $vcdplusmemon() dump数组的波形

initial begin

`ifdef DUMP_ME

$vcdplusmemon();

`endif

end

7.Skills

initial begin是并行的,执行顺序位置,可以通过宏确定执行语句的文件及行数

__FILE__,LINE- 执行仿真之后,由于有上面的宏,并且显示出文件路径以及执行的行数

initial begin

$display("Hello Verilog!",`__FILE__,`__LINE__)

end

initial begin

$display("Hello Verilog!",`__FILE__,`__LINE__)

end

initial begin

$display("Hello Verilog!",`__FILE__,`__LINE__)

end

07-逻辑仿真工具VCS-Post processing with VCD+ files的更多相关文章

- 02-逻辑仿真工具VCS使用

逻辑仿真工具VCS使用 1 Makefile执行VCS仿真 # Makefile for simulating the full_adder.v with the simulator VCS # -- ...

- 01-逻辑仿真工具VCS使用

1 逻辑仿真工具VCS的使用 在书写完成RTL代码之后,确保自己书写的代码和自己想要的逻辑是一致的. VCS是synopsys公司下的的仿真工具. 1 VCS仿真过程 编译-->仿真--> ...

- 027 01 Android 零基础入门 01 Java基础语法 03 Java运算符 07 逻辑“与”运算符

027 01 Android 零基础入门 01 Java基础语法 03 Java运算符 07 逻辑"与"运算符 本文知识点:Java中的逻辑"与"运算符 逻辑运 ...

- VCS 常用命令速查

VCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言.PLI和SDF.VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模 ...

- Windows7WithSP1/TeamFoundationServer2012update4/SQLServer2012

[Info @09:03:33.737] ====================================================================[Info @ ...

- DataStage 七、在DS中使用配置文件分配资源

DataStage序列文章 DataStage 一.安装 DataStage 二.InfoSphere Information Server进程的启动和停止 DataStage 三.配置ODBC Da ...

- DDR3 IP和CIC IP仿真问题解决记录

1.更新vivado的仿真库(data/secureip和verilog和vhdl文件夹)至最新的vivado库和生成IP的版本匹配: 2.vcs编译脚本里面把仿真库地址指向匹配的仿真库版本: 3.v ...

- Windbg调试命令详解

作者:张佩][原文:http://www.yiiyee.cn/Blog] 1. 概述 用户成功安装微软Windows调试工具集后,能够在安装目录下发现四个调试器程序,分别是:cdb.exe.ntsd. ...

- modelsim(3) - tips(zt)

1)如果需要跟踪信号,可以使用dataflow,直观,缺点是后仿太慢! http://www.cnblogs.com/asus119/archive/2011/04/01/2002525.html M ...

- oracle10g在rh6上安装缺少libXtst*的包导致不能出OUI

由于测试需要,今天在linux6.0上装了下oracle10g,确实是知道oracle10g已经不支持redhat5.0以后的版本了,但是根据自己以往在redhat5.0上装oracle的经验就鲁莽下 ...

随机推荐

- Oracle参数文件spfile

spfile:server parameter file. spfile只能通过OEM(oracle enterprise manager)软件或者alter system命令进行修改. spfile ...

- ASR项目实战-架构设计

一般而言,业务诉求作为架构设计的输入. 需求清单 对于语音识别产品而言,需满足的需求,举例如下: 功能需求 文件转写. 长文件转写,时长大于60秒,小于X小时,X可以指定为5. 短文件转写,时长小于6 ...

- 编译安装openssl-1.1.1和openssh-9.4

1.安装 openssl-1.1.1 先处理下opensll的版本,以免编译安装Openssh环境异常: yum remove openssl cd /opt wget https://www.ope ...

- Ubuntu 之 7zip使用

1.安装 sudo apt-get install p7zip 2.压缩 7zr a xxx foldername 3.解压缩 7zr x xxx.7z 4.zip命令压缩文件夹 zip -qr xx ...

- LeetCode 947. 移除最多的同行或同列石头 并查集

传送门 思路 干货太干就不太好理解了,以下会有点话痨( ̄▽ ̄)" 首先题目给了一个二维stones数组,存储每个石子的坐标,因为在同行或者同列的石子最终可以被取到只剩下一个,那么我们将同行同 ...

- VSCode 终端选择文本自动复制

Ctrl + , 打开设置 搜索 copyOnSelection,勾选即可 对应的 settings.json 如下 "terminal.integrated.copyOnSelection ...

- 创建傀儡进程svchost.exe并注入DLL文件(Shellcode)

本文主要利用 SetThreadContext 修改进程中的线程上下文来实现Dll注入(ShellCode). 实现原理 首先,使用 CreateProcess 函数创建svchost.exe进程,并 ...

- 文心一言 VS 讯飞星火 VS chatgpt (49)-- 算法导论6.2 1题

一.参照图6-2的方法,说明 MAX-HEAPIFY(A,3)在数组 A=(27,17,3,16,13,10,1,5,7,12,4,8,9,0)上的操作过程. 文心一言: 下面是 MAX-HEAPIF ...

- 微信小程序卡片

1.1 效果 左右滑动 1.2 代码 <view class="container"> <swiper autoplay interval="4000& ...

- 【鲲鹏 DevKit黑科技揭秘】│如何实现全链路系统问题90%精准诊断?

摘要:DevKit系统诊断工具是鲲鹏性能分析工具的子工具之一,能够针对内存.网络.存储等常见故障和异常,提供精准定位和诊断能力,帮助用户识别出源代码中的问题点,提升程序的可靠性,故障定位准确率高达90 ...