Xilinx XPM使用说明--XPM_MEMORY_SDPRAM

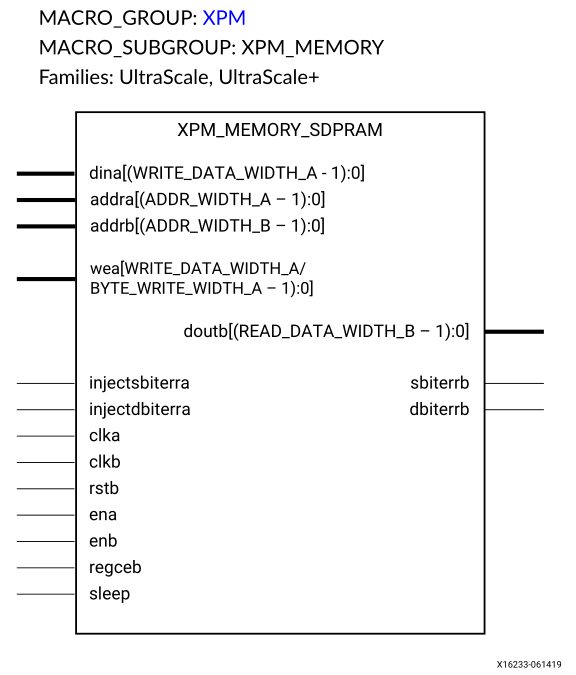

XPM_MEMORY_SDPRAM

参数化宏:简单的双端口RAM

介绍

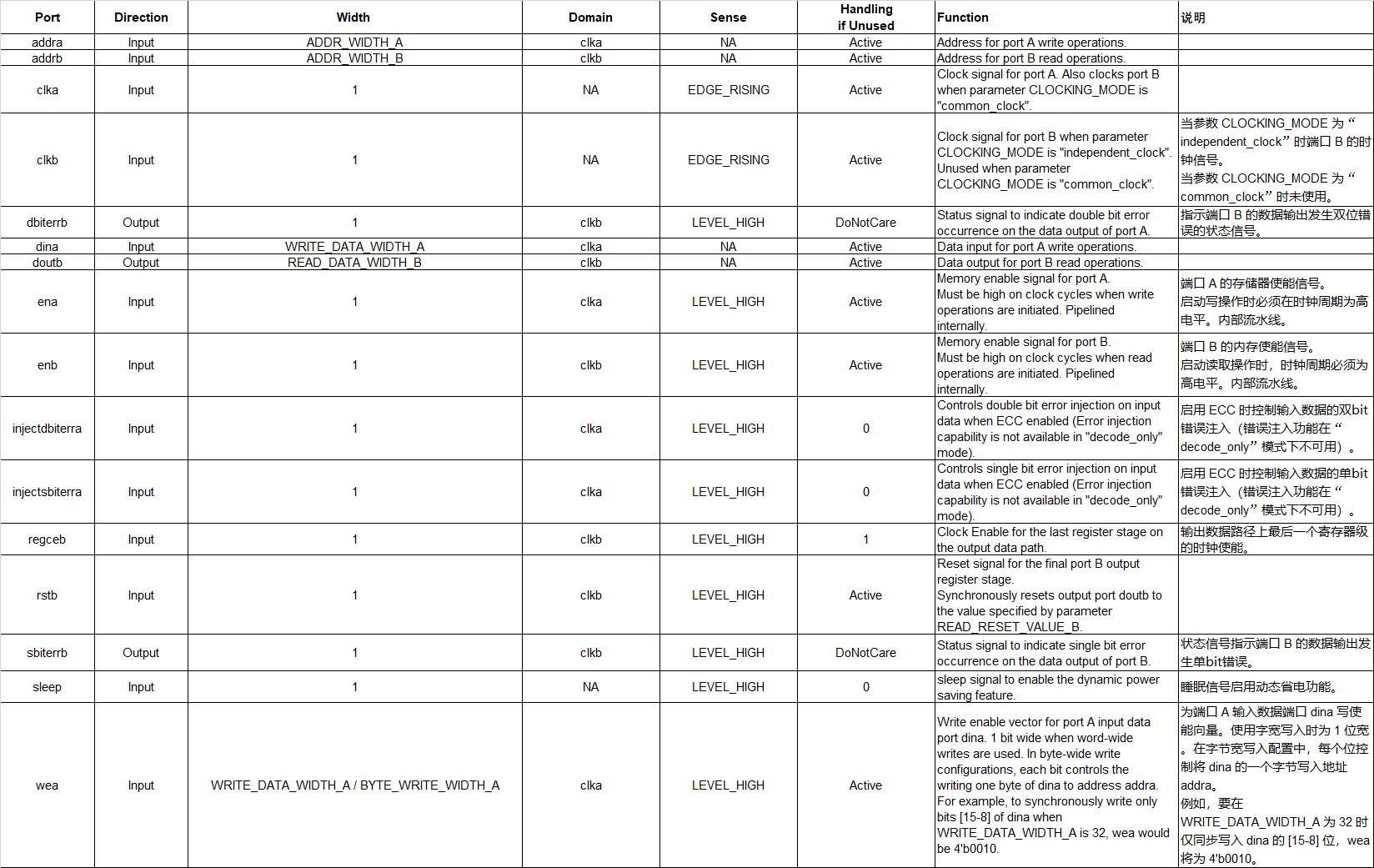

此宏用于实例化简单双端口RAM。端口A用于从存储器执行写入操作,端口B可用于从存储器读取。

下面介绍XPM_MEMORY实例的基本读写端口使用情况。它不区分端口A和端口B。

所有同步信号都对 clk[a|b] 的上升沿敏感,它被假定为根据目标设备和内存原语要求运行的缓冲和切换时钟信号。

- 隐式执行读取操作以组合方式寻址 addrb。数据输出在 enb 置位的每个 clkb 周期被寄存。

在关联的读取操作之后,读取数据出现在 doutb 端口 READ_LATENCY_B 个clkb 周期。

当 ena 和 wea 在每个 clka 周期都有效时,显式执行写操作,将 dina 写入地址 addra。

所有读写操作都由启动clk[a|b] 周期的en[a|b] 值门控,无论输入或输出延迟如何。当 ena 在重合的 clk[a|b] 周期上被取消断言时,addra 和 wea 输入没有影响。

对于置位 rstb 的每个 clkb 周期,最终输出寄存器会立即同步重置为 READ_RESET_VALUE_B,而不管 READ_LATENCY_B。

对于regceb 有效且rstb 无效的每个clkb 周期,最终输出寄存器捕获并输出前一个流水线寄存器的值。

模块输入上提供的未驱动或未知值将产生未定义的内存阵列和输出端口行为。

当使用MEMORY INIT PARAM 时,支持的最大内存大小为4K bits。

不支持使用非对称字节写使能进行内存初始化。

在简单双端口 RAM 配置中,仅考虑 WRITE_MODE_B(尽管端口 A 具有写入权限,但使用 WRITE_MODE_B,因为输出数据将连接到端口 B,并且在传递给原语时,相同的模式值在内部应用于 WRITE_MODE_A ).

选择无效配置将导致DRC。为了在更大的内存(>1 Mb) 中获得更好的时序性能,请使用1 的CASCADE_HEIGHT 并具有足够的读取延迟。

注意:

当属性“CLOCKING_MODE”设置为“common_clock”时,所有通过端口A 和端口B 对内存的读/写操作都在clka 上执行。如果该属性设置为“independent_clock”,则端口A的读/写操作基于clka执行,端口B的读/写操作基于clkb执行。

当有效地址位与物理内存地址位置匹配时,写入超出范围的地址位置可能会覆盖有效地址位置。

如果设计注意避免地址冲突(在任何给定时间点写入地址!= 读取地址),基于独立时钟分布式RAM 的内存需要set_false_path 约束。

如果 XPM_MEMORY 需要处理必要的约束,则设置 USE_EMBEDDED_CONSTRAINT = 1。如果 USE_EMBEDDED_CONSTRAINT = 0,Vivado 可能触发 Timing-6 或 Timing-7 或两者。

或者,您也可以在 USE_EMBEDDED_CONSTRAINT = 0 时添加约束。下面提供了添加此约束的示例。如果端口 B 也具有独立时钟配置的写入权限,则也需要为 clkb 添加类似的约束。

set_false_path -from [filter [all_fanout -from [get_ports clka]

-flat -endpoints_only] {IS_LEAF}] -through [get_pins -of_objects

[get_cells -hier * -filter {PRIMITIVE_SUBGROUP==LUTRAM ||

PRIMITIVE_SUBGROUP==dram || PRIMITIVE_SUBGROUP==drom}]

-filter {DIRECTION==OUT}]

- 如果 "CLOCKING_MODE" 设置为 "independent_clock" ,Vivado 可能会触发误报 CDC-1 警告,可以忽略。

- UltraRAM 的专用输入和输出寄存器的使用由基于 READ_LATENCY_B 值的综合控制。例如,如果 4 个 UltraRAM 级联并且 READ_LATENCY_B ≥ 4,则综合将尽可能多地吸收 UltraRAM 原语中的寄存器。

- 对于UltraRAM,OREG 的启用取决于READ_LATENCY_B 和WRITE_MODE_B。当 READ_FIRST 模式下 READ_LATENCY_B ≥ 3 且 WRITE_FIRST 模式下 READ_LATENCY_B ≥4 时启用 OREG。

- 对于更大的存储器 (≥2 MB),建议的读取延迟必须 > 8,因为 Vivado 综合使用的默认级联高度为 8。

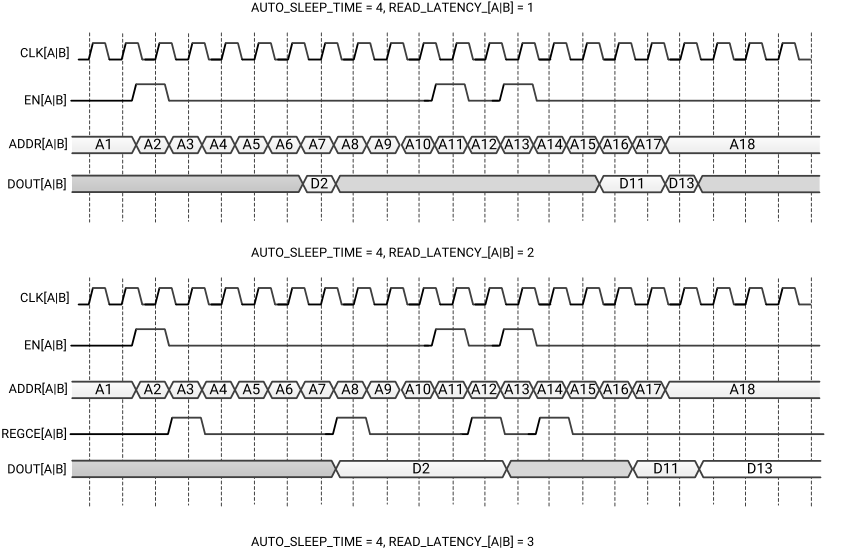

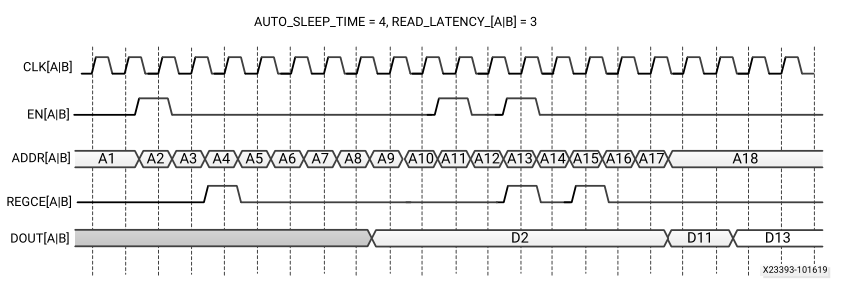

Timing Diagrams

注意:当 OREG 属性设置为 TRUE 时,UltraRAM 原语不支持在睡眠断言在时钟的上升沿上被识别之前时钟周期中的写/读访问。对于 UltraRAM 配置,在睡眠断言之前的时钟周期内不允许对存储器进行写/读访问。

ECC Modes

当内存类型设置为简单双端口 RAM 时,Block RAM 和 UltraRAM 原语都支持 ECC。支持的三种 ECC 模式是:

- 既编码又解码

- 仅编码

- 仅解码

三种 ECC 模式的读写用法与上文介绍部分所述相同。请参阅 UltraScale 架构内存资源用户指南 (UG573) 的“内置纠错”部分,了解有关此功能(如错误注入和校正子位计算)的更多详细信息。

以上ECC模式中的WRITE_DATA_WIDTH_A、READ_DATA_WIDTH_B、MEMORY_SIZE属性都有限制。

- 编码和解码 WRITE_DATA_WIDTH_A 和 READ_DATA_WIDTH_B 都必须是 64 位的倍数。违反此规则将导致 XPM_Memory 中出现 DRC。

- 仅编码 WRITE_DATA_WIDTH_A 必须是 64 位的倍数,READ_DATA_WIDTH_B 必须是 72 位的倍数。 MEMORY_SIZE 必须是 READ_DATA_WIDTH_B 的倍数。违反这些规则将导致 DRC。

- 仅解码 WRITE_DATA_WIDTH_A 必须是 72 位的倍数,READ_DATA_WIDTH_B 必须是 64 位的倍数。 MEMORY_SIZE 必须是 WRITE_DATA_WIDTH_A 的倍数。违反这些规则将导致 DRC。

当启用 ECC 时,不支持以下内容:

- 不对称

- 初始化

- 复位(非零复位值或复位断言)

注意:ECC 使用 BRAM/URAM 宏中可用的硬 ECC 块,数据宽度应为倍数64/72。将 ECC IP 用于其他数据宽度组合。

自动睡眠模式

- 此功能仅适用于 MEMORY_PRIMITIVE 为 URAM 且在 UltraRAM 中进行内部控制以检查其是否可以进入睡眠模式以及何时需要唤醒。因此,无需显式控制 SLEEP 引脚即可自动实现节能。

- 当AUTO_SLEEP_TIME 为0 时,该功能被禁用。当 AUTO_SLEEP_TIME 不为零时,XPM_MEMORY 在除 rst[a|b] 之外的所有输入信号上构造等于 AUTO_SLEEP_TIME 值的流水线寄存器。

- 如果AUTO_SLEEP_TIME 太低,则UltraRAM 进入睡眠和唤醒的频率太高,这会导致消耗更多功率。

- 实现的睡眠周期数通过以下公式计算:

- 如果连续非活动周期数 < AUTO_SLEEP_TIME,则睡眠周期数 = 0。

- 如果连续非活动周期数≥AUTO_SLEEP_TIME,则连续睡眠周期数 = 连续非活动周期数 – 3。

- 非活动周期定义为任一端口都没有读/写操作的周期。

- 读取操作和数据到达dout[a|b] 之间的延迟是AUTO_SLEEP_TIME + READ_LATENCY_[A|B] 个时钟周期(假设当输出数据管道存在时REGCE 为高电平)。

- 当 READ_LATENCY_[A|B] 设置为 1 或 2 时,XPM_Memory 在行为上模拟自动睡眠功能并在 RAM 处于自动睡眠模式时在 DOUT[A|B] 上强制“x”。对于大于 2 的 READ_LATENCY_[A|B],“x”的传播不会发生在 DOUT[A| B] 因为输出寄存器在 UltraRAM 退出睡眠模式后获得时钟使能(延迟读取使能)。

自动睡眠模式对于较大的内存或任何活动很少的内存最有效。

不同读取延迟下自动睡眠模式的时序图如下所示。

Port Descriptions

设计输入法

Instantiation Yes

Inference No

IP and IP Integrator Catalog No

可用属性

Verilog Instantiation Template

// xpm_memory_sdpram: Simple Dual Port RAM

// Xilinx Parameterized Macro, version 2022.2

xpm_memory_sdpram #(

.ADDR_WIDTH_A(6), // DECIMAL

.ADDR_WIDTH_B(6), // DECIMAL

.AUTO_SLEEP_TIME(0), // DECIMAL

.BYTE_WRITE_WIDTH_A(32), // DECIMAL

.CASCADE_HEIGHT(0), // DECIMAL

.CLOCKING_MODE("common_clock"), // String

.ECC_MODE("no_ecc"), // String

.MEMORY_INIT_FILE("none"), // String

.MEMORY_INIT_PARAM("0"), // String

.MEMORY_OPTIMIZATION("true"), // String

.MEMORY_PRIMITIVE("auto"), // String

.MEMORY_SIZE(2048), // DECIMAL

.MESSAGE_CONTROL(0), // DECIMAL

.READ_DATA_WIDTH_B(32), // DECIMAL

.READ_LATENCY_B(2), // DECIMAL

.READ_RESET_VALUE_B("0"), // String

.RST_MODE_A("SYNC"), // String

.RST_MODE_B("SYNC"), // String

.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.USE_EMBEDDED_CONSTRAINT(0), // DECIMAL

.USE_MEM_INIT(1), // DECIMAL

.USE_MEM_INIT_MMI(0), // DECIMAL

.WAKEUP_TIME("disable_sleep"), // String

.WRITE_DATA_WIDTH_A(32), // DECIMAL

.WRITE_MODE_B("no_change"), // String

.WRITE_PROTECT(1) // DECIMAL

)

xpm_memory_sdpram_inst (

.dbiterrb(dbiterrb), // 1-bit output: Status signal to indicate double bit error occurrence

// on the data output of port B.

.doutb(doutb), // READ_DATA_WIDTH_B-bit output: Data output for port B read operations.

.sbiterrb(sbiterrb), // 1-bit output: Status signal to indicate single bit error occurrence

// on the data output of port B.

.addra(addra), // ADDR_WIDTH_A-bit input: Address for port A write operations.

.addrb(addrb), // ADDR_WIDTH_B-bit input: Address for port B read operations.

.clka(clka), // 1-bit input: Clock signal for port A. Also clocks port B when

// parameter CLOCKING_MODE is "common_clock".

.clkb(clkb), // 1-bit input: Clock signal for port B when parameter CLOCKING_MODE is

// "independent_clock". Unused when parameter CLOCKING_MODE is

// "common_clock".

.dina(dina), // WRITE_DATA_WIDTH_A-bit input: Data input for port A write operations.

.ena(ena), // 1-bit input: Memory enable signal for port A. Must be high on clock

// cycles when write operations are initiated. Pipelined internally.

.enb(enb), // 1-bit input: Memory enable signal for port B. Must be high on clock

// cycles when read operations are initiated. Pipelined internally.

.injectdbiterra(injectdbiterra), // 1-bit input: Controls double bit error injection on input data when

// ECC enabled (Error injection capability is not available in

// "decode_only" mode).

.injectsbiterra(injectsbiterra), // 1-bit input: Controls single bit error injection on input data when

// ECC enabled (Error injection capability is not available in

// "decode_only" mode).

.regceb(regceb), // 1-bit input: Clock Enable for the last register stage on the output

// data path.

.rstb(rstb), // 1-bit input: Reset signal for the final port B output register stage.

// Synchronously resets output port doutb to the value specified by

// parameter READ_RESET_VALUE_B.

.sleep(sleep), // 1-bit input: sleep signal to enable the dynamic power saving feature.

.wea(wea) // WRITE_DATA_WIDTH_A/BYTE_WRITE_WIDTH_A-bit input: Write enable vector

// for port A input data port dina. 1 bit wide when word-wide writes are

// used. In byte-wide write configurations, each bit controls the

// writing one byte of dina to address addra. For example, to

// synchronously write only bits [15-8] of dina when WRITE_DATA_WIDTH_A

// is 32, wea would be 4'b0010.

);

// End of xpm_memory_sdpram_inst instantiation

参考资料:UG974

Xilinx XPM使用说明--XPM_MEMORY_SDPRAM的更多相关文章

- [原创]iFPGA-Cable FT2232H Xilinx / Altera / Lattice 三合一JTAG & UART调试器-详细使用说明

iFPGA-Cable调试器使用说明 全文分为6部分: 第0部分:实物.连线及其驱动安装说明 第1部分:Xilinx JTAG 第2部分:UART 第3部分:Altera JTAG 第4部分:Latt ...

- PCIE_DMA实例一:xapp1052详细使用说明

一:前言 很多和我一样初学pcie的硬件工程师都会遇到这样一个问题,看了不少pcie相关的资料,还是搞不清这玩意儿到底该怎么用.于是我们打开ISE的core_generator工具,生成了一个pcie ...

- Atitit.项目修改补丁打包工具 使用说明

Atitit.项目修改补丁打包工具 使用说明 1.1. 打包工具已经在群里面.打包工具.bat1 1.2. 使用方法:放在项目主目录下,执行即可1 1.3. 打包工具的原理以及要打包的项目列表1 1. ...

- awk使用说明

原文地址:http://www.cnblogs.com/verrion/p/awk_usage.html Awk使用说明 运维必须掌握的三剑客工具:grep(文件内容过滤器),sed(数据流处理器), ...

- Xilinx下载安装与在win10闪退问题解决方法

Xilinx的14.4版本的下载链接(百度云的上传了N多次都提示失败,所以就换了360云盘上传) https://yunpan.cn/cPHKLjbX9RueM (提取码:2a5a)下载后解压到以下目 ...

- “我爱背单词”beta版发布与使用说明

我爱背单词BETA版本发布 第二轮迭代终于画上圆满句号,我们的“我爱背单词”beta版本已经发布. Beta版本说明 项目名称 我爱背单词 版本 Beta版 团队名称 北京航空航天大学计算机学院 拒 ...

- Oracle 中 union 和union all 的简单使用说明

1.刚刚工作不久,经常接触oracle,但是对oracle很多东西都不是很熟.今天我们来了解一下union和union all的简单使用说明.Union(union all): 指令的目的是将两个 S ...

- Map工具系列-02-数据迁移工具使用说明

所有cs端工具集成了一个工具面板 -打开(IE) Map工具系列-01-Map代码生成工具说明 Map工具系列-02-数据迁移工具使用说明 Map工具系列-03-代码生成BySQl工具使用说明 Map ...

- Map工具系列-03-代码生成BySQl工具使用说明

所有cs端工具集成了一个工具面板 -打开(IE) Map工具系列-01-Map代码生成工具说明 Map工具系列-02-数据迁移工具使用说明 Map工具系列-03-代码生成BySQl工具使用说明 Map ...

- jQuery验证控件jquery.validate.js使用说明

官网地址:http://bassistance.de/jquery-plugins/jquery-plugin-validation jQuery plugin: Validation 使用说明 转载 ...

随机推荐

- 《HTTP权威指南》– 2.HTTP报文与URL资源

URL与资源: 大多数URL方案的URL语法都建立在这个由9部分构成的通用格式上. 方案: 访问服务器以获取资源要使用哪种协议 用户: 某些方案访问资源时需要的用户名 密码: 用户名后面可能包含的密码 ...

- 04-CURD

Insert @Test//测试插入 public void insertTest(){ User user = new User(); user.setName("wsk"); ...

- 中国蚁剑 - AntSword

中国蚁剑 - AntSword 中国蚁剑是一种跨平台操作工具,它主要提供给用户用于有效的网络渗透测试以及进行正常运行的网站. 否则任何人不得将网站用于其无效用途以及可能的等目的.自己承担并追究其相关责 ...

- [OpenCV实战]39 在OpenCV中使用ArUco标记的增强现实

文章目录 1 什么是ArUco标记? 2 在OpenCV中生成ArUco标记 3 检测Aruco标记 4 增强现实应用 5 总结和代码 5.1 生成aruco标记 5.2 使用aruco增强现实 6 ...

- [C++标准模板库:自修教程与参考手册]关于deque

Deque的基本概念 deque和vector很相似,也提供随机存取的能力,将元素都动态地存储在一个数组中,最大的区别就是:deque的头和尾都是开放的,非常方便在头尾两端进行一些操作.(重点在于:d ...

- [深度探索C++对象模型]memcpy和memset注意事项

不管使用memcpy()还是memset(),都只有在"classes不含任何由编译器产生的内部members"时才能运行.如果这个类声明一个或者一个以上的virtual func ...

- element上传图片组件使用方法|图片回显|格式转换base64

upload上传组件的使用方法 上传图片后自动上传(也可以手动上传),图片上传成功后由后端返回特定图片地址,在表单提交后将表单数据同图片地址一并返回即可完成图片上传功能. 组件HTML <!-- ...

- Vue项目 invalid host header 问题 配置 disableHostCheck:true报错

项目场景: 解决 Vue 项目 invalid host header 问题disableHostCheck:true报错 问题描述 使用内网穿透时出现 invalid host header 找了好 ...

- SqlServer服务中利用触发器对指定账户进行登录ip限制提升安全性

转眼间上次写文章已经是 2022年12月15日的事情啦,本来从2022年7月份开始写作之后保持着每周一篇,然而从12月15日后断更了这么久,经历了,隔离.阳.过年.从今天开始继续坚持写作,本片文章给大 ...

- 【开源】libinimini:适用于单片机的极简 ini 解析库

介绍说明 最近自己基于 XR872 在做一个小作品练习练习,具备可以配置的功能,选择了使用 ini 作为配置文件.我调研了网上常见的 ini 解析库,几乎都涉及到了 fopen()/fgets().. ...