verilog 计算机网络 仿真 激励 pcap

做verilog网络逻辑时,需要产生正确的数据包格式激励,手写激励真烦人,现在让testbench读取pcap文件,则可以精确还原数据包的bit与时序,省去了一大批麻烦

1.设计读取逻辑

`timescale 1ns / 1ps

`define NULL // Coder: joe

// Description:

// 将pcap文件中的数据包读出来,8bit位宽

//

//

//

//

// module PcapParser

#(

parameter pcap_filename = "none",

parameter ipg =

) (

input CLOCK,

input pause,

output reg available = ,

output reg datavalid = ,

output reg [:] data = ,

output reg [:] pktcount = ,

output reg newpkt = ,

output reg pcapfinished =

); // buffers for message

reg [:] global_header [:];

reg [:] packet_header [:]; integer swapped = ;

integer toNanos = ;

integer file = ;

integer r = ;

integer eof = ;

integer i = ;

integer pktSz = ;

integer diskSz = ;

integer countIPG = ; initial begin // open pcap file

if (pcap_filename == "none") begin

$display("pcap filename parameter not set");

$finish_and_return();

end file = $fopen(pcap_filename, "rb");

if (file == `NULL) begin

$display("can't read pcap input");

$finish_and_return();

end // read binary global_header

// r = $fread(file, global_header);

r = $fread(global_header,file); // check magic signature to determine byte ordering

if (global_header[] == 'hD4 && global_header[1] == 8'hC3 && global_header[] == 'hB2) begin

$display(" pcap endian: swapped, ms");

swapped = ;

toNanos = 'd1000000;

end else if (global_header[] == 'hA1 && global_header[1] == 8'hB2 && global_header[] == 'hC3) begin

$display(" pcap endian: native, ms");

swapped = ;

toNanos = 'd1000000;

end else if (global_header[] == 'h4D && global_header[1] == 8'h3C && global_header[] == 'hb2) begin

$display(" pcap endian: swapped, nanos");

swapped = ;

toNanos = 'd1;

end else if (global_header[] == 'hA1 && global_header[1] == 8'hB2 && global_header[] == 'h3c) begin

$display(" pcap endian: native, nanos");

swapped = ;

toNanos = 'd1;

end else begin

$display(" pcap endian: unrecognised format %02x%02x%02x%02x", global_header[], global_header[], global_header[], global_header[] );

$finish_and_return();

end

end always @(posedge CLOCK)

begin

if (eof == && diskSz == && countIPG == ) begin

// read packet header

// fields of interest are U32 so bear in mind the byte ordering when assembling

// multibyte fields

r = $fread(packet_header, file);

eof = $feof(file); if ( eof == ) begin

if (swapped == ) begin

pktSz = {packet_header[],packet_header[],packet_header[] ,packet_header[] };

diskSz = {packet_header[],packet_header[],packet_header[],packet_header[]};

end else begin

pktSz = {packet_header[ ],packet_header[ ],packet_header[],packet_header[]};

diskSz = {packet_header[],packet_header[],packet_header[],packet_header[]};

end $display(" packet %0d: incl_length %0d orig_length %0d eof %0d", pktcount, pktSz, diskSz, eof ); available <= ;

newpkt <= ;

pktcount <= pktcount + ;

countIPG <= ipg; // reload interpacket gap counter

end

end else if ( diskSz > ) begin // packet content is byte-aligned, no swapping required

if (~pause) begin

newpkt <= ;

diskSz <= diskSz - ;

data <= $fgetc(file);

eof = $feof(file);

if ( eof != || diskSz == ) begin

available <= ;

end else begin

datavalid <= ;

end

end else begin

datavalid <= ;

end

end else if (countIPG > ) begin

countIPG <= countIPG - ;

end else if (eof != ) begin

pcapfinished <= ; // terminal loop here

end end endmodule

2.编写testbench文件

将 tcp-4846-connect-disconnect.pcap 文件放在工程目录下。自己随意放置一个,然后修改源码中文件的名称,才可以读到。

`timescale 1ns / 1ps

`define NULL // Coder: joe

// Description:

// 测试文件,读取数据,打入模块

//

//

//

//

// module PcapParser_test

#(

parameter DATA_WIDTH = ,

parameter CTRL_WIDTH=,

parameter STAGE_NUMBER = ,

parameter NUM_QUEUES =

); // Inputs

reg CLOCK = ;

reg paused = ;

reg rst=;

wire available;

wire [:] pktcount;

wire streamvalid;

wire [:] stream;

wire pcapfinished;

wire newpkt; wire out_wr;

wire [CTRL_WIDTH-:] out_ctl;

wire [DATA_WIDTH-:] out_data; wire out_wr1;

wire [CTRL_WIDTH-:] out_ctl1;

wire [DATA_WIDTH-:] out_data1; // Instantiate the Unit Under Test (UUT)

PcapParser #(

.pcap_filename( "tcp-4846-connect-disconnect.pcap" )

) pcap (

.CLOCK(CLOCK),

.pause(paused),

.available(available),

.datavalid(streamvalid),

.data(stream),

.pktcount(pktcount),

.newpkt(newpkt),

.pcapfinished(pcapfinished)

); always # CLOCK = ~CLOCK; //always #100 paused = ~paused; integer i; initial begin $dumpfile("pcap.lxt");

//$dumpvars(0); // Initialize Inputs

$display("Reading from pcap"); // Wait 100 ns for global reset to finish

#;

rst = ; // Add stimulus here

while (~pcapfinished ) begin

//$display("stream: %8d %x %d %x %x %c", i, paused, pktcount, streamvalid, stream, stream);

#

i = i+;

end $finish; end endmodule

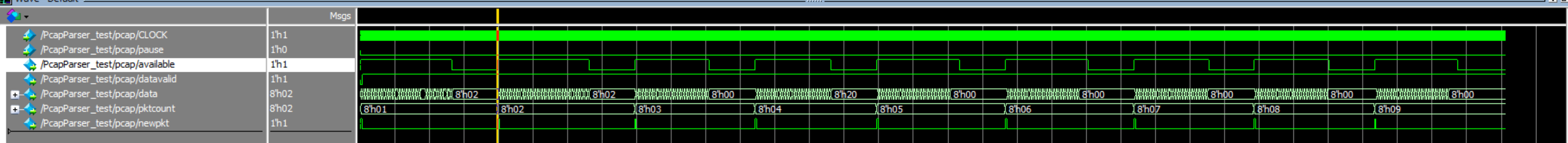

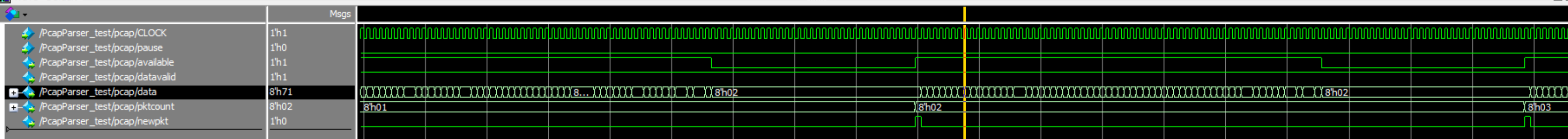

3.读取仿真激励结果

=====================

qsy

2018-7-5 11:39:44

verilog 计算机网络 仿真 激励 pcap的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- 【仿真】【modelsim】:verilog功能仿真流程

一.编写verilog源文件,在diamond中编译.编写testbench文件.在diamond设置中将仿真工具设置为modelsim,运行仿真向导 二.自动进入modelsim, 编译全部 运行仿 ...

- 全平台轻量级 Verilog 编译器 & 仿真环境

一直苦于 modelsim 没有Mac版本,且其体量过大,在学习verilog 时不方便使用. 终于找到一组轻量级且全平台 ( Linux+Windows+macOS ) 的编译仿真工具组. Icar ...

- VCS使用学习笔记(1)——Verilog相关的仿真知识

本文主要学习Verilog的仿真特性,以及仿真器对Verilog的处理,算是对Verilog知识的增量学习.本文内容与我的另一篇博文(http://www.cnblogs.com/IClearner/ ...

- 【设计经验】5、Verilog对数据进行四舍五入(round)与饱和(saturation)截位

一.软件平台与硬件平台 软件平台: 操作系统:Windows 8.1 64-bit 开发套件:Vivado2015.4.2 Matlab2016a 仿真工具:Vivado自带仿真器 二.引言 在利用 ...

- Verilog对数据进行四舍五入(round)与饱和(saturation)截位

转自https://www.cnblogs.com/liujinggang/p/10549095.html 一.软件平台与硬件平台 软件平台: 操作系统:Windows 8.1 64-bit 开发套件 ...

- DC综合及仿真验证和DFT测试

综合技术是提高设计产能的一个很重要的技术,没有综合技术的发展就不可能用HDL实现电路的设计,因为HDL开始是用来供电路仿真建模使用的,到了后来才把其中一部分子集作为可综合的语言,也就是R ...

- vivado2018.3 与 modelsim联合仿真

我用的是目前最新版本的软件,vivado2018.3与modelsim10.6d.废话不多说,直接上操作 1.modelsim编译vivado库 1)双击启动vivado软件,如下图操作 2)Simu ...

- 浅谈用ModelSim+Synplify+Quartus来实现Altera FPGA的仿真

浅谈用ModelSim+Synplify+Quartus来实现Altera FPGA的仿真 工作内容: Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业 ...

随机推荐

- django网站

https://www.djangoproject.com/download/ 指定版本安装django命令:pip install Django==1.11.8

- Leetcode 63

//一维dp还是比较难写的class Solution { public: int uniquePathsWithObstacles(vector<vector<int>>&a ...

- vue兼容ie

为了兼容IE github build/webpack.base.conf.js [vuex] vuex requires a Promise polyfill in this browser. // ...

- BZOJ1228 [SDOI2009]E&D

蒟蒻不会= = 话说写题解的巨巨也只会打表233 反正先A掉再说 /************************************************************** Pro ...

- POJ 2823 单调队列入门水题

最最基础的单调队列题目.一个单增一个单减.还是可以借此好好理解一下单调队列的. #include <stdio.h> #include <string.h> #include ...

- 利用django.core.mail发送QQ邮件的配置

1.在 settings.py 的最后面加上类似这些 EMAIL_USE_SSL = True EMAIL_HOST = 'smtp.qq.com' # 如果是 163 改成 smtp.163.com ...

- Beta阶段第1周/共2周 Scrum立会报告+燃尽图 01

作业要求[https://edu.cnblogs.com/campus/nenu/2018fall/homework/2383] 版本控制:https://git.coding.net/liuyy08 ...

- PostgreSQL常用插件收集

hexdump -C 数据表文件 -- 查看表文件中数据. pg_stat_statements pgcompacttable -- 在减少锁的情况下,清理表和索引的老空间. pg_repack--P ...

- C++17中那些值得关注的特性(上)

C++17标准在2017上半年已经讨论确定,正在形成ISO标准文档,今年晚些时候会正式发布.本文将介绍最新标准中值得开发者关注的新特新和基本用法. 总的来说C++17相比C++11的新特性来说新特性不 ...

- 经典排序方法 python

数据的排序是在解决实际问题时经常用到的步骤,也是数据结构的考点之一,下面介绍10种经典的排序方法. 首先,排序方法可以大体分为插入排序.选择排序.交换排序.归并排序和桶排序四大类,其中,插入排序又分为 ...