Verilog 加法器和减法器(2)

类似半加器和全加器,也有半减器和全减器。

半减器只考虑当前两位二进制数相减,输出为差以及是否向高位借位,而全减器还要考虑当前位的低位是否曾有借位。它们的真值表如下:

对半减器,diff = x ^y, cin = ~x&y

对全减器,要理解真值表,可以用举列子的方法得到,比如4’b1000-4b'0001,则第一位对应0 1 0 1 1第二位对应的是0 0 1 1 1

从真值表中,可以得到 diff = x ^ y ^cout, cin = (~x&(y^cout))|(y&cout)

推导过程:diff = ~x&~y&cout + ~x&y&~cout +x&~y&~cout+x&y&cout=~x&(~y&cout+y&~cout)+x&(~y&~cout+y&cout)=~x&(y^cout)+x&~(y^cout)=x^y^cout;

cin = ~x&~y&cout+~x&y&~cout+~x&y&cout+x&y&cout=~x&(~y&cout+~x&~cout)+(~x+x)&y&cout=~x&(y^cout)+y&cout

注意:这儿 +和|都表示或。

半减器的verilog代码和testbench代码如下:

module halfsub(x,y,d,cin); input x;

input y; output d;

output cin; assign d = x^y;

assign cin = (~x)&y; endmodule

`timescale 1ns/1ns

`define clock_period 20 module halfsub_tb;

reg x,y; wire cin; //carryover

wire d;

reg clk; halfsub halfsub_0(

.x(x),

.y(y),

.d(d),

.cin(cin)

); initial clk = 0;

always #(`clock_period/2) clk = ~clk; initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random; end initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random; end initial begin

#(`clock_period*20)

$stop;

end endmodule

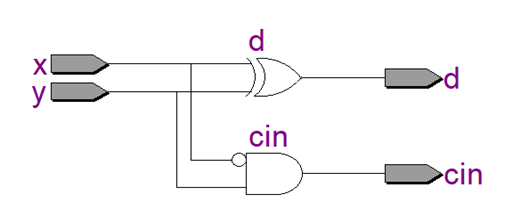

用rtl viewer,可以看到半减器逻辑图如下:

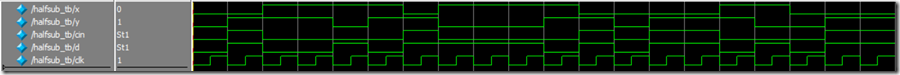

半减器功能验证的波形:

全减器的verilog代码和testbench代码如下:

module fullsub(cout,x,y,d,cin); input cout; // carry out bit, borrowed by its next low bit

input x;

input y; output d;

output cin; assign d = x^y^cout;

assign cin = (~x&(y^cout))|(y&cout); endmodule

`timescale 1ns/1ns

`define clock_period 20 module fullsub_tb;

reg x,y,cout; wire cin; //carryover

wire d;

reg clk; fullsub fullsub_0(

.cout(cout),

.x(x),

.y(y),

.d(d),

.cin(cin)

); initial clk = 0;

always #(`clock_period/2) clk = ~clk; initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random; end initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random; end initial begin

cout = 0;

repeat(20)

#(`clock_period) cout = $random; end initial begin

#(`clock_period*20)

$stop;

end endmodule

用rtl viewer,可以看到全减器逻辑图如下:

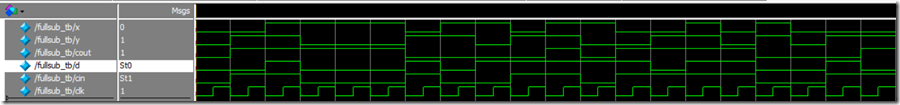

全减器的功能验证波形:

Verilog 加法器和减法器(2)的更多相关文章

- Verilog 加法器和减法器(8)-串行加法器

如果对速度要求不高,我们也可以使用串行加法器.下面通过状态机来实现串行加法器的功能. 设A=an-1an-2-a0, B=bn-1bn-2-b0,是要相加的两个无符号数,相加的和为:sum=sn-1s ...

- Verilog 加法器和减法器(4)

类似于行波进位加法器,用串联的方法也能够实现多位二进制数的减法操作. 比如下图是4位二进制减法逻辑电路图. 8位二进制减法的verilog代码如下: module subn(x, y, d,cin) ...

- Verilog 加法器和减法器(7)

在计算机中浮点数 表示通常采用IEEE754规定的格式,具体参考以下文章. https://www.cnblogs.com/mikewolf2002/p/10095995.html 下面我们在Veri ...

- Verilog 加法器和减法器(6)

为了减小行波进位加法器中进位传播延迟的影响,可以尝试在每一级中快速计算进位,如果能在较短时间完成计算,则可以提高加法器性能. 我们可以进行如下的推导: 设 gi=xi&yi, pi = xi ...

- Verilog 加法器和减法器(3)

手工加法运算时候,我们都是从最低位的数字开始,逐位相加,直到最高位.如果第i位产生进位,就把该位作为第i+1位输入.同样的,在逻辑电路中,我们可以把一位全加器串联起来,实现多位加法,比如下面的四位加法 ...

- Verilog 加法器和减法器(1)

两个一位的二进制数x,y相加,假设和为s,进位为cout,其真值表为: 从真值表中,我们可以得到:s = x^y, cout = x&y,实现两个一位数相加的逻辑电路称为半加器. 实现该电路的 ...

- Verilog 加法器和减法器(5)

前面二进制加法运算,我们并没有提操作数是有符号数,还是无符号数.其实前面的二进制加法对于有符号数和无符号数都成立.比如前面的8位二进制加法运算,第一张图我们选radix是unsigned,表示无符号加 ...

- 基于Xilinx的Synthesize

所谓综合.就是讲HDL语言.原理图等设计输入翻译成由与.或.非们和RAM.触发器登记本逻辑单元的逻辑连接(即网表).并依据目标和要求(约束条件)优化生成的逻辑连接. ISE-XST XST是Xilin ...

- FPGA综合工具--Synplify Pro的常用选项及命令

最近要用到Synplify,但以前没使用过,无基础,找到一篇帖子,隧保存下来. 本文转自:http://blog.sina.com.cn/s/blog_65fe490d0100v8ax.html Sy ...

随机推荐

- python3之Django模型(一)

1.模型概述 模型是关于您的数据的唯一,明确的信息来源,它包含您正在存储的数据的重要字段和行为.通常,每个模型映射到单个数据库表. 每个模型都是一个子类的python类django.db.models ...

- SOAP port

To determine the SOAP port on WebSphere Base: Server Types > WebSphere application servers > [ ...

- Orleans介绍

一.介绍 Orleans是一个框架,提供了一个直接的方法来构建分布式高规模计算应用程序 默认可扩展 -> Orleans处理构建分布式系统的复杂性,使您的应用程序能够扩展到数百台服务器.低延迟 ...

- View 事件分发

View 事件分发 学习自 <Android开发艺术探索> 官方文档-MotionEvent 事件分发机制漫谈 View的事件分发机制,使我们了解View的工作原理继而学习如何自定义Vie ...

- android 进程间通信 messenger 是什么 binder 跟 aidl 区别 intent 进程间 通讯? android 消息机制 进程间 android 进程间 可以用 handler么 messenger 与 handler 机制 messenger 机制 是不是 就是 handler 机制 或 , 是不是就是 消息机制 android messenge

韩梦飞沙 韩亚飞 313134555@qq.com yue31313 han_meng_fei_sha messenger 是什么 binder 跟 aidl 区别 intent 进程间 通讯 ...

- HDU.5819.Knights(概率DP)

题目链接 参考一下这的. \(Description\) 数轴上有n个骑士,分别位于1,2,3,...,n,它们的移动速度相同,初始移动方向已知.当两个骑士相遇时,各有50%的概率获胜,失败的骑士就死 ...

- C#中四种常用集合的运用(非常重要)

C#中4个常用的集合 1.ArrayList ArrayList类似于数组,有人也称它为数组列表.ArrayList可以动态维护,而数组的容量是固定的. 它的索引会根据程序的扩展而重新进行分配和调整. ...

- Consul功能简介

Consul 是 HashiCorp 公司的一个用于实现分布式系统的服务发现与配置工具.Consul内置了服务注册与发现框 架.分布一致性协议实现.健康检查.Key/Value存储.多数据中心方案.由 ...

- Oracle绝对值函数

1.绝对值:abs() select abs(-2) value from dual; 2.取整函数(大):ceil() select ceil(-2.001) value from dual;(-2 ...

- 使用jQuery和Bootstrap实现多层、自适应模态窗口

本篇实践一个多层模态窗口,而且是自适应的. 点击页面上的一个按钮,弹出第一层自适应模态窗口. 在第一层模态窗口内包含一个按钮,点击该按钮弹出第二层模态窗口,弹出的第二层模态窗口会挡住第一层模态窗口,即 ...