Verilog三线 - 八线译码器

参阅了一些书籍和网上的写法,在此Mark。

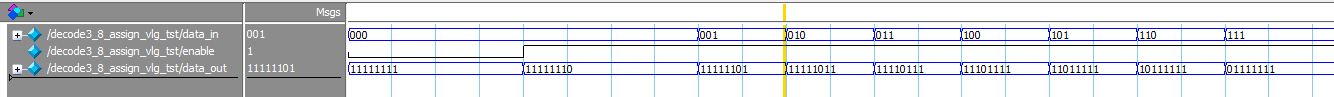

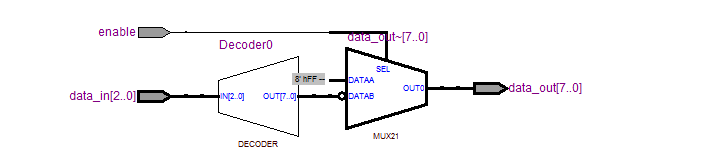

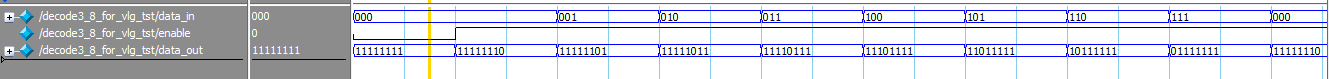

布尔表达式法

module decode3_8_assign (data_in,data_out,enable);//算法实现

input [:] data_in;

input enable;

output [:] data_out;

reg data_a = 'b00000001;

assign data_out = (enable)?(~(data_a << data_in)):'b11111111;

endmodule

testbench:

`timescale ns/ ps

module decode3_8_assign_vlg_tst();

reg [:] data_in;

reg enable;

wire [:] data_out;

decode3_8_assign i1 (

.data_in(data_in),

.data_out(data_out),

.enable(enable)

);

initial

begin

enable = ;

data_in = ;

# enable = ;

# data_in = ;

# data_in = ;

# data_in = ;

# data_in = ;

# data_in = ;

# data_in = ;

# data_in = ;

# data_in = ;

end

endmodule

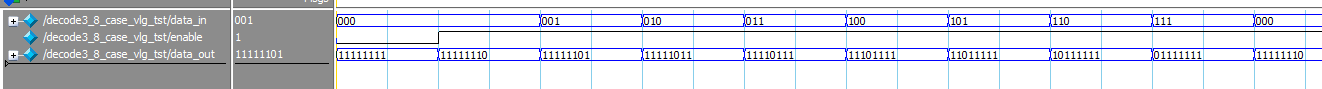

case语句法

module decode3_8_case (data_in,data_out,enable);

input [:] data_in;

input enable;

output [:] data_out;

reg [:] data_out;

always @ (data_in or enable)

begin

if (enable)

case (data_in)

'b000 : data_out = 8'b11111110;

'b001 : data_out = 8'b11111101;

'b010 : data_out = 8'b11111011;

'b011 : data_out = 8'b11110111;

'b100 : data_out = 8'b11101111;

'b101 : data_out = 8'b11011111;

'b110 : data_out = 8'b10111111;

'b111 : data_out = 8'b01111111;

default : data_out = 'bxxxxxxxx;

endcase

else data_out = 'b11111111;

end

endmodule

testbench:

`timescale ps/ ps

module decode3_8_case_vlg_tst();

reg [:] data_in;

reg enable;

wire [:] data_out;

decode3_8_case i1 (

.data_in(data_in),

.data_out(data_out),

.enable(enable)

);

initial

begin

data_in = ;

enable = ;

# enable = ;

while (data_in <= 'b111)//for (i = 0;i <= 3'b111;i = i + )

begin

# data_in = data_in + ;

end

# $stop;

end

endmodule

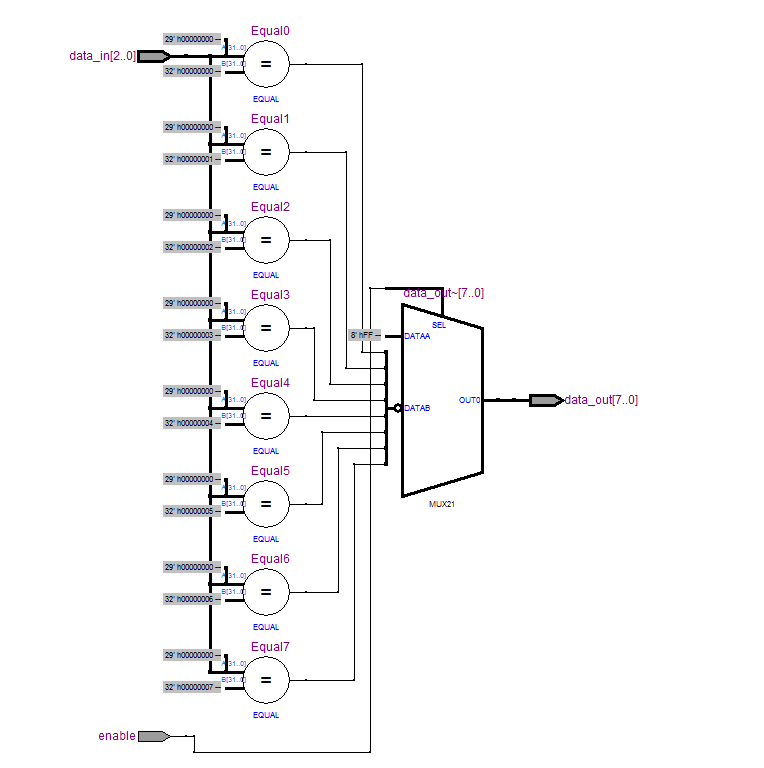

for语句法

module decode3_8_for (data_out,data_in,enable);

input [:] data_in;

input enable;

output [:] data_out;

reg [:] data_out;

integer i;

always @ (data_in or enable)

begin

if (enable)

begin

for (i = ;i < ;i = i + )

begin

if (data_in == i)

data_out[i] = ;

else

data_out[i] = ;

end

end

else

data_out = 'hff;

end

endmodule

testbench:

`timescale ps/ ps

module decode3_8_for_vlg_tst();

reg [:] data_in;

reg enable;

wire [:] data_out;

decode3_8_for i1 (

.data_in(data_in),

.data_out(data_out),

.enable(enable)

);

initial

begin

data_in = ;

enable = ;

# enable = ;

while (data_in <= 'b111)//for (i = 0;i <= 3'b111;i = i + )

begin

# data_in = data_in + ;

end

# $stop;

end

endmodule

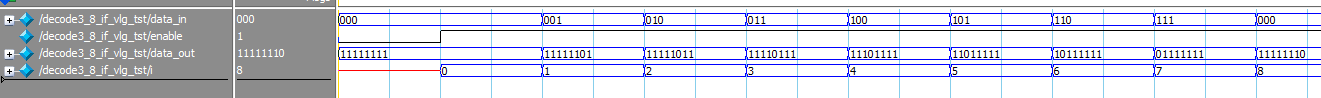

if语句法

`timescale ps/ ps

module decode3_8_for_vlg_tst();

reg [:] data_in;

reg enable;

wire [:] data_out;

decode3_8_for i1 (

.data_in(data_in),

.data_out(data_out),

.enable(enable)

);

initial

begin

data_in = ;

enable = ;

# enable = ;

while (data_in <= 'b111)//for (i = 0;i <= 3'b111;i = i + )

begin

# data_in = data_in + ;

end

# $stop;

end

endmodule

testbench:

`timescale ns/ ps

module decode3_8_if_vlg_tst();

reg [:] data_in;

reg enable;

wire [:] data_out;

integer i;

decode3_8_if i1 (

.data_in(data_in),

.data_out(data_out),

.enable(enable)

);

initial

begin

data_in = ;

enable = ;

# enable = ;

for (i = ;i < ;i = i + )

begin

# data_in = data_in + ;

end

end

endmodule

如有错误还请指出,如有侵权还请告知,如需转载请注明出处!

本人博客:http://www.cnblogs.com/yllinux/

Verilog三线 - 八线译码器的更多相关文章

- Verilog八线 - 三线优先编码器设计(74LS148)

百度百科_74LS148 if语句法 //8线-3线优先编码器设计(74LS148) // //EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO //0 | ...

- 8-3编码器,3-8译码器的verilog实现

在数字系统中,由于采用二进制运算处理数据,因此通常将信息变成若干位二进制代码.在逻辑电路中,信号都是以高,低电平的形式输出.编码器:实现编码的数字电路,把输入的每个高低电平信号编成一组对应的二进制代码 ...

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- 用Verilog语言设计一个3-8译码器

case语句 if_case语句 源码下载 Github >>

- FPGA作为从机与STM32进行SPI协议通信---Verilog实现 [转]

一.SPI协议简要介绍 SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口.SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用 ...

- 03-组合逻辑电路设计之译码器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献 课程目标: 1. 再次熟悉Quartus II工程的建立以及完整的FPGA开发流程 2. 以译码器为例学会简单组合逻辑电路设计 实验平台:无 实验原理: 组合逻辑, ...

- 对Verilog 初学者比较有用的整理(转自它处)

*作者: Ian11122840 时间: 2010-9-27 09:04 ...

- 写自己的第二级处理器(3)——Verilog HDL行为语句

我们会继续上传新书<自己动手写处理器>(未公布),今天是第七章,我每星期试试4 2.6 Verilog HDL行为语句 2.6.1 过程语句 Verilog定义的模块一般包含有过程语句,过 ...

- 基于basys2用verilog设计多功能数字钟(重写)

话不多说先上图 前言 自从学习FPGA以来,唯一做过的完整系统就是基于basys2得多功能数字表.记得当时做的时候也没少头疼,最后用时间磨出来了一个不是很完整的小系统,当时还是产生了满 ...

随机推荐

- sql的几种常用锁简述

比较全的文章地址保存下:http://www.cnblogs.com/knowledgesea/p/3714417.html SELECT * FROM dbo.AASELECT * FROM dbo ...

- python安装包的时候报错

python安装包的时候报错 今天兴致勃勃的安装了一个paramiko包,过程很顺利,但是到结尾的时候报错,这就让人不爽了. 所以呢,需要安装一个名为python-dev的软件包. 该软件包包括头文件 ...

- myEclipse更换SVN登录账号

Win10下 找到下面路径删除其下的所有文件 C:\Users\Administrator\AppData\Roaming\Subversion\auth\svn.simple AppData默认隐藏 ...

- Java-IO读写文件简单操作

Java中读写文件的关键在于节点流和处理流的的选取上,而节点流和处理流又分为面向字节.面向字符两种处理模式,因此,需要根据实际的情况选择合适的处理模式,一般而言,往往尽量尝试使用面向字符的处理模式,如 ...

- XGBoost算法

一.基础知识 (1)泰勒公式 泰勒公式是一个用函数在某点的信息描述其附近取值的公式.具有局部有效性. 基本形式如下: 由以上的基本形式可知泰勒公式的迭代形式为: 以上这个迭代形式是针对二阶泰勒展开,你 ...

- C语言有GetOpenFile吗?

windows中有个GetOpenFile的函数,就是上面那个啦!!我们怎么来实现呢?要我用C语言写出来我真的跪了..但是我们可以输入文件的[绝对路径],配合fopen函数来实现的.. 注意问题 ①文 ...

- mysql 不能插入中文记录

问题: # ERR: Incorrect string value: '\xE5\xAD\x9F\xE5\xBB\xBA...' for column 'chinese_name' at row 1 ...

- Emacs学习笔记1

Emacs笔记-Emacs基本的文本操作 使用命令时要在minibuffer缓冲区中 关于文件 注意 在对单词的操作中C开头的控制范围要比M开头的控制范围要下 对于文件的撤销操作, 不要使用C-x, ...

- [巩固C#] 三、依赖注入是什么?

阅读目录 接口 在说依赖注入之前,先了解下什么是接口. 我们在学编程的时候都知道,接口的相关规则:(来源百度百科) 1. 接口是一个引用类型,通过接口可以实现多重继承. 2. C#中接口的成员不能 ...

- C#操作Excel报错:服务器出现意外情况。

C#操作Excel表格时,如遇以下错误: 服务器出现意外情况.(异常来自 HRESULT:0x80010105(RPC_E_SERVERFAULT)) 解决方案: 打开你电脑中的Office-Exce ...