Zynq7000开发系列-7(在Zybo上运行Linaro桌面系统)

目标板:Zybo(7Z010)

主机操作系统:Ubuntu 14.04.5 LTS 64bit

交叉编译链: arm-xilinx-linux-gnueabi- [gcc version 4.9.2 (Sourcery CodeBench Lite 2015.05-17)]

Linaro系统:linaro-precise-ubuntu-desktop-20120923-436.tar.gz

〇、准备工作

1、交叉编译环境搭建,见之前的记录:Zynq7000开发系列-4(新:Xilinx交叉编译环境搭建)

2、环境变量设置

gedit /etc/bash.bashrc

在文件底部添加:

export ARCH=arm

export CROSS_COMPILE=arm-xilinx-linux-gnueabi-gcc

重启终端后生效。(后续编译命令中即可省略对ARCH、CROSS_COMPILE的指定)

一、硬件平台搭建

[目标文件:硬件平台综合生成的比特流文件system_warpper.bit、SDK创建的FSBL执行文件fsbl.elf、SDK/ubuntu创建的设备树文件system.dts/devicetree.dtb]

1、硬件平台综合生成的比特流文件system_warpper.bit

1)安装Vivado 2015.4,参考:Zynq7000开发系列-1(Vivado HLx 2016.4下载及安装)

2)安装zybo板级文件,参考:Installing Vivado Board Files for Digilent Boards

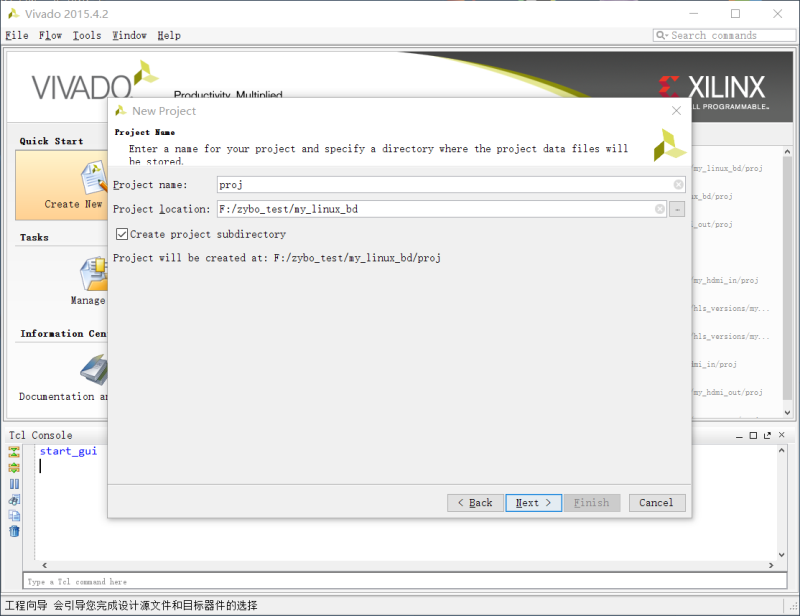

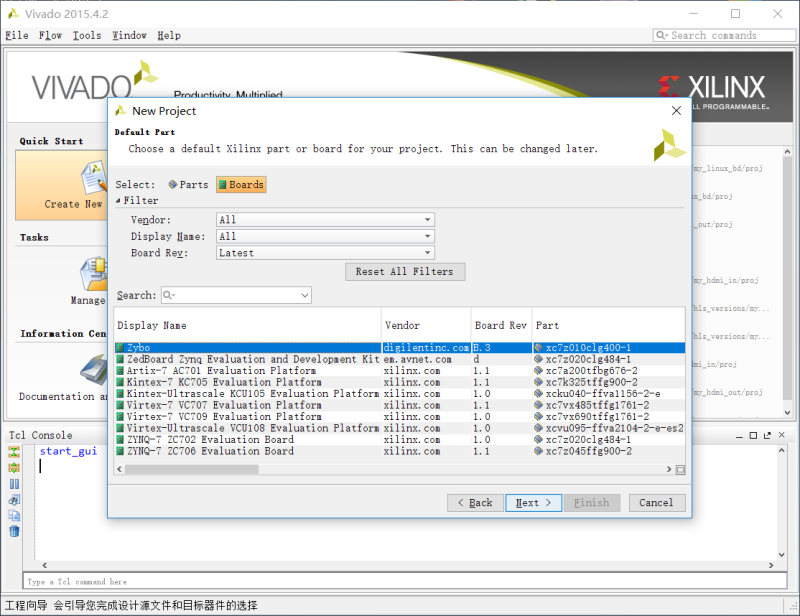

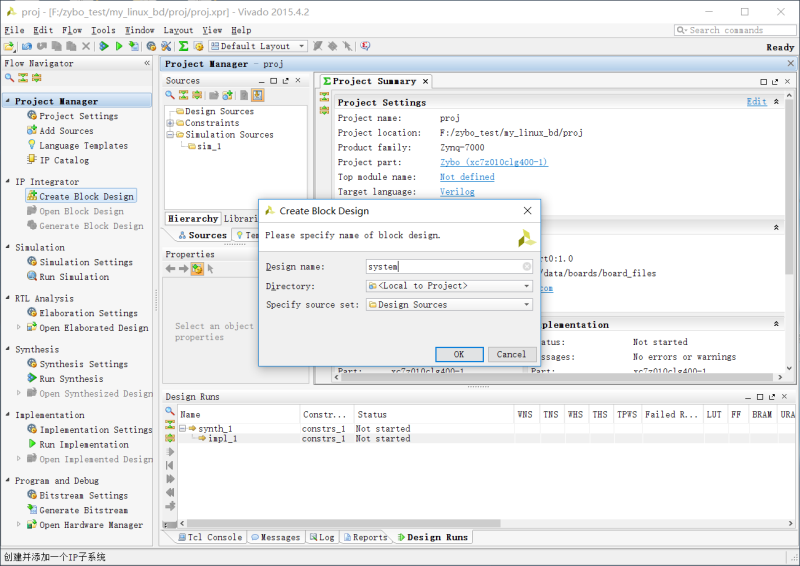

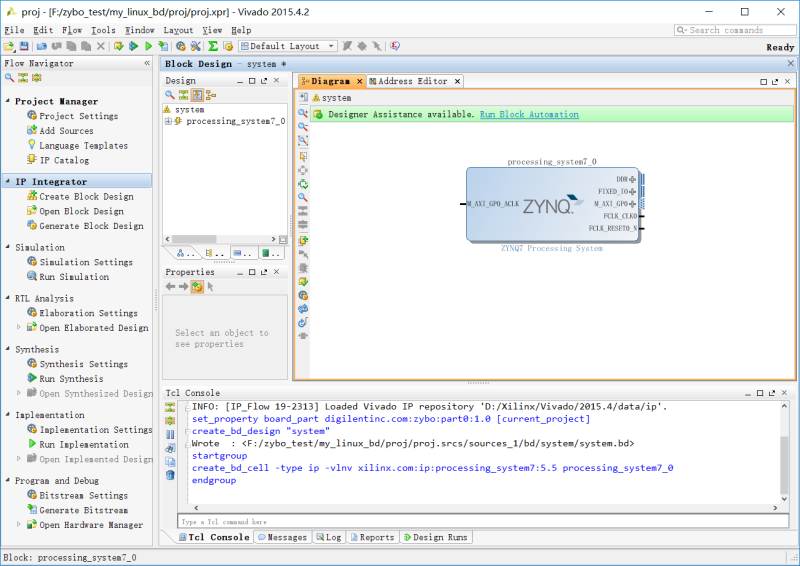

3)创建硬件工程,如下各图(见注释):

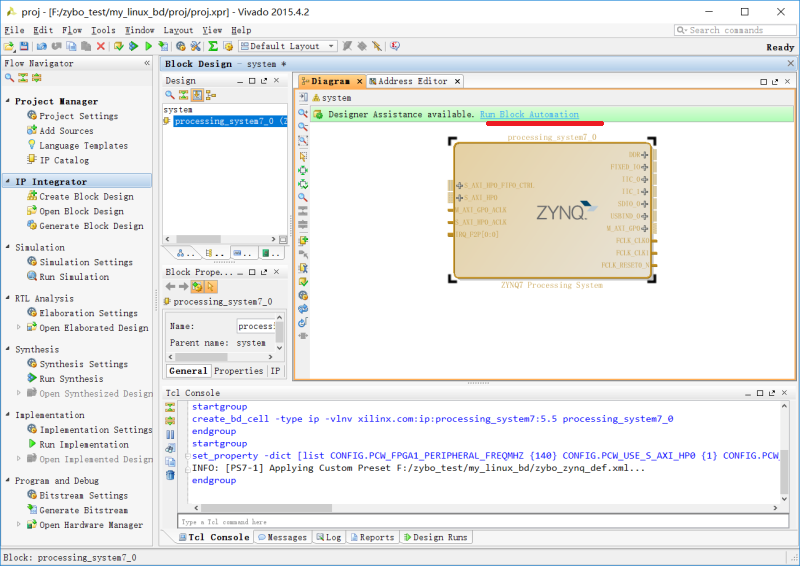

#1 创建名为my_linux_bd的硬件工程

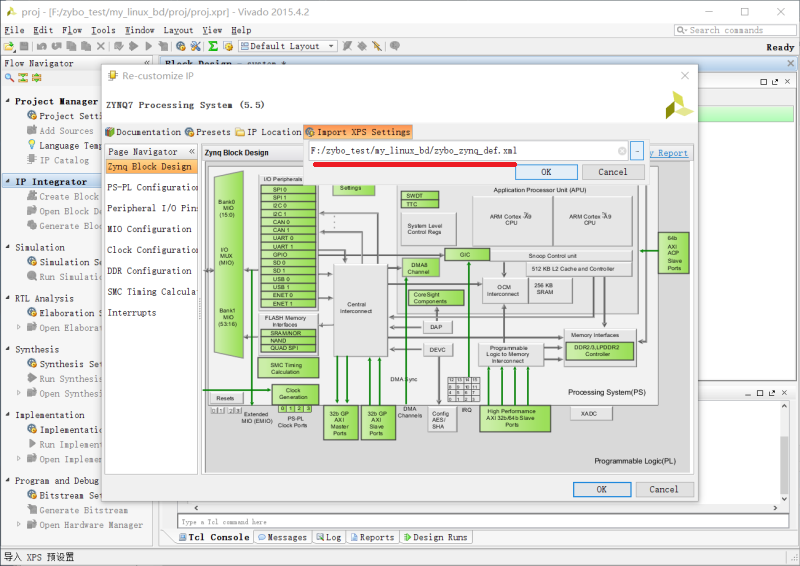

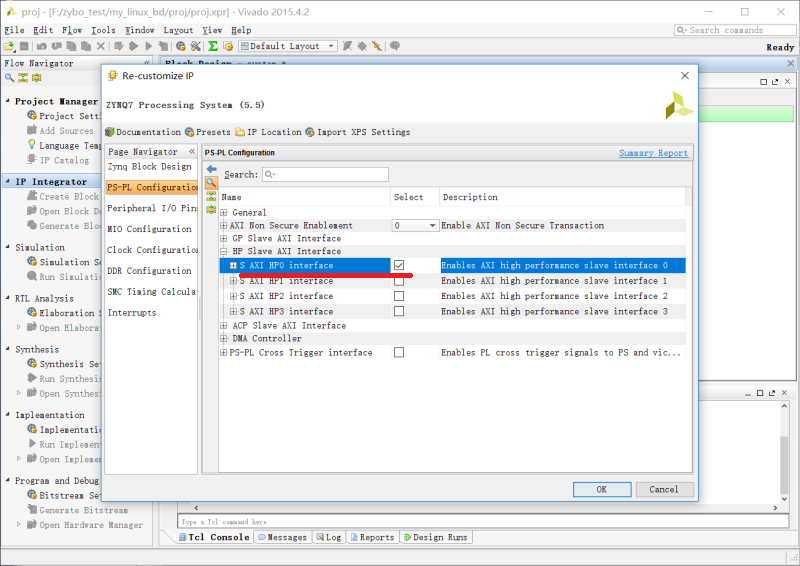

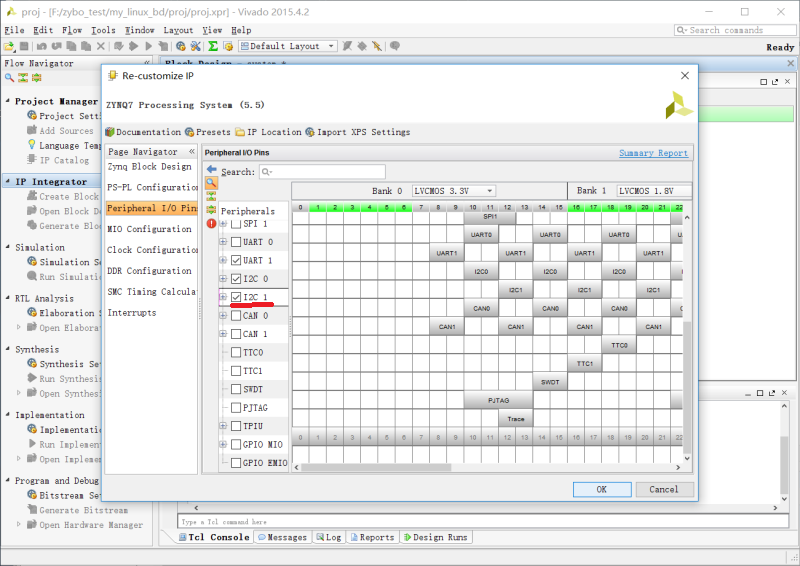

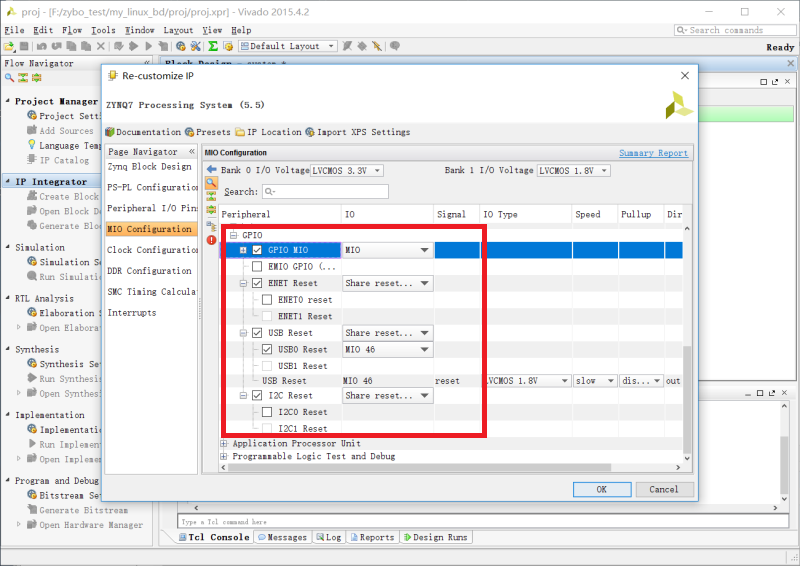

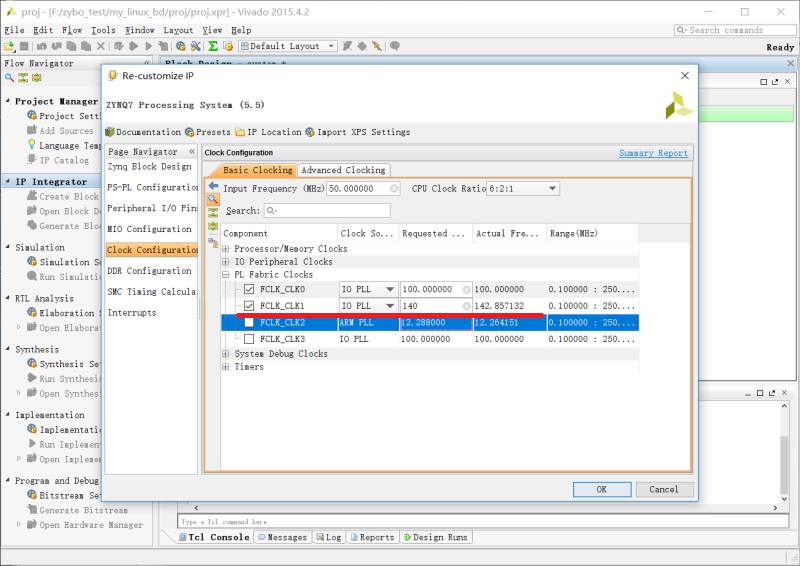

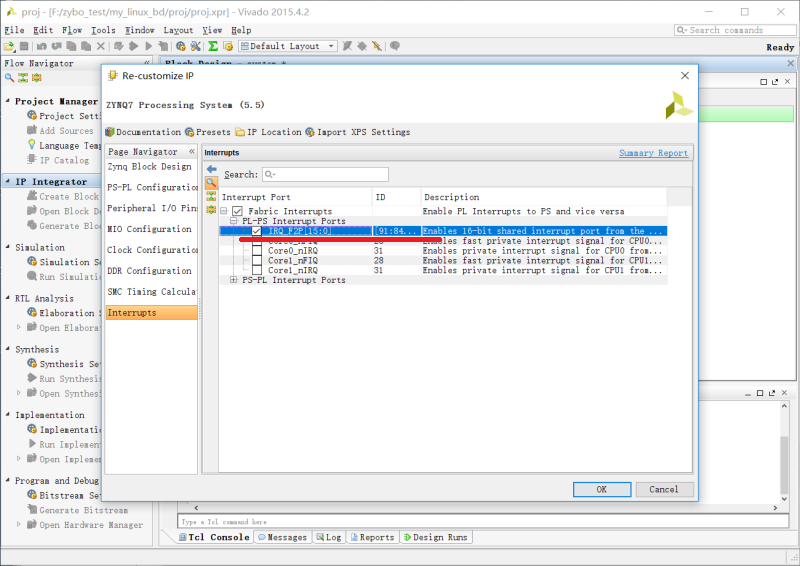

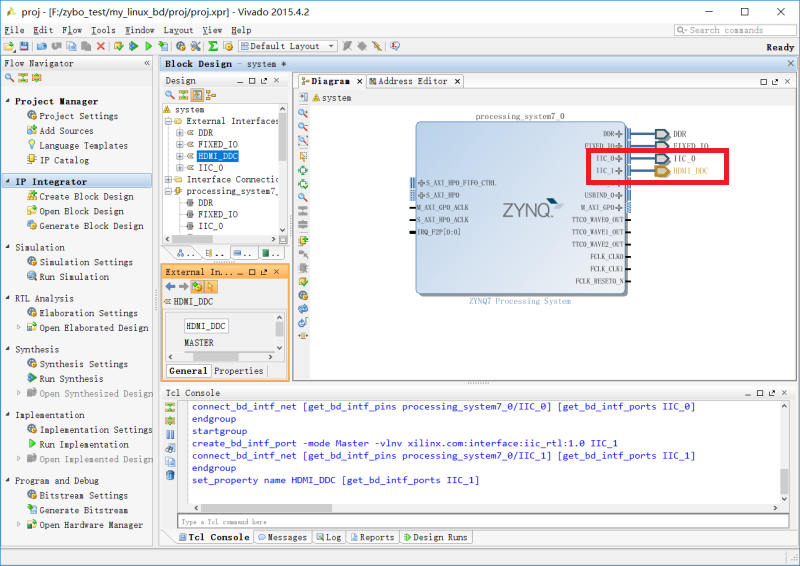

#2 创建名为system的block design顶层文件,添加zynq系统IP,导入zybo板级配置文件,并做必要修改

#3 添加必要的vivado-library(开源IP核[ axi_dynclk_v1_0、rgb2dvi ]及接口[ tmds_v1_0 ])

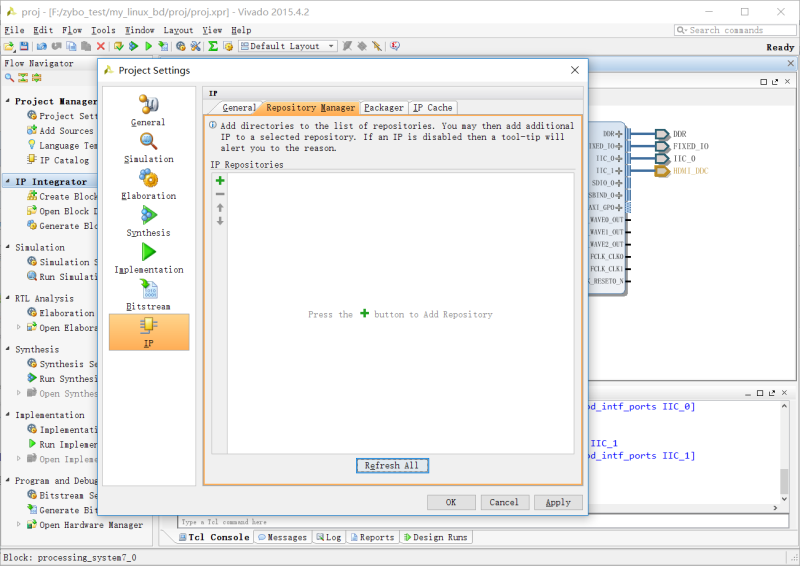

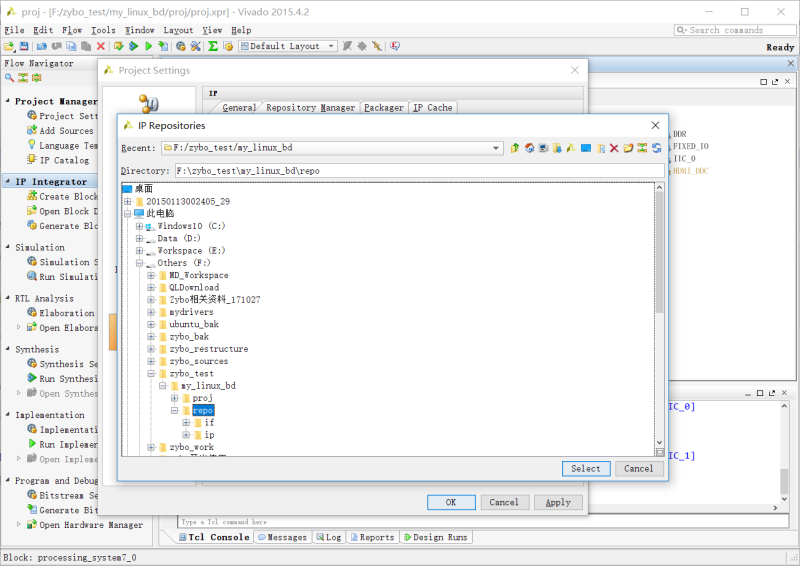

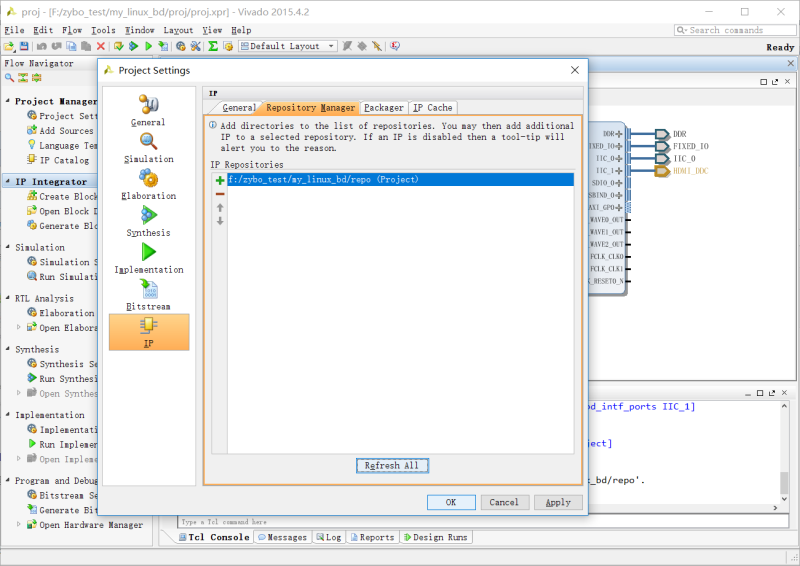

(在工程文件夹内创建名为repo的文件夹,repo文件夹内创建if、ip文件夹,拷贝接口文件tmds_v1_0到if文件夹内,拷贝IP核axi_dynclk_v1_0、rgb2dvi到ip文件夹内,并按下图操作)

(开源vivado-library下载:https://github.com/Digilent/vivado-library)

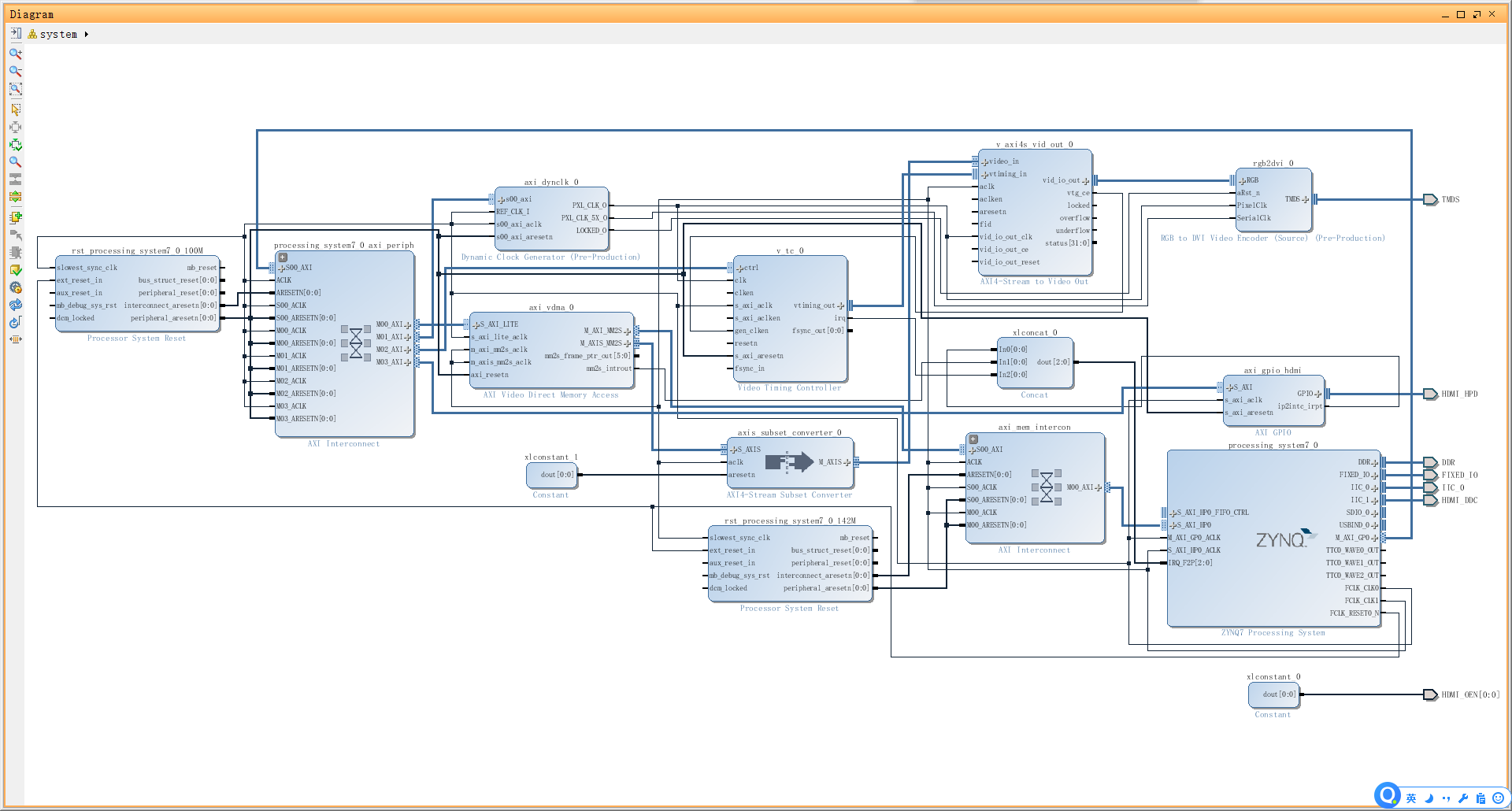

#4 添加IP核:axi_dynclk_v1_0、rgb2dvi、gpio、vdma、vtc、stream2video等IP核,并作布线如下图所示

(布线方法:先手动连接时钟信号线FCLK_CLK0、FCLK_CLK1,然后点击上方的绿色自动布线选项)

其中,关键IP核配置如下:

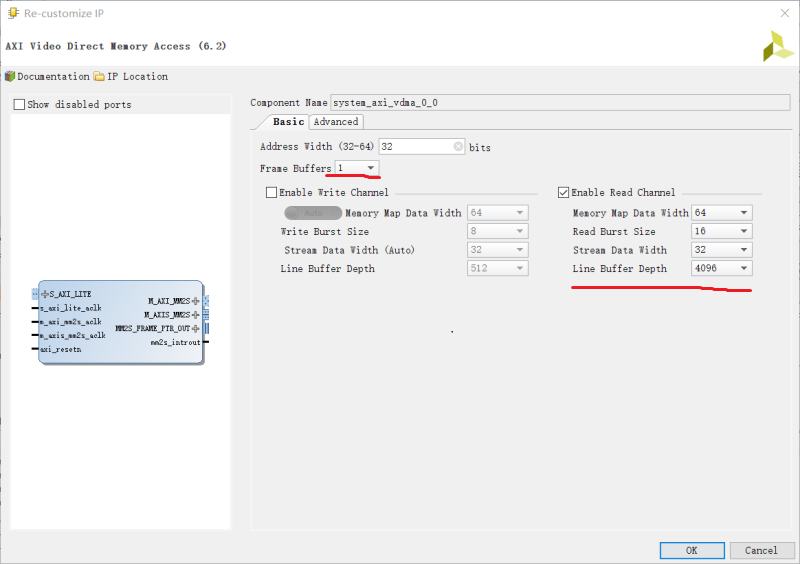

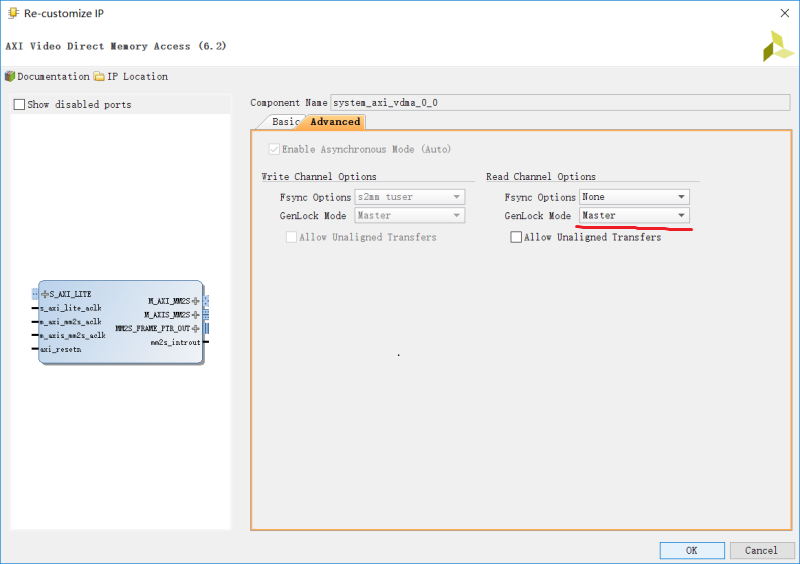

##1 vdma

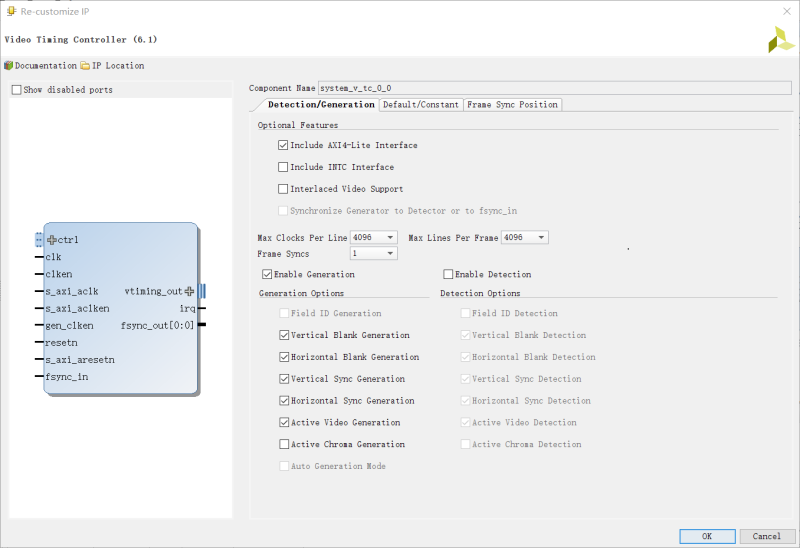

##2 vtc

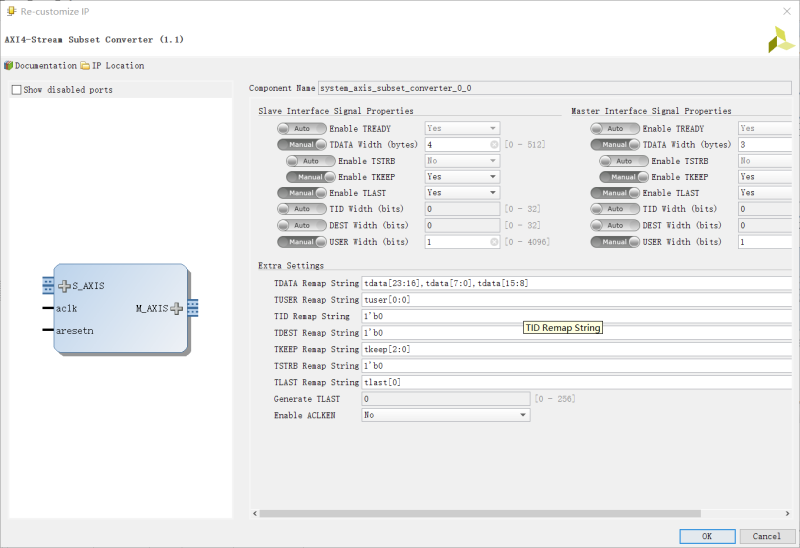

##3 axis_subset_converter

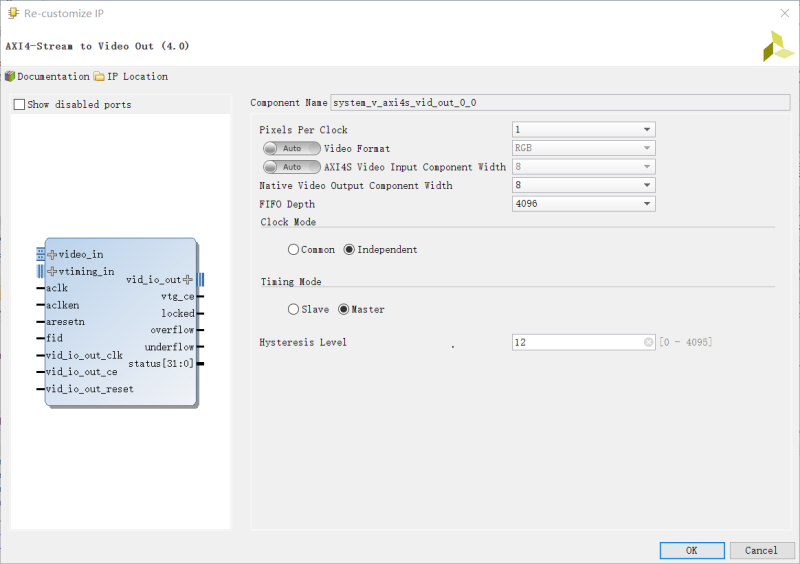

##4 stream2video

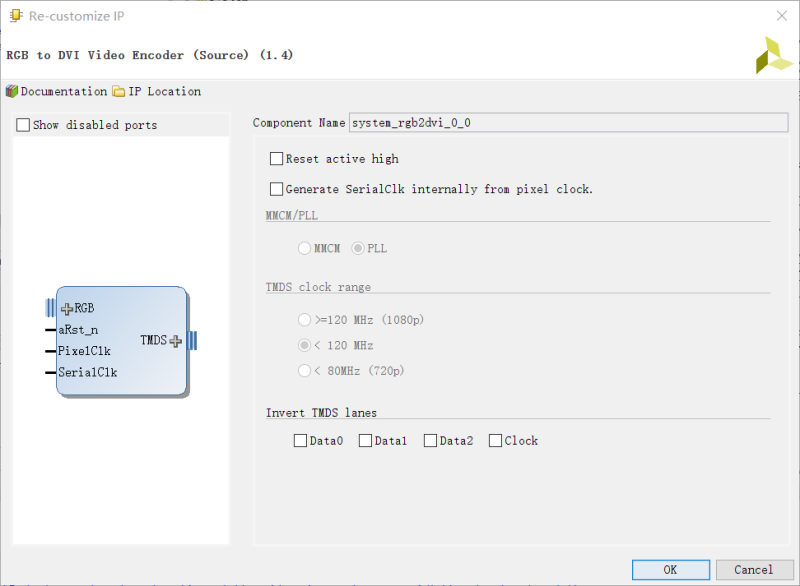

##5 rgb2dvi

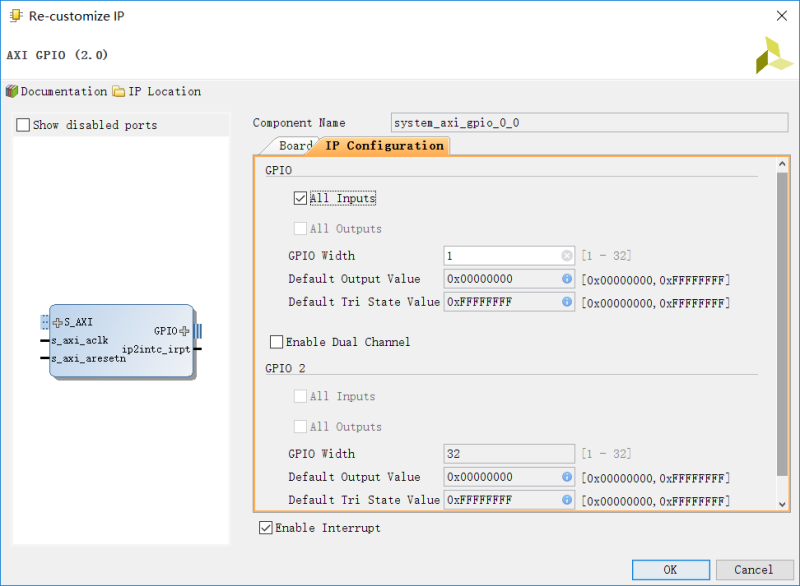

##6 gpio

##7 图中两个常量IP均为一位,数值为1,其一使converter不重置,其二使HDMI_OEN输出为高电平,指示当前hdmi为输出模式

#5 点击“validate design”,验证没有错误后,添加引脚约束文件,修改自ZYBO_Master.xdc

## This file is a general .xdc for the ZYBO Rev B board

## To use it in a project:

## - uncomment the lines corresponding to used pins

## - rename the used signals according to the project ##Audio Codec/external EEPROM IIC bus

#IO_L13P_T2_MRCC_34

set_property PACKAGE_PIN N18 [get_ports iic_0_scl_io]

set_property IOSTANDARD LVCMOS33 [get_ports iic_0_scl_io] #IO_L23P_T3_34

set_property PACKAGE_PIN N17 [get_ports iic_0_sda_io]

set_property IOSTANDARD LVCMOS33 [get_ports iic_0_sda_io] ##HDMI Signals

#IO_L13N_T2_MRCC_35

set_property IOSTANDARD TMDS_33 [get_ports TMDS_clk_n] #IO_L13P_T2_MRCC_35

set_property PACKAGE_PIN H16 [get_ports TMDS_clk_p]

set_property IOSTANDARD TMDS_33 [get_ports TMDS_clk_p] #IO_L4N_T0_35

set_property IOSTANDARD TMDS_33 [get_ports {TMDS_data_n[]}] #IO_L4P_T0_35

set_property PACKAGE_PIN D19 [get_ports {TMDS_data_p[]}]

set_property IOSTANDARD TMDS_33 [get_ports {TMDS_data_p[]}] #IO_L1N_T0_AD0N_35

set_property IOSTANDARD TMDS_33 [get_ports {TMDS_data_n[]}] #IO_L1P_T0_AD0P_35

set_property PACKAGE_PIN C20 [get_ports {TMDS_data_p[]}]

set_property IOSTANDARD TMDS_33 [get_ports {TMDS_data_p[]}] #IO_L2N_T0_AD8N_35

set_property IOSTANDARD TMDS_33 [get_ports {TMDS_data_n[]}] #IO_L2P_T0_AD8P_35

set_property PACKAGE_PIN B19 [get_ports {TMDS_data_p[]}]

set_property IOSTANDARD TMDS_33 [get_ports {TMDS_data_p[]}] #IO_L5P_T0_AD9P_35

set_property PACKAGE_PIN E18 [get_ports {hdmi_hpd_tri_i[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {hdmi_hpd_tri_i[]}] ##IO_L6N_T0_VREF_35

set_property PACKAGE_PIN F17 [get_ports {HDMI_OEN[]}]

set_property IOSTANDARD LVCMOS33 [get_ports {HDMI_OEN[]}] #IO_L16P_T2_35

set_property PACKAGE_PIN G17 [get_ports hdmi_ddc_scl_io]

set_property IOSTANDARD LVCMOS33 [get_ports hdmi_ddc_scl_io] #IO_L16N_T2_35

set_property PACKAGE_PIN G18 [get_ports hdmi_ddc_sda_io]

set_property IOSTANDARD LVCMOS33 [get_ports hdmi_ddc_sda_io]

#6 点击“generate bitstream”,等待生成比特流文件

2、SDK创建的FSBL执行文件fsbl.elf

略。

3、SDK/ubuntu创建的设备树文件system.dts/devicetree.dtb

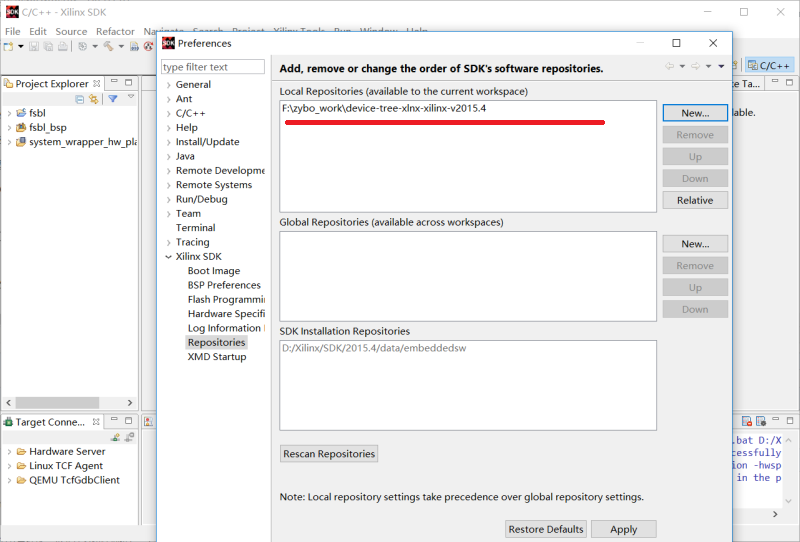

1)下载device_tree配置文件,链接:https://github.com/Xilinx/device-tree-xlnx/releases(注意下载的版本与vivado版本匹配)

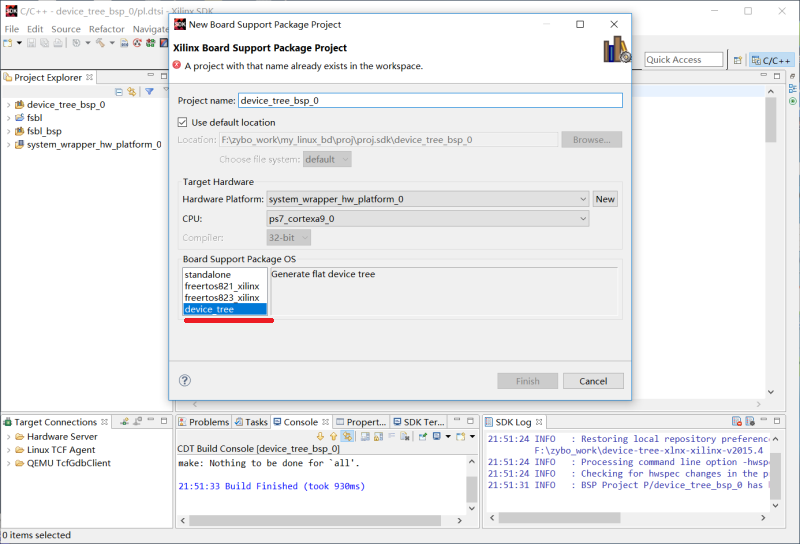

2)SDK添加device_tree配置文件

Xilinx Tools -> Repositories -> New

3)SDK创建device_tree工程,生成dts文件

File -> New -> Board Support Package

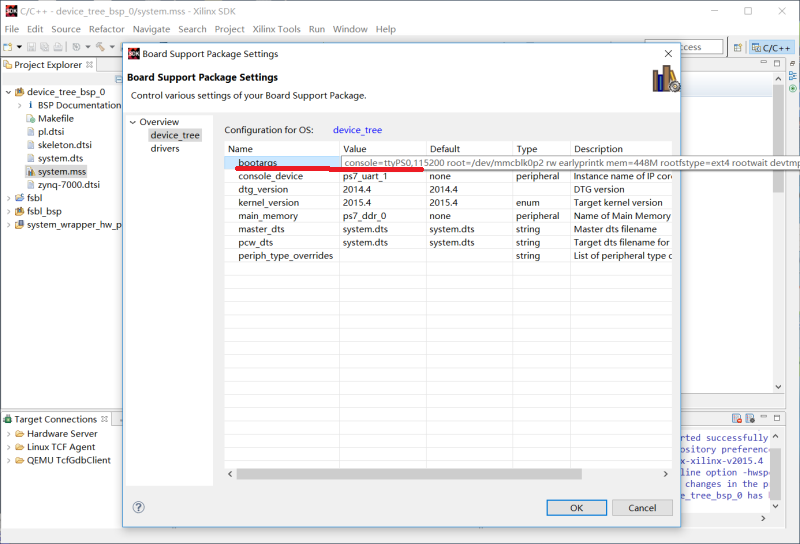

4)bootagrs参数设定

(e.g. console=ttyPS0,115200 root=/dev/mmcblk0p2 rw earlyprintk rootfstype=ext4 rootwait devtmpfs.mount=1)

5)[重要] 根据相关硬件做出修改,如下:

#1 添加usb驱动配置

在pl.dtsi文件中最后一个分号“ } ; ”前添加:

/*add for usb0*/

usb_phy_0: usb_phy {

compatible = "usb-nop-xceiv";

#phy-cells = <0x0>;

};

并在zynq-7000.dtsi文件中,usb0标签的最后一个分号“ } ; ”前添加:

usb-phy = <&usb_phy_0>;//add for usb0

#2 添加hdmi驱动配置

在pl.dtsi文件中,amba_pl标签内作如下修改:

amba_pl: amba_pl {

#address-cells = <>;

#size-cells = <>;

compatible = "simple-bus";

ranges ;

axi_dynclk_0: axi_dynclk@43c00000 {

#clock-cells = <0x0>;//add

compatible = "digilent,axi-dynclk";//change

reg = <0x43c00000 0x10000>;

xlnx,s00-axi-addr-width = <0x5>;

xlnx,s00-axi-data-width = <0x20>;

clocks = <&clkc 0xf>;//add, 0xf不能删掉

};

axi_gpio_hdmi: gpio@ {

#gpio-cells = <>;

compatible = "xlnx,xps-gpio-1.00.a";

gpio-controller ;

interrupt-parent = <&intc>;

interrupts = < >;

reg = <0x41200000 0x10000>;

xlnx,all-inputs = <0x1>;

xlnx,all-inputs- = <0x0>;

xlnx,all-outputs = <0x0>;

xlnx,all-outputs- = <0x0>;

xlnx,dout-default = <0x00000000>;

xlnx,dout-default- = <0x00000000>;

xlnx,gpio-width = <0x1>;

xlnx,gpio2-width = <0x20>;

xlnx,interrupt-present = <0x1>;

xlnx,is-dual = <0x0>;

xlnx,tri-default = <0xFFFFFFFF>;

xlnx,tri-default- = <0xFFFFFFFF>;

};

axi_vdma_0: dma@ {

#dma-cells = <>;

compatible = "xlnx,axi-vdma-1.00.a";

interrupt-parent = <&intc>;

interrupts = < >;

reg = <0x43000000 0x10000>;

//xlnx,flush-fsync = <0x1>;//change

xlnx,num-fstores = <0x1>;

dma-channel@ {

compatible = "xlnx,axi-vdma-mm2s-channel";

interrupts = < >;

clocks = <&clkc>;//add

clock-names = "axis";//add

xlnx,datawidth = <0x20>;

xlnx,device-id = <0x0>;

};

};

v_tc_0: v_tc@43c10000 {

compatible = "xlnx,v-tc-5.01.a";//change

interrupt-parent = <&intc>;

interrupts = < >;

reg = <0x43c10000 0x10000>;

xlnx,det-achroma-en = <0x0>;

xlnx,det-avideo-en = <0x1>;

xlnx,det-fieldid-en = <0x0>;

xlnx,det-hblank-en = <0x1>;

xlnx,det-hsync-en = <0x1>;

xlnx,det-vblank-en = <0x1>;

xlnx,det-vsync-en = <0x1>;

xlnx,detect-en = <0x0>;

xlnx,fsync-hstart0 = <0x0>;

xlnx,fsync-hstart1 = <0x0>;

xlnx,fsync-hstart10 = <0x0>;

xlnx,fsync-hstart11 = <0x0>;

xlnx,fsync-hstart12 = <0x0>;

xlnx,fsync-hstart13 = <0x0>;

xlnx,fsync-hstart14 = <0x0>;

xlnx,fsync-hstart15 = <0x0>;

xlnx,fsync-hstart2 = <0x0>;

xlnx,fsync-hstart3 = <0x0>;

xlnx,fsync-hstart4 = <0x0>;

xlnx,fsync-hstart5 = <0x0>;

xlnx,fsync-hstart6 = <0x0>;

xlnx,fsync-hstart7 = <0x0>;

xlnx,fsync-hstart8 = <0x0>;

xlnx,fsync-hstart9 = <0x0>;

xlnx,fsync-vstart0 = <0x0>;

xlnx,fsync-vstart1 = <0x0>;

xlnx,fsync-vstart10 = <0x0>;

xlnx,fsync-vstart11 = <0x0>;

xlnx,fsync-vstart12 = <0x0>;

xlnx,fsync-vstart13 = <0x0>;

xlnx,fsync-vstart14 = <0x0>;

xlnx,fsync-vstart15 = <0x0>;

xlnx,fsync-vstart2 = <0x0>;

xlnx,fsync-vstart3 = <0x0>;

xlnx,fsync-vstart4 = <0x0>;

xlnx,fsync-vstart5 = <0x0>;

xlnx,fsync-vstart6 = <0x0>;

xlnx,fsync-vstart7 = <0x0>;

xlnx,fsync-vstart8 = <0x0>;

xlnx,fsync-vstart9 = <0x0>;

xlnx,gen-achroma-en = <0x0>;

xlnx,gen-achroma-polarity = <0x1>;

xlnx,gen-auto-switch = <0x0>;

xlnx,gen-avideo-en = <0x1>;

xlnx,gen-avideo-polarity = <0x1>;

xlnx,gen-cparity = <0x0>;

xlnx,gen-f0-vblank-hend = <0x500>;

xlnx,gen-f0-vblank-hstart = <0x500>;

xlnx,gen-f0-vframe-size = <0x2ee>;

xlnx,gen-f0-vsync-hend = <0x500>;

xlnx,gen-f0-vsync-hstart = <0x500>;

xlnx,gen-f0-vsync-vend = <0x2d9>;

xlnx,gen-f0-vsync-vstart = <0x2d4>;

xlnx,gen-f1-vblank-hend = <0x500>;

xlnx,gen-f1-vblank-hstart = <0x500>;

xlnx,gen-f1-vframe-size = <0x2ee>;

xlnx,gen-f1-vsync-hend = <0x500>;

xlnx,gen-f1-vsync-hstart = <0x500>;

xlnx,gen-f1-vsync-vend = <0x2d9>;

xlnx,gen-f1-vsync-vstart = <0x2d4>;

xlnx,gen-fieldid-en = <0x0>;

xlnx,gen-fieldid-polarity = <0x1>;

xlnx,gen-hactive-size = <0x500>;

xlnx,gen-hblank-en = <0x1>;

xlnx,gen-hblank-polarity = <0x1>;

xlnx,gen-hframe-size = <0x672>;

xlnx,gen-hsync-en = <0x1>;

xlnx,gen-hsync-end = <0x596>;

xlnx,gen-hsync-polarity = <0x1>;

xlnx,gen-hsync-start = <0x56e>;

xlnx,gen-interlaced = <0x0>;

xlnx,gen-vactive-size = <0x2d0>;

xlnx,gen-vblank-en = <0x1>;

xlnx,gen-vblank-polarity = <0x1>;

xlnx,gen-video-format = <0x2>;

xlnx,gen-vsync-en = <0x1>;

xlnx,gen-vsync-polarity = <0x1>;

xlnx,generate-en = <0x1>;

xlnx,has-axi4-lite = <0x1>;

xlnx,has-intc-if = <0x0>;

xlnx,interlace-en = <0x0>;

xlnx,max-lines = <0x1000>;

xlnx,max-pixels = <0x1000>;

xlnx,num-fsyncs = <0x1>;

xlnx,sync-en = <0x0>;

};

/*add for vga_hdmi_encoder*/

digilent_encoder_0: digilent_encoder {

compatible = "dglnt,drm-encoder";

dglnt,edid-i2c = <&i2c1>;

};

/*add for drm*/

xilinx_drm_0: xilinx_drm {

compatible = "xlnx,drm";

xlnx,vtc = <&v_tc_0>;

xlnx,connector-type = "HDMIA";

xlnx,encoder-slave = <&digilent_encoder_0>;

clocks = <&axi_dynclk_0>;

dglnt,edid-i2c = <&i2c1>;

planes {

xlnx,pixel-format = "xrgb8888";

plane0 {

dmas = <&axi_vdma_0 >;//0不能删掉

dma-names = "dma";

};

};

};

};

6)修改后,工程会重新编译,复制device_tree_dsp_0整个文件夹到ubuntu系统下,执行以下命令生成设备树文件devicetree.dtb

cd device_tree_dsp_0

dtc -I dts -O dtb ./system.dts -o devicetree.dtb

(前提:安装dtc工具,或从Linux kernel源码中拷贝dtc执行文件出来)

(安装命令:sudo apt-get install device-tree-compile)

二、软件平台搭建

[目标文件:启动引导程序u-boot.elf、Linux内核文件uImage、文件系统linaro]

[待续...]

官方教程链接:

ZYBOt Guide [Reference.Digilentinc]

https://reference.digilentinc.com/learn/programmable-logic/tutorials/zybo-zybot-guide/start

Zybot - Getting Started Guide and Source Code: 8 Steps

http://www.instructables.com/id/Zybot-Getting-Started-Guide/

搭建好了硬件平台、Linaro软件桌面系统,下一步便是开发应用程序(用到Qt与OpenCV),然后交叉编译后移植到Linaro系统中运行。但此时又发生了一个重大问题:交叉编译后的应用程序不能运行,涉及到Linaro系统编译时所用的编译器版本问题、2012年后Linaro系统加载程序的路径及名称问题,以至于需要重装交叉编译链、重新交叉编译Qt与OpenCV等,下一篇文章再续。

Zynq7000开发系列-7(在Zybo上运行Linaro桌面系统)的更多相关文章

- Zynq7000开发系列-2(VMware与Ubuntu安装使用)

一.前言 在嵌入式开发中,是无法避免使用Linux系统的,因为在开发之前必须先搭建起交叉编译环境,而后关于Bootloader.Linux Kernel的裁剪移植,File system的制作,底层驱 ...

- nw.js桌面软件开发系列 第0.1节 HTML5和桌面软件开发的碰撞

第0.1节 HTML5和桌面软件开发的碰撞 当我们谈论桌面软件开发技术的时候,你会想到什么?如果不对技术本身进行更为深入的探讨,在我的世界里,有这么多技术概念可以被罗列出来(请原谅我本质上是一个Win ...

- 树莓派开发系列教程2--树莓派3B介绍及系统烧写、基本配置

注意:树莓派系列的3篇文章里面的图片因为博客转移过程丢失了,非常抱歉 前言 树莓派系列里涉及到需要额外电脑来协助处理的部分(如烧写系统,远程访问等等),统一在运行着Ubuntu15系统的mac air ...

- iOS开发——运行时OC篇&使用运行时获取系统的属性:使用自己的手势修改系统自带的手势

使用运行时获取系统的属性:使用自己的手势修改系统自带的手势 有的时候我需要实现一个功能,但是没有想到很好的方法或者想到了方法只是那个方法实现起来太麻烦,一或者确实为了装逼,我们就会想到iOS开发中最牛 ...

- Zynq7000开发系列-3(Xilinx交叉编译环境搭建)

一.前言 上一篇文章说了,在开发之前必须先搭建起交叉编译环境,于是这里我们就介绍一下环境的搭建过程. 其实在所安装的Vivado HLx 2016.4中就包含了Xilinx SDK,在该SDK上即可开 ...

- Zynq7000开发系列-6(QT开发环境搭建:Ubuntu、Zynq)

操作系统:Ubuntu14.04.5 LTS 64bit Qt:Qt 5.4.2 (qt-opensource-linux-x64-5.4.2.run.qt-everywhere-opensource ...

- Zynq7000开发系列-4(新:Xilinx交叉编译环境搭建)

一.前言 本来上一篇文章已经讲了Xilinx交叉编译环境的搭建,但是我在后续的使用中发现:使用2011年版本的交叉编译链编译OpenCV 3.1.0时出现错误: 网络搜索一番,查明是交叉编译链的问题 ...

- Zynq7000开发系列-5(OpenCV开发环境搭建:Ubuntu、Zynq)

操作系统:Ubuntu14.04.5 LTS 64bit OpenCV:OpenCV 3.1.0.opencv_contrib gcc:gcc version 4.8.4 (Ubuntu 4.8.4- ...

- Zynq7000开发系列-1(Vivado HLx 2016.4下载及安装)

一.下载 1.访问Xilinx官方网站:www.xilinx.com,注册帐号并完善个人信息 2.点击以下选项进入下载页面:Support -> Downloads & Licensin ...

随机推荐

- contentprovider基础

程序启动后,只要再manifest当中注册上,就会执行PersonProvider()创建一个对象

- Python pip源,解决安装慢的问题

经常在使用Python的时候需要安装各种模块,而pip是很强大的模块安装工具,但是由于国外官方pypi经常被墙,导致不可用,所以我们最好是将自己使用的pip源更换一下,这样就能解决被墙导致的装不上库的 ...

- Discuz/X3.1去掉标题中的Powered by Discuz!以及解决首页标题后的"-"

虽然不提倡大家去掉版权信息,但是在实际操作的时候还是去掉,毕竟每个页面标题最后面出现”Powered by Discuz!“会显得页面标题比较冗长. 经过本人的实践,论坛里也有操作方法,不过那个操作方 ...

- 【C++】私有数据成员不能用对象去访问吗

首先,必须清楚的是private和public限定的是类而不是对象.因此,在成员函数中访问同类对象的私有成员是完全可以的. 所以,某些教材上所说的“私有数据成员不能用对象去访问”是欠妥当的. 比如,如 ...

- BZOJ_2208_[Jsoi2010]连通数_强连通分量+拓扑排序+手写bitset

BZOJ_2208_[Jsoi2010]连通数_强连通分量+拓扑排序+手写bitset Description Input 输入数据第一行是图顶点的数量,一个正整数N. 接下来N行,每行N个字符.第i ...

- JavaWeb----文件的上传和下载

一.开发环境搭建 创建一个FileUploadAndDownLoad项目,加入Apache的commons-fileupload文件上传组件的相关Jar包,如下图所示: 二.实现文件上传 2.1.文件 ...

- mybatis 优缺点和适用场合

MyBatis 是支持定制化 SQL.存储过程以及高级映射的优秀的持久层框架, MyBatis 避免了几乎所有的 JDBC 代码和手动设置参数以及获取结果集.MyBatis 可以对配置和原生Map使用 ...

- Visual Studio Ultimate 2013 下载地址

VS2013_RTM_ULT_CHS.iso 文件大小:2.87G 百度网盘下载地址: http://pan.baidu.com/s/1bn4gavX 微软官网下载地址: http://downloa ...

- IIS 部署 SSAS

转自:http://blog.csdn.net/jinjazz/article/details/4058368 1.首先到分析服务器的SQLServer安装目录中找到如下目录和文件 2.然后为IIS建 ...

- OutputDebugString()输出调试的使用