FPGA-HPS

最近在做DE1的图像方面实验,用到了HPS,所以简要谈一谈什么是HPS.

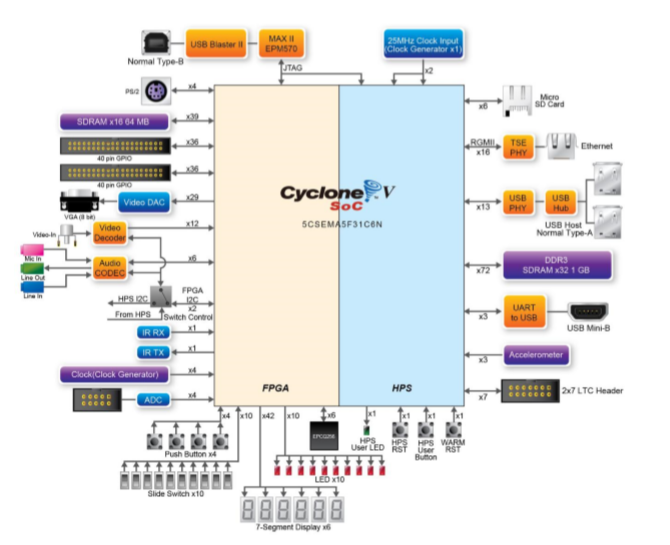

由图可知,DE1的板子就是有fpga+hps组成的;

参考自:http://bbs.eeworld.com.cn/thread-454766-1-1.html

1、HPS:Hard processor system 字面意思就是硬件处理器系统,应该指的是和arm核相连的硬件接口。

2、包括以下内容:

1)Single or dual-core ARM Cortex-A9 MPCore processor-up to 800 MHz maximum frequency with support for symmetric and asymmetric multiprocessing

支持一个或2个ARM Cortex-A9,频率最大能达到800MHz,两个处理器还可以设置成不同的处理速率,这点不知道有什么好处。

2)Interface peripherals —10/100/1000 Ethernet media access control (EMAC), USB 2.0

On-The-GO (OTG) controller, quad serial peripheral interface (QSPI) flash controller,

NAND flash controller, Secure Digital/MultiMediaCard (SD/MMC) controller, UART,

controller area network (CAN), serial peripheral interface (SPI), I2C interface, and

up to 85 HPS GPIO interfaces

接口外设,这个比较好理解,都是常见的arm接口,网口、USB,SPI等等

3)System peripherals —general-purpose timers, watchdog timers, direct memory access

(DMA) controller, FPGA configuration manager, and clock and reset managers

系统外设,这个也比较好理解,就是系统能不运行,而不和外界打交道的,比如定时器,看门狗,DMA控制器等

4) On-chip RAM and boot ROM

片上的RAM和POM,这个还不知道是什么玩意

5)HPS –FPGA bridges —include the FPGA-to-HPS, HPS-to-FPGA, and lightweight

HPS-to-FPGA bridges that allow the FPGA fabric to issue transactions to slaves in

the HPS, and vice versa

这个是比较关键的地方,HPS-FPGA之间的沟通机制

6)FPGA-to-HPS SDRAM controller subsystem —provides a configurable interface to

the multiport front end (MPFE) of the HPS SDRAM controller

接到HPS的SDRAM控制器,应该是和ARM的存储资源有联系

7)ARM CoreSight™ JTAG debug access port, trace port, and on-chip trace storage

这应该说的是调试接口和调试机制

以前的简要介绍

https://www.cnblogs.com/fcfc940503/p/10438350.html

FPGA-HPS的更多相关文章

- 可编程逻辑(FPGA)与硬核处理器(HPS)之间互联的结构

本周我想进一步探究可编程逻辑(FPGA)与硬核处理器(HPS)之间互联的结构.我发现了三种主要方式,它们是如何映射并处理通信的,哪些组件需要管控时序并且有访问权限. AXI Bridge 为了能够实现 ...

- 通过HPS控制FPGA端的GPIO

该笔记主要记录HPS端如何通过AXI Bridge控制FPGA端口的GPIO,主要是如何操作FPGA侧的Led 1.AXI Bridge AXIB主要包括H2FB.F2HB.LWH2F ...

- 通过HPS控制FPGA的GPIO

1.学习目的 本例程主要是让 SoC FPGA 初学者了解 HPS/ARM 如何跟 FPGA 交互.“My First HPS-FPGA”工程演示了实现方法的细节.这个工程包括 Quartus II ...

- 关于HPS和FPGA之间的桥接学习笔记一

为了实现FPGA和HPS之间的存储器共享和数据传输,Altera SoC FPGA提供了两种方式用于FPGA和HPS通信.分别是FPGA to SDRAM和AXI bridge. FPGA to SD ...

- HPS端如何通过AXI Bridge控制FPGA端口的GPIO

该笔记主要记录HPS端如何通过AXI Bridge控制FPGA端口的GPIO,主要是如何操作FPGA侧的Led 1.AXI Bridge AXIB主要包括H2FB.F2HB.LWH2F ...

- altera soc体验之旅 FPGA与ARM的窃窃私语

喜大普奔,公司要评估用SOC做产品,我就自然而然的被安排了学习和评估的工作,于是,每天的工作就是开始研究soc了.其实,只要能静下心来学习,一切都还是能够弄出来的. 以前像个无头苍蝇一样到处乱撞, ...

- FPGA在其他领域的应用(一)

测试和测量应用: 测试需要是所有细分市场的要求.无论是终端市场,所有产品在运到最终客户之前都必须进行测试.这动态地驱动测试和测量领域的普遍性质,其中包括下面的种类和分段: 通信测试: 无线测试仪 (W ...

- FPGA开发随笔汇总

点击标题即可进入相关随笔. DE-SOC开发板VrilogHDL开发相关部分: (本过程需要Verilog HDL 的基本语言基础) 1.FPGA的发展史及FPGA 的基础架构 2.首先看一下友晶DE ...

- Altera FPGA SoC搭建步骤

Altera SoC 官方搭建指南: https://rocketboards.org/foswiki/Documentation/EmbeddedLinuxBeginnerSGuide 官方文档中除 ...

随机推荐

- idea基于spring boot的依赖分开打包

idea版本为2018.3.3 1.在菜单栏点击如图所示图标 Project Structure: 2.选择左侧菜单Artificial,然后在右侧点击 + 号按钮,在弹出的菜单中选择JAR -> ...

- 《深入理解java虚拟机》读书笔记四——第五章

第五章 调优案例分析与实战

- 想要学好Git,应该掌握哪些基础知识?

说到Git,作为程序员的你,在项目开发中一定会使用到或将来也一定会使用到的,但是我相信,很多在使用Git的人,都只是停留一些简单的操作上,比如提交(commit).拉取(pull).推送(push). ...

- 论Mac与windows的STS下的路径问题

mac下的 <!-- javaBean生成在哪里 --> <javaModelGenerator targetPackage="com.atcrowdfunding.bea ...

- C++-POJ2777-Count Color[线段树][lazy标记][区间修改]

分析:https://www.bilibili.com/read/cv4777102 #include <cstdio> #include <algorithm> using ...

- HTML的学习结构

HTML的学习结构 HTML的背景 HTML的创建 HTML的网页基本结构 HTML的基本标签 HTML的图像标签 HTML的链接标签 HTML的列表标签和表格标签 HTML的媒体元素(视频+音频) ...

- OpenGL 编程指南 (2)

1.OpenGL对共享的边有严格的规定:1)共享边上的像素因为同事被两者所覆盖,因此不可能不受到光照计算的影响: 2)共享边上的像素值,不可能受到多于一个三角形的光照计算的影响. 2.多边形存在正面与 ...

- Ubuntu18.04 一条命令安装caffe问题

由于caffe安装坑很多,而且caffe框架很久不更新了,微调对框架影响不大,所以对与ubuntu18.04在caffe官网提供了一条命令安装,避免很多踩坑痛苦. CPU的一条命令安装: sudo a ...

- 打表法fffff

打表法: 打表前先运行一下 看一看速度 优化: O3 #pragma GCC optimize(3,"Ofast","inline") O2 #pragma ...

- ICPC2019 亚洲区域赛 南京站

蒟蒻终于打完了人生的第一场ICPC了. 终榜去星后rank36,AG,和AU差几十罚时了. 虽有遗憾但总体也是正常发挥了. 不愿再去对比赛做什么回顾,甚至很不愿去想.很多题已经在能力之外,即便是平常熟 ...