第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。

涉及到AXI BRAM Controller 和 Block Memery Generator等IP的使用。

本系列文章尽可能的让每一个实验都相对独立,过程尽可能保证完整性,保证实验的可重现性。 但是用到的模块或者IP的具体作用和用法不保证都重复详细的介绍。

本文所使用的开发板是Miz702 PC 开发环境版本:Vivado 2015.4 Xilinx SDK 2015.4

12.0本章难度系数★★☆☆☆☆☆

12.1 搭建硬件工程

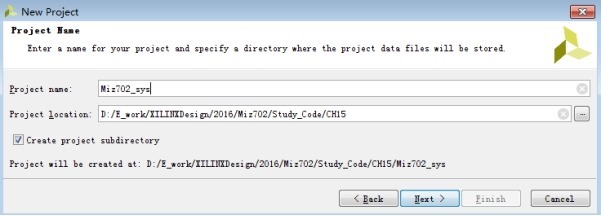

Step1:新建一个名为为Miz702_sys的工程

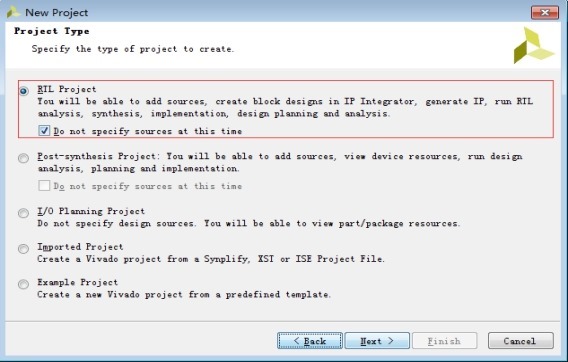

Step2:选择RTL Project 勾选Do not specify source at this time

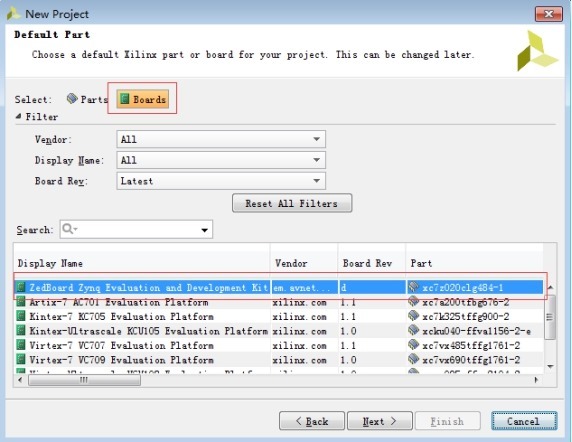

Step3:由于Miz702兼容zedboard 因此选择zedboard开发包

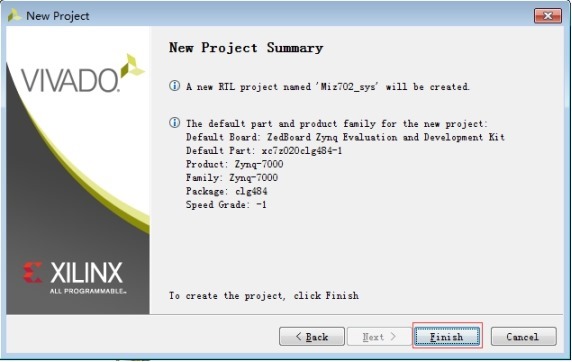

Step4:单击Finish

12.2使用IP Integrator创建硬件系统

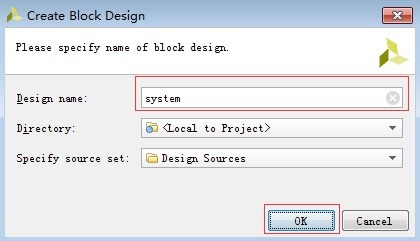

Step1:单击Create Block Design

Step2:输入system

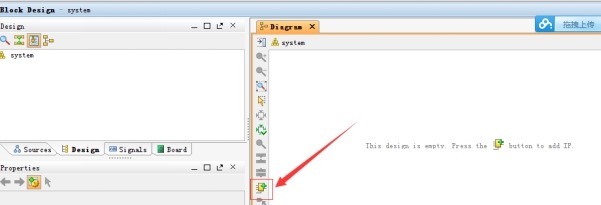

Step3:单击下图中 添加IP按钮

添加IP按钮

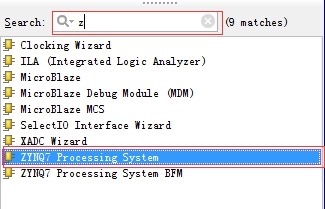

Step4:搜素单词z选择ZYNQ7 Processing System,然后双击

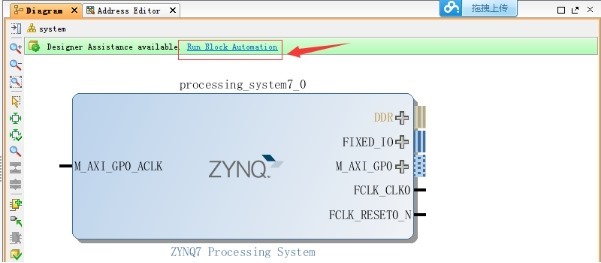

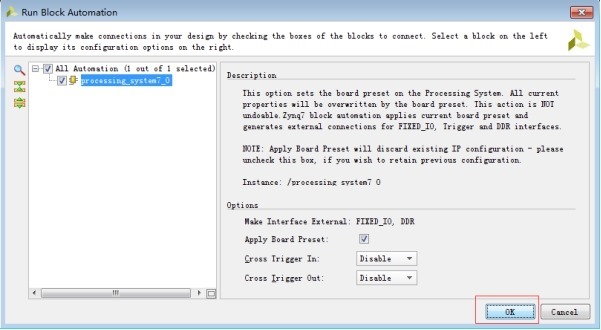

Step5:添加进来了ZYNQ CPU IP,然后单击Run Block Automation

Step6:直接单击OK

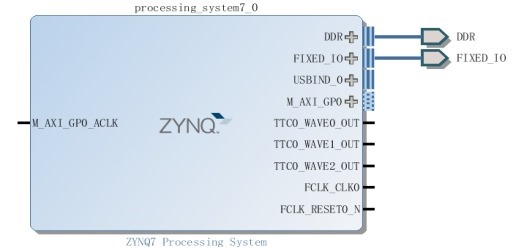

Step7:在你点击了OK后,你会发现DDR以及FICED_IO自劢的延伸出来。

Step8:连线的作用就是把PS的时钟可以接入PL部分,当然这里我们暂时用不到PL部分的资源。在Block文件中,我们迚行连线,将鼠标放在引脚处,鼠标变成铅笔后迚行拖拽,连线如下图所示:

Step9:双击 ZYNQ,打开Re-customize IP对话框,在PL-PS Configuration下,选中 GP0和GP1然后 点击ok

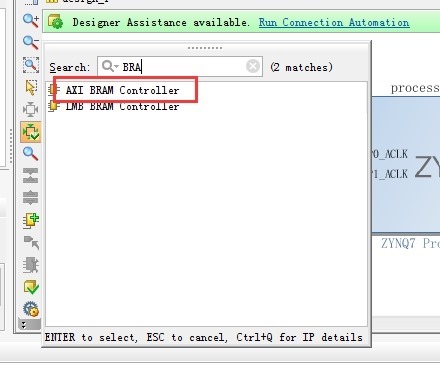

Step10:点击,Add IP,连续添加两个 AXI BRAM Controller

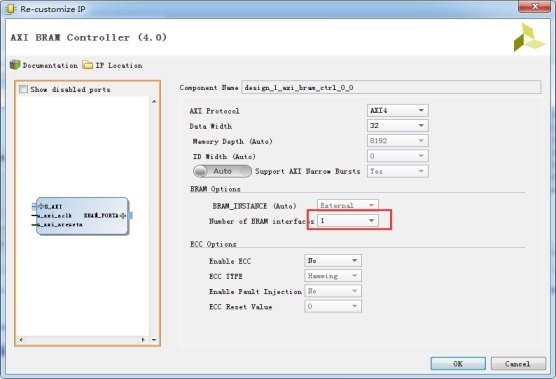

Step11:分别双击AXI BRAM Controller模块,把number of BRAM interfaces 全部修改成1

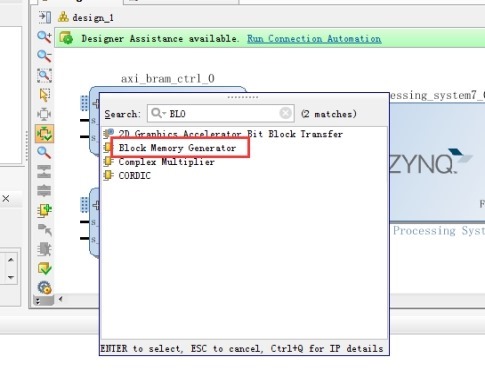

Step12:点击ADD IP,添加Block Memory Generator

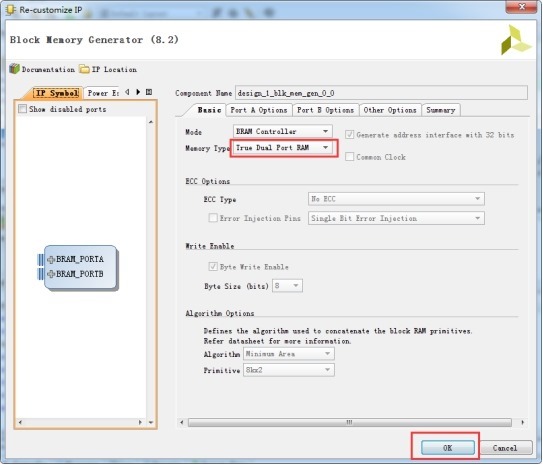

Step13:双击Block Memory Generator ,修改Memory Type。

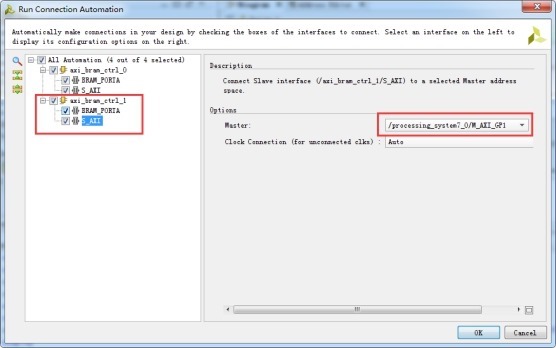

Step14:点击run Connection Automation,把axi_bram_ctrl_1的S_AXI端口的连接目标修改为如图所示:

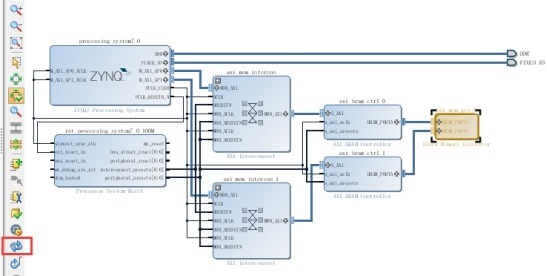

Step15:点击重新布局,生成好的硬件框架如下

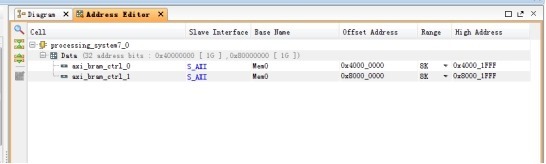

Step16:点击Address Editor 可以看到系统已经为我们自动分配好了正确的地址

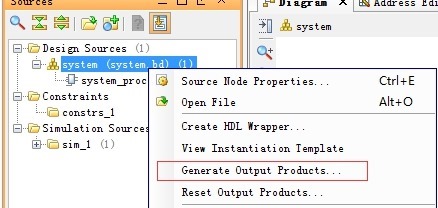

Step17: 右击 system.bd, 单击Generate Output Products

Step18:支部操作会产生执行、仿真、综合的文件

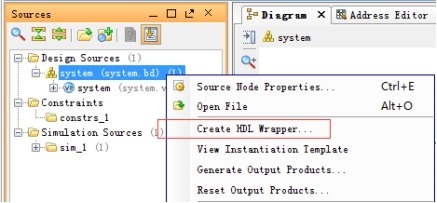

Step19:右击system.bd 选择 Create HDL Wrapper 这步的作用是产生顶层的HDL文件

Step20:选择Leave Let Vivado manager wrapper and auto-update 然后单击OK

Step21:执行->产生bit文件

12.3导出SOC硬件到SDK

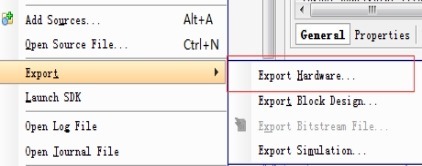

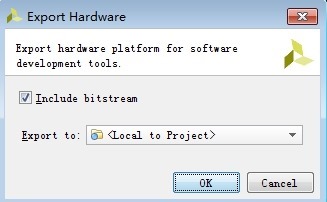

Step1:File->Export->Export Hardware

Step2:勾选Include bitstream 直接单击OK

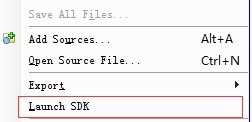

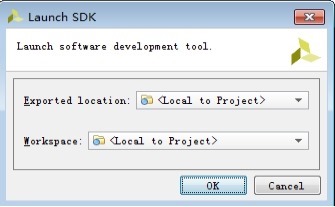

Step3:File->Launch SDK加载到SDK

Step4:单击OK

12.4 软件工程

Step1:打开的SDK界面如下,这里的信息是和硬件相关的,例如在Address Map 这一栏下可以看到axi_bram_ctrl_0和刚刚在vavado Address Editor下的地址是一致的

Step2: 新建一个名为BRAM_Test的空的工程,并且新建一个main.c文件,添加如下代码。

|

/* * mai.c * * Created on: 2016年6月26日 * Author: Administrator */ #include <stdio.h> #include "xil_io.h" //这个头文件下面包含很重要的IO读写函数 #include "xparameters.h" //这个头文件里把硬件的地址映射等参数都写成了宏定义方便使用 //void print(char *str); int main() { int num; int rev; xil_printf("------The test is start...------\n\r"); //XPAR_AXI_BRAM_CTRL_0_S_AXI_BASEADDR是axi_bram_ctrl_0的地址,Xil_Out32通过控制axi_bram_ctrl_0,向blk_mem_gen_0写数据 for( num=0; num<15; num++ ) { Xil_Out32(XPAR_BRAM_0_BASEADDR + num*4, 0x10000000+num); // } //XPAR_AXI_BRAM_CTRL_1_S_AXI_BASEADDR是axi_bram_ctrl_1的地址,Xil_In32 通过控制axi_bram_ctrl_0,把blk_mem_gen_0里的数据读出来 //PS和PL可以在blk_mem_gen_0里共享数据 for( num=0; num<15; num++ ) { rev = Xil_In32(XPAR_BRAM_0_BASEADDR + num*4); xil_printf( "The data at %x is %x \n\r",XPAR_BRAM_0_BASEADDR + num*4,rev); } xil_printf("------The test is end!------\n\r"); return 0; } |

12.5 测试结果

串口终端打印输出信息如下:

------The test is start...------

The data at 80000000 is 10000000

The data at 80000004 is 10000001

The data at 80000008 is 10000002

The data at 8000000C is 10000003

The data at 80000010 is 10000004

The data at 80000014 is 10000005

The data at 80000018 is 10000006

The data at 8000001C is 10000007

The data at 80000020 is 10000008

The data at 80000024 is 10000009

The data at 80000028 is 1000000A

The data at 8000002C is 1000000B

The data at 80000030 is 1000000C

The data at 80000034 is 1000000D

The data at 80000038 is 1000000E

------The test is end!------

12.6 本章小结

本文通过PS端把数据写入到PL端的BRAM,然后从而又把数据从PL端读到PS端,从而简单的实现了PL和PS的数据交互和共享。

官网论坛:www.osrc.cn

视频链接:http://www.osrc.cn/forum.php?mod=viewthread&tid=1102

源码链接:http://pan.baidu.com/s/1hssfxbQ 密码:040p

第十二章 ZYNQ-MIZ702 PS读写PL端BRAM的更多相关文章

- 第十一章 ZYNQ-MIZ701 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- Vivado设计二:zynq的PS访问PL中的自带IP核(基于zybo)

1.建立工程 首先和Vivado设计一中一样,先建立工程(这部分就忽略了) 2.create block design 同样,Add IP 同样,也添加配置文件,这些都和设计一是一样的,没什么区别. ...

- [CSAPP笔记][第十二章并发编程]

第十二章 并发编程 如果逻辑控制流在时间上是重叠,那么它们就是并发的(concurrent).这种常见的现象称为并发(concurrency). 硬件异常处理程序,进程和Unix信号处理程序都是大家熟 ...

- JavaScript DOM编程艺术-学习笔记(第十二章)

第十二章 1.本章是综合前面章节的所有东西的,一个综合实例 2.流程:①项目简介:a.获取原始资料(包括文本.图片.音视频等) b.站点结构(文件目录结构) c.页面(文件)结构 ②设计(切图) ③c ...

- 《OpenCL异构并行编程实战》补充笔记散点,第五至十二章

▶ 第五章,OpenCL 的并发与执行模型 ● 内存对象与上下文相关而不是与设备相关.设备在不同设备之间的移动如下,如果 kernel 在第二个设备上运行,那么在第一个设备上产生的任何数据结果在第二个 ...

- 进击的Python【第十二章】:mysql介绍与简单操作,sqlachemy介绍与简单应用

进击的Python[第十二章]:mysql介绍与简单操作,sqlachemy介绍与简单应用 一.数据库介绍 什么是数据库? 数据库(Database)是按照数据结构来组织.存储和管理数据的仓库,每个数 ...

- 第十二章 Python文件操作【转】

12.1 open() open()函数作用是打开文件,返回一个文件对象. 用法格式:open(name[, mode[, buffering[,encoding]]]) -> file obj ...

- Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第十二章:几何着色器(The Geometry Shader)

原文:Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第十二章:几何着色器(The Geometry Shader) 代码工 ...

- 《深入理解java虚拟机》读书笔记十一——第十二章

第十二章 Java内存模型与线程 1.硬件效率与一致性 由于计算机的存储设备与处理器的运算速度有几个数量级的差距,所以现代计算机系统都不得不加入一层读写速度尽可能接近处理器运算速度的高速缓存(Cac ...

随机推荐

- GEOS库的编译

下载地址https://trac.osgeo.org/geos/ 选择最新的geos-3.6.2版本,下载 将geos-3.6.2放在VS2012文件夹下,本例是D:\VS2012 打开VS2012开 ...

- Linux快速编译

#include<bits/stdc++.h> using namespace std; string name, tmp, s; int main() { cin >> tm ...

- spring boot处理跨域

使用重写WebMvcConfigurer的方式 @Component public class WebMvcConfig extends WebMvcConfigurationSupport { @O ...

- Jenkins修改显示语言为中文

1 安装插件 主界面 -> 系统管理 -> 插件管理 -> 可选插件 1.1 安装插件Locale plugin 1.2 安装插件Localization: Chinese(Simp ...

- ReactiveCocoa实践

1.按钮addTarget [[self.aDepositBtn rac_signalForControlEvents:UIControlEventTouchUpInside] subscribeNe ...

- pwn学习日记Day10 《程序员自我修养》读书笔记

第一章 从 Hello world 说起 抛出问题: 1.程序为什么要被编译器编译后才能执行? 2.编译器在把C语言程序转换成可以执行的机器码的过程中做了什么,怎么做的? 3.最后编译出来的可执行文件 ...

- AddLayer和AddTag

using System.Collections; using System.Collections.Generic; using UnityEditor; using UnityEngine; pu ...

- mongodb 报错 not authorized on admin to execute command【 version 3.2.18 】

mongodb version 3.2.18 测试问题: 分析: 从报错内容上看是权限不够,但不明了为什么,因为已经使用的超级用户权限: { "_id" : "admin ...

- 09 Flutter底部Tab切换保持页面状态的几种方法

IndexedStack:保此所有页面的状态: AutomaticKeepAliveClientMixin:保此部分页面的状态: 修改的页面代码: 页面效果: Tabs.dart import 'pa ...

- 阶段5 3.微服务项目【学成在线】_day03 CMS页面管理开发_04-新增页面-服务端-接口开发

api接口定义方法 api的微服务里面.CmsPageControllerApi内定义add方法,返回类型是CmsPageResult CmsPageResult继承了ResponseResult R ...