Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器。在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还是有一些不方便,所以我便直接使用Modelsim独立仿真,但是对于IP Core的话,就需要添加Vivado IP Core的库文件,本人查阅了很多资料,最终实现了使用Modelsim仿真Vivado Clocking Wizard IP Core,软件版本,Vivado 2017.3、Modelsim SE10.4。具体流程如下,实测记录。

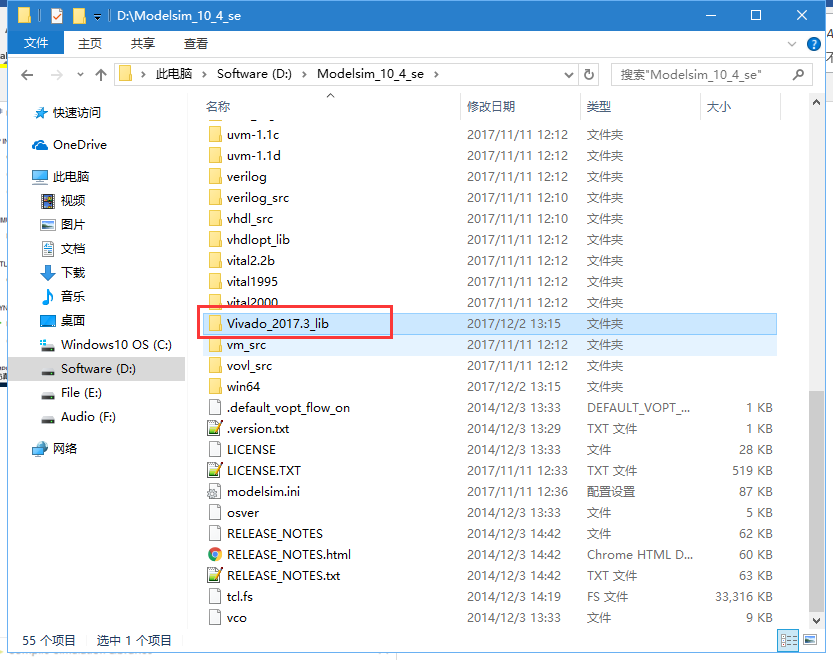

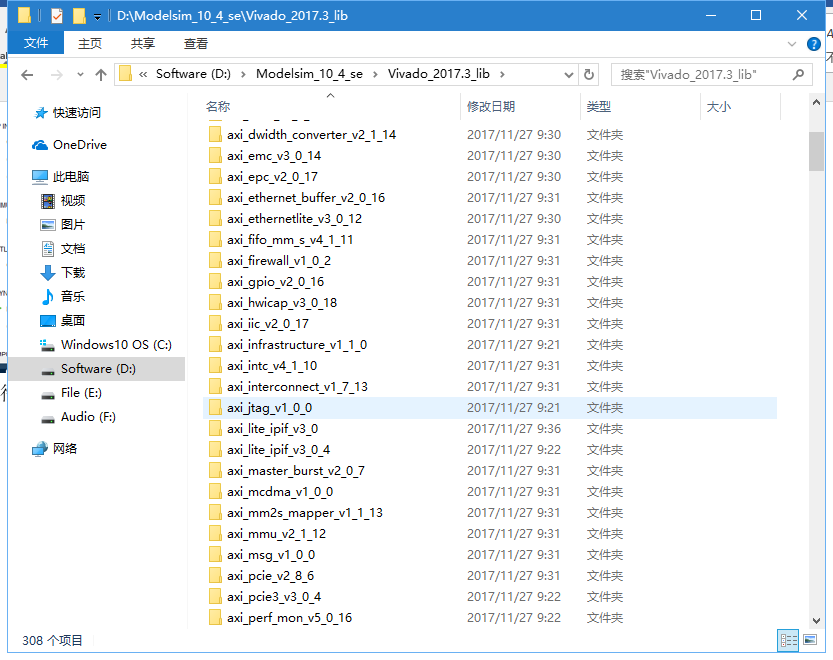

首先,在 Modelsim 的安装目录下新建一个文件夹,我这里是D:\Modelsim_10_4_se\Vivado_2017.3_lib

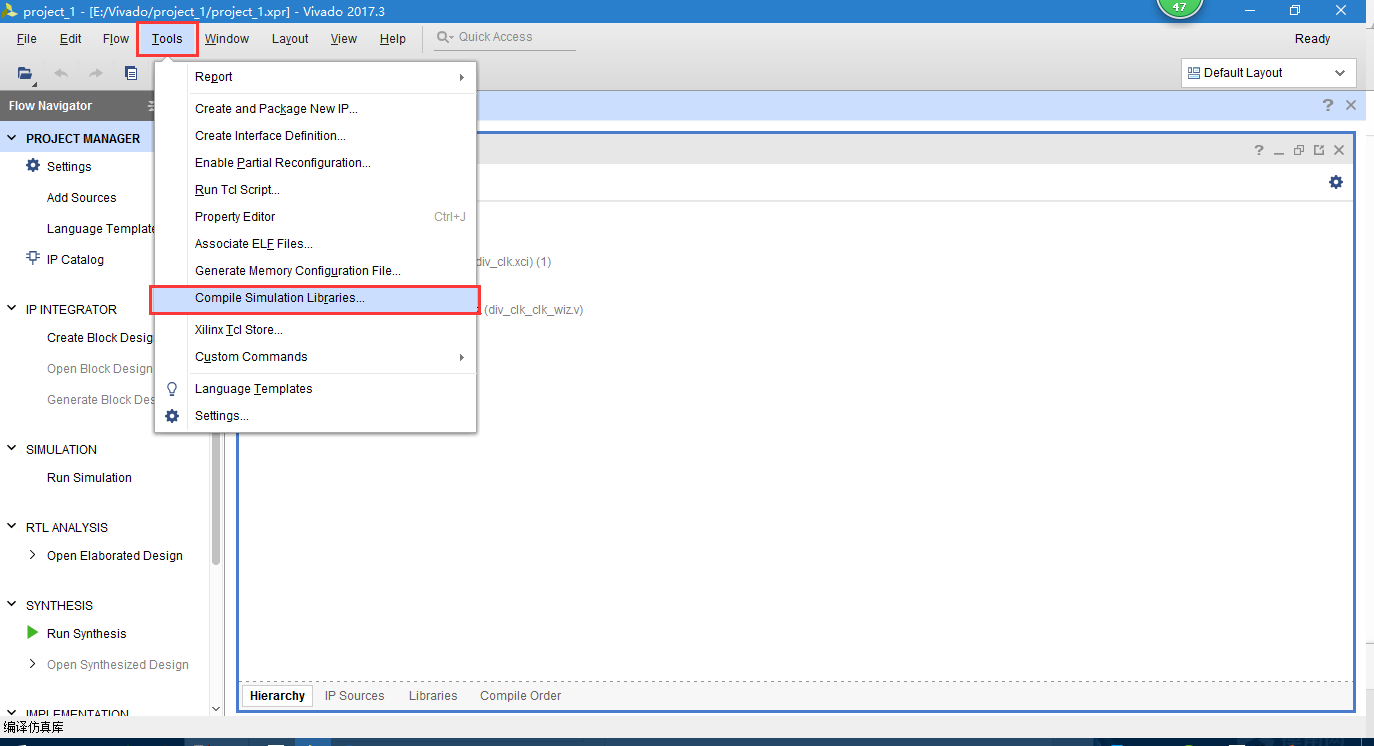

然后,打开Vivado软件,主界面菜单栏点击Tools下的Compile Simulation Libraries编译Vivado仿真库

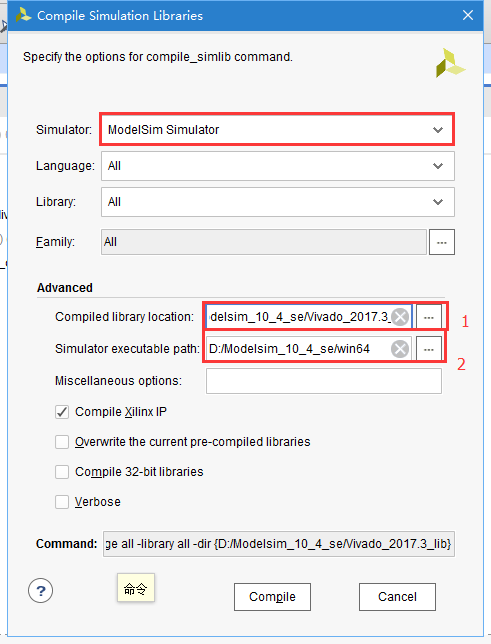

弹出如下窗口然后按如图所示选择,1处路径为刚才我们新建的文件夹中,2处为Modelsim的运行程序路径。设置好后点击compile。

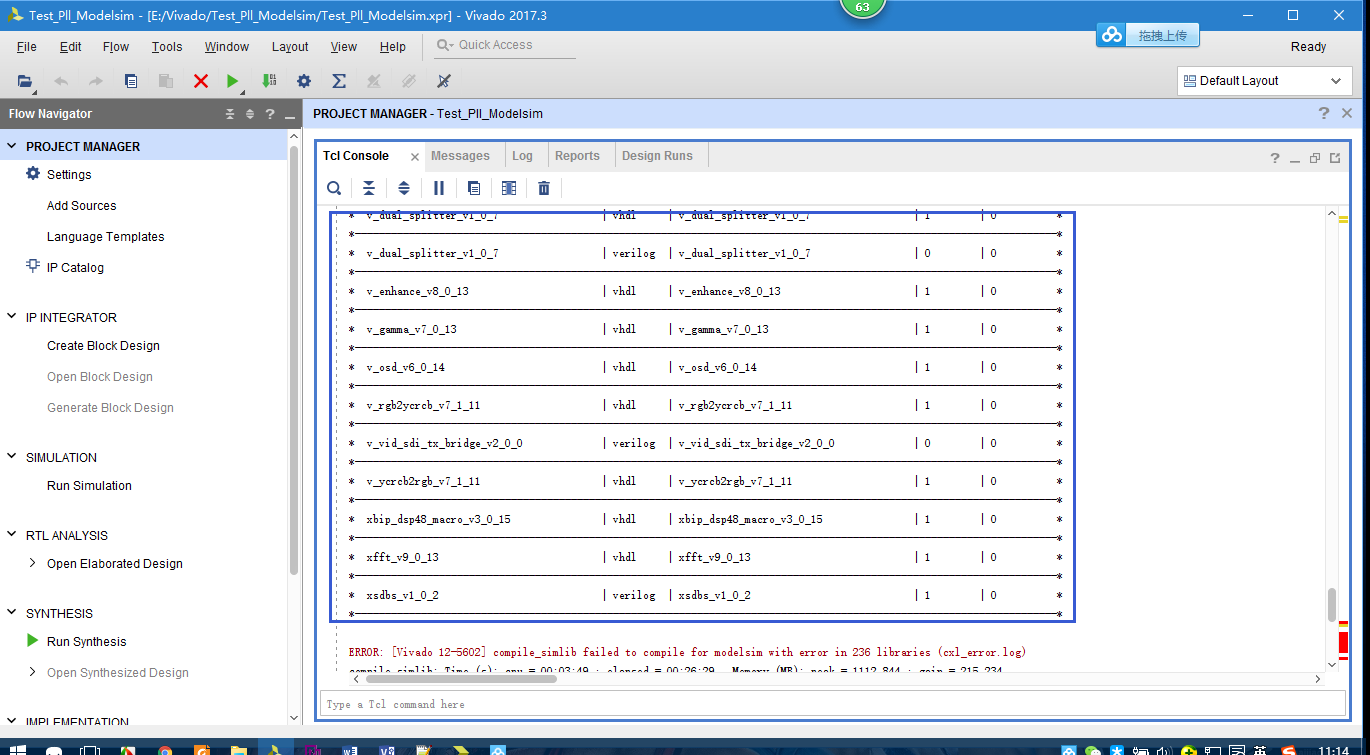

在编译的过程中窗口会打印出来如下信息。

等待一段时间,Vivado的库文件编译完成后我们可以看到文件夹下都是Vivado的库文件

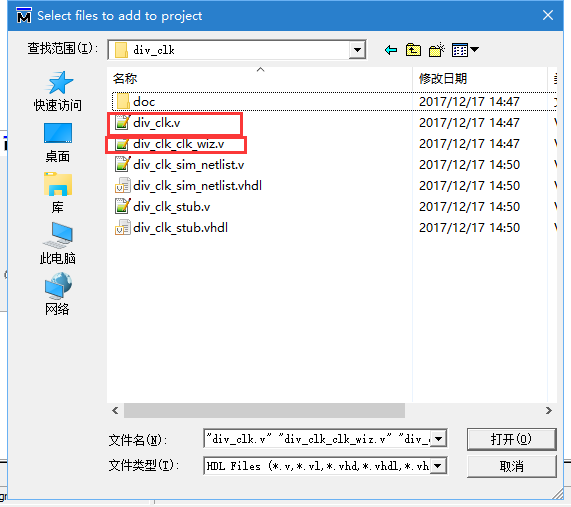

然后使用Vivado新建一个调用的Clocking Wized IP Core的工程,编写好测试文件,然后再用Modelsim新建一个仿真工程,将测试文件和顶层添加进来。这里省略掉这些步骤。这里需要将IP Core中生成的两个文件添加进来,如下图所示。

直接在work右键点击test bench文件进行仿真会出现如下错误,这是因为没有添加所仿IP Core的库文件

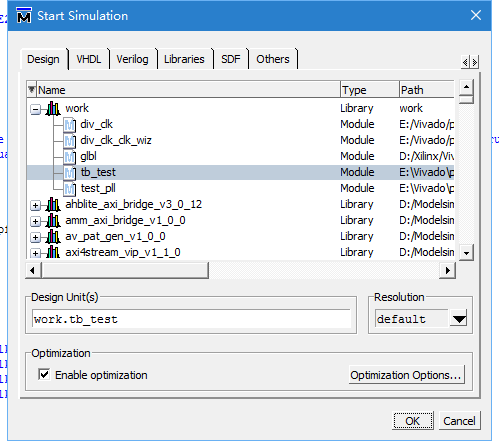

点击标题栏simulator——start simulator,在work里选中test bench。

点击libraries,点击添加所需要的库,这里只需要simprims_ver

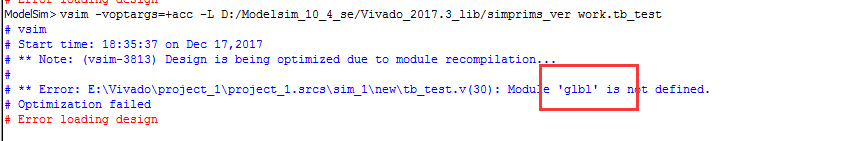

点击这里后还是会出现错误,打印出来的信息如下,提示缺少glbl模块,

这是Xilinx的全局复位模块,该模块的路径在你Vivado的安装路径里,比如我的是D:\Xilinx\Vivado2017.3\Vivado\2017.3\data\verilog\src中,把它添加到工程里面,在test bench中如图所示例化一下这个模块,然后重新仿真一次。

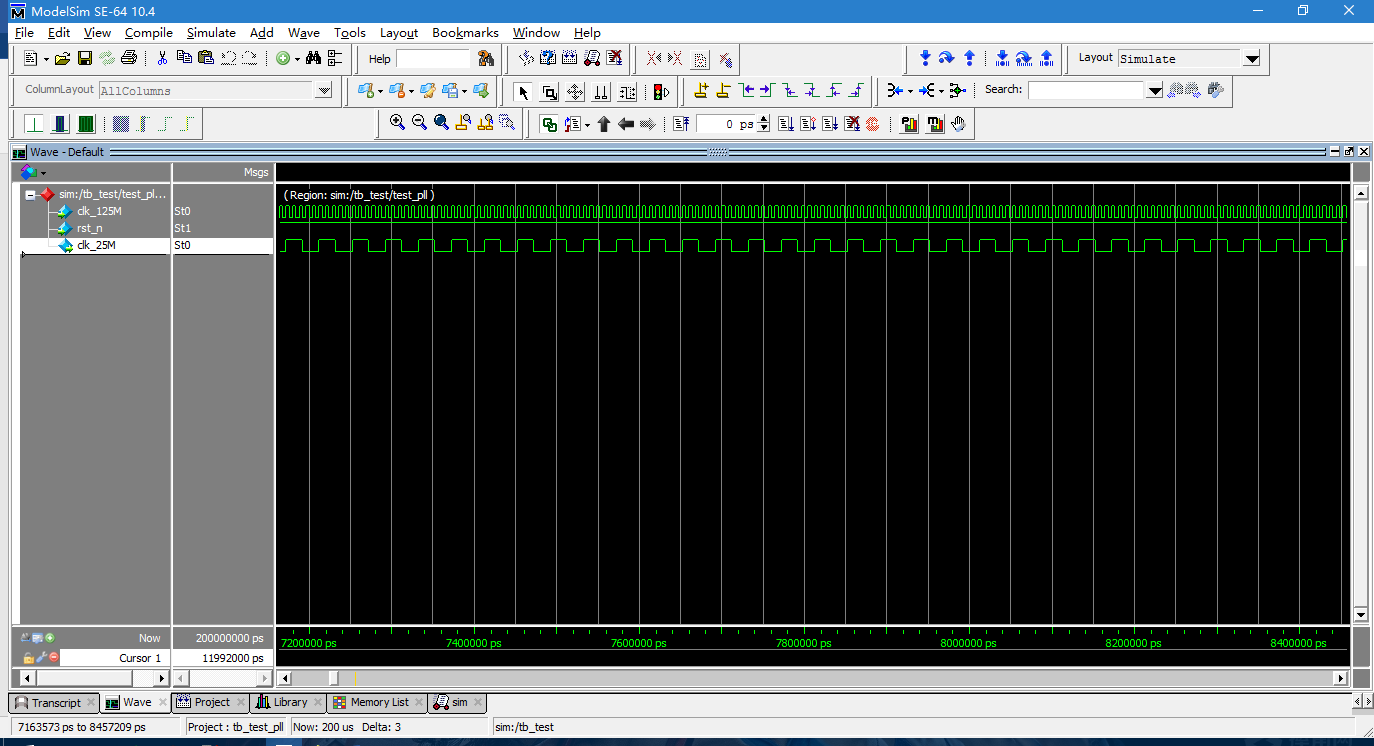

然后就可以看到波形了

我这里的测试工程师一个125Mhz分25Mhz的五分频。

接下来本人会继续尝试使用Modelsim仿真FIFO、RAM/ROM、Shift_RAM等常用IP Core,如果你有什么更加高效的方法,欢迎提出,欢迎指点。如果需要Modelsim软件请关注我的微信订阅号:开源FPGA,后台回复“Modelsim”即可获得,欢迎加入开源FPGA-交流群-I进行讨论,群号码:677163633。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8305925.html

Modelsim独立仿真Vivado Clocking Wizard IP Core的更多相关文章

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- [Xilinx]Modelsim独立仿真Vivado生成的PLL核

EDA Tools: 1.Vivado 2015.1(64-bit) 2.Modelsim SE-64 10.1c Time: 2016.05.26 ------------------------- ...

- 基于Vivado调用ROM IP core设计DDS

DDS直接数字式频率合成器(Direct Digital Synthesizer) 下面是使用MATLAB生成正弦波.三角波.方波的代码,直接使用即可. t=:*pi/^:*pi y=0.5*sin ...

- Vivado&ISE&Quartus II调用Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

- Viavdo&ISE&Quartus II级联Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

- ddr3调试经验分享(一)——modelsim实现对vivado中的MIG ddr3的仿真

Vivado中的MIG已经集成了modelsim仿真环境,是不是所有IP 都有这个福利呢,不知道哦,没空去验证. 第一步:使用vivado中的MIG IP生成一堆东西 ,这个过程自己百度.或者是ug5 ...

- Modelsim SE 仿真 ALTERA FPGA IP

Modelsim SE 仿真 ALTERA FPGA IP 最近,有几个朋友问过我是不是有新版本的Modelsim altera,其原因是 Qii 升级为新版本的,但是没配套的modelsim,没办法 ...

- 用Modelsim SE 直接仿真 Altera(Intel PSG) IP核 需要注意的问题

如果我们直接用Modelsim SE仿真 Altera IP核,首先会进入Quartus II目录下找到IP核对应的仿真库源文件,然后在Modelsim SE中进行编译,添加到Modelsim SE的 ...

- Vivado 与 Modelsim 联合仿真

1 编译库 用命令行 用vivado工具 vivado 有很多 IP核的接口 已经与 ISE的核 不太一样了,比如fir ,接口就是这样的: fir_lp fir_lp_ip( .aclk ( ...

随机推荐

- 总结一下现在关于Design Support Library的几个博客

原文转载:http://www.jcodecraeer.com/a/anzhuokaifa/androidkaifa/2015/0713/3179.html 关于Design Support Libr ...

- 在Office Add-in中实现单点登陆(SSO)

作者:陈希章 发表于 2017年12月27日 这篇文章经过多次修改,终于在今天晚上写完了,演示用的范例代码也终于跑通了.因为这个SSO的功能目前只是Preview的状态,所以本篇文章严格参考了官方的文 ...

- 详解MongoDB管理命令

MongoDB是一个NoSQL数据库系统:一个数据库可以包含多个集合(Collection),每个集合对应于关系数据库中的表:而每个集合中可以存储一组由列标识的记录,列是可以自由定义的,非常灵活,由一 ...

- idea和Webstorm上使用git和github,码云

由于之前一直使用svn,现在项目使用git,顾根据网上找的学习资料,自己梳理了下,收获蛮多,这里做个记录,如果能帮助到您那是最好不过的. 1.大致步骤 使用工具:idea,github,码云 webs ...

- 【python】字符串变量赋值时字符串可用单或双引号

>>> name='萧峰' >>> print(name) 萧峰 >>> name="独孤求败" >>> p ...

- 指针变量的*p,p以及&p的区别

23/7/2017 决定夯实基础,回顾指针的知识点,该博文转载于CSDN博主百家晓东,小部分修改,外加编译图引证 正文如下: 以下面的情况说明: int a = 5; int* p = &a ...

- react native仿微信性别选择-自定义弹出框

简述 要实现微信性别选择需要使用两部分的技术: 第一.是自定义弹出框: 第二.单选框控件使用: 效果 实现 一.配置弹出框 弹出框用的是:react-native-popup-dialog(Git地址 ...

- Xamarin截取/删除emoji表情bug解决方案

大家都知道,一个英文=1字节,一个汉字2字节,而一个emoji表情=4个字节,在有这三种混用的时候,比如app聊天界面,那么删除和截取便成了很头痛的事情. 问题描述 截取导致乱码,如下图: 解决方案 ...

- js浏览器对象navigator

移动端通常需要判断当前设备的类型,比如安卓,ios等.输出浏览器的请求代理,可以判断浏览器类型.js代码如下 判断当前浏览器的请求代理 我是出来玩的! <!DOCTYPE html> &l ...

- Angularjs 2 绝对零基础的教程(1):从安装配置开始

写在前面 适合人群: 1. 愿意未来从事前端工作,并以此开拓自己未来职业 2. 有任何一种编程语言基础 3. 喜欢简单粗暴学一门实用的技术,而不是做科研. Angular 2 比 Angular 1 ...