11-verilog-有限状态机

有限状态机

写RTL的时候,实现一个功能的时候有很多种方法

- 将系统划分为多个状态,状态之间有状态的转移,第一步,第二步......形成有限状态机

- 流水线技术设计,从输入到输出有多个步骤,多个步骤可以并行执行

有限状态机,状态是有限的,比如8个状态,16个状态等,在进行设计的时候,状态机的状态不要太多,状态超过10个,就会造成设计复杂度和验证复杂度都变高.

有限状态机分类

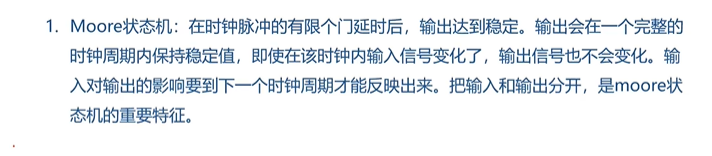

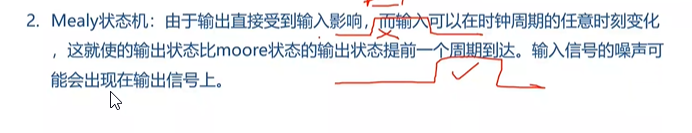

- Moore FSM

输出只与当前的状态有关,与输入没有关系 - Mealy FSM

输出不仅与当前的状态有关,还与输入有关

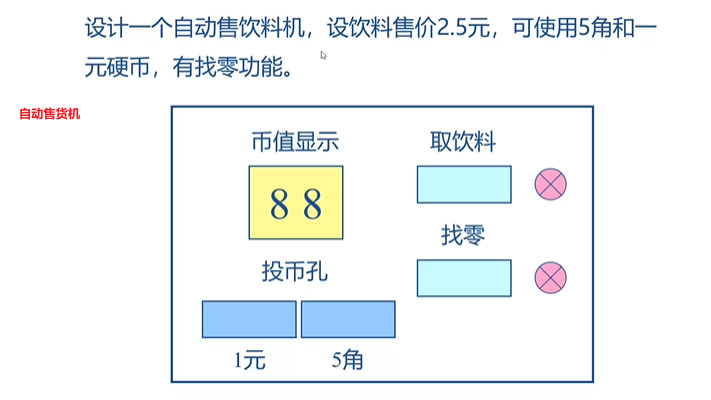

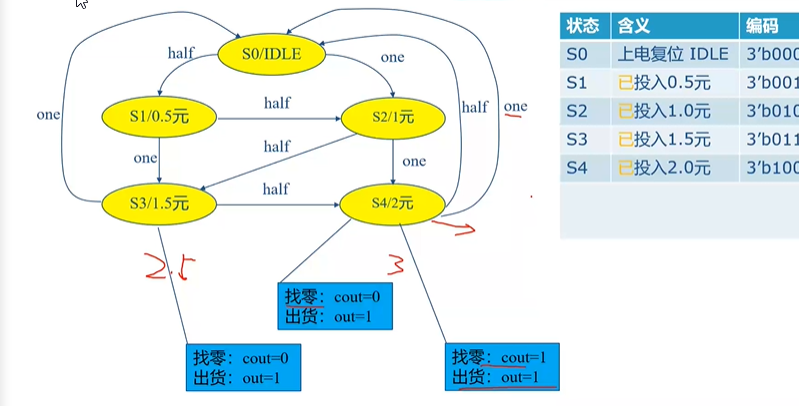

Moore FSM-设计自动售货机

分析输入输出信号

- 自动售货机,输入的就是硬币,输出的是饮料和找零 (确定输入,输出)

- 假设饮料只有一种价格2.5元,输入的零钱只有一元和五角(两种状态,用1bit表示),找零的情况只有两种0元和5角(用1bit表示)(确定输出输出的状态,用几位的信号表示)

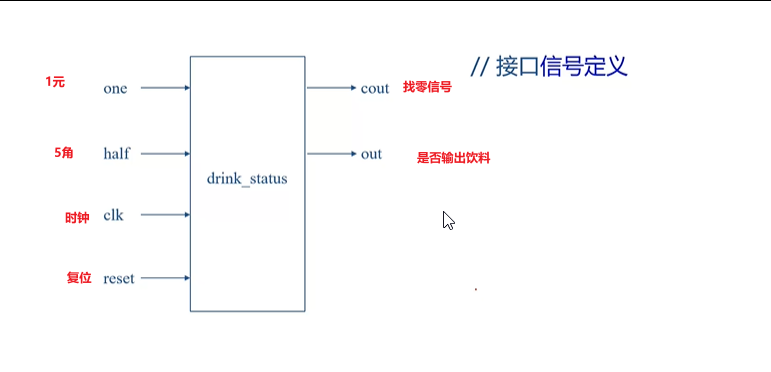

定义接口

- 状态机要存储一些状态,肯定会有一些寄存器,会有时钟和复位信号

- 在设计一个模块的时候,最先确定输入输出的端口和位宽以及时序

定义时序

- 输入的一元和五角不能同时为1(确定输入的约束)

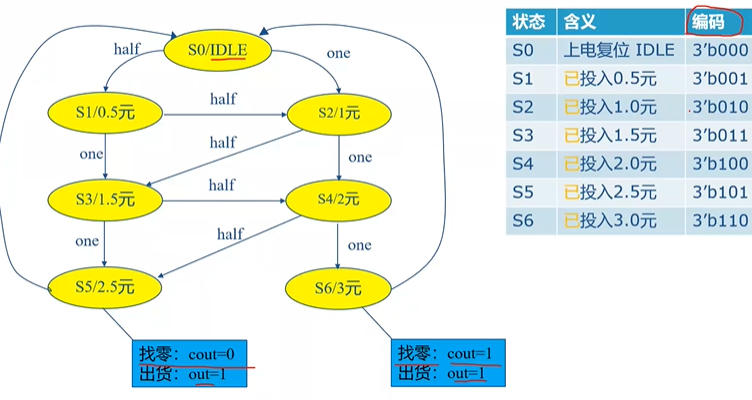

内部实现--画出状态转移图

要存储当前已经存储了多少钱,初始状态时0,可以收到1元和5角

- IDLE就是当前系统是空闲状态,没有收到任何的投币

- 这是一个Moore类型的有限状态机,输出只与当前的状态有关

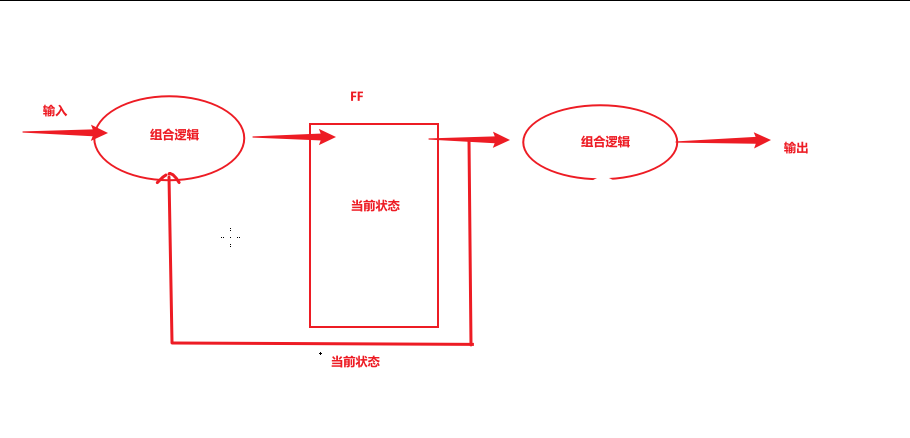

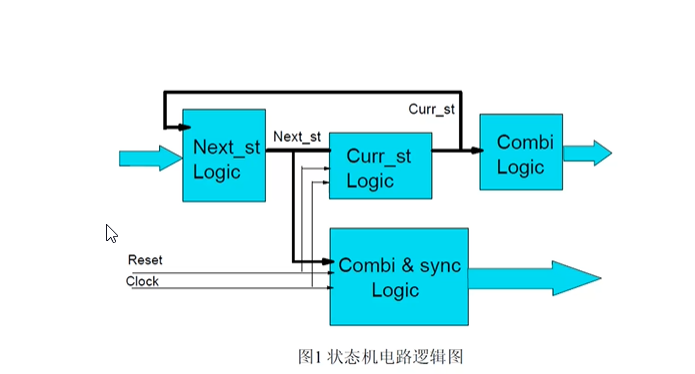

Moore有限状态机电路特点

- 输入与当前的状态有关,所以需要一个寄存器存储当前的状态

- 寄存器存储的状态输入给组合逻辑之后,进行输出

- 输入与当前的状态值,经过组合逻辑之后,输入给寄存器

- 时序清晰,输入和输出,没有一条直接的组合逻辑路径;如果输入经过组合逻辑,没有经过寄存器,直接输出,这样的设计不好;因为不知道周围环境的组合逻辑的时序是多少

Code

module drink_status_moore(

input clk,

input reset,

input half,

input one,

output out,

output cout

);

parameter [2:0] s0 = 3'b000,

s1 = 3'b001,

s2 = 3'b010,

s3 = 3'b011,

s4 = 3'b100,

s5 = 3'b101,

s6 = 3'b110; //定义6个状态

reg [2:0] curr_state; //当前状态 CS

reg [2:0] next_state; //下一个状态 NS reg定义的信号不一定是寄存器

//第一段:声明一个寄存器,state transfer

always @ (posedge clk ,negedge reset) begin

if(~reset)

curr_state <= s0; //这里时钟来了之后,就寄存器传输,寄存器功耗比较大,需要给寄存器传输添加条件

else

curr_state <= #1 next_state;

end

//第二段,根据条件写出中间状态转移

always @ (curr_state,half,one) begin

case(curr_state)

s0:begin

if(half) next_state = s1; //如果两个投币口,就会出现问题,一次投入可能为1.5元,所以要给输入添加约束

else if(one) next_state = s2; //文件和文件之间需要进行一些约束

else next_state = S0;

end

s1:begin

if(half) next_state = s2;

else if(one) next_state = s3;

else next_state = S1;

end

s2:begin

if(half) next_state = s3;

else if(one) next_state = s4;

else next_state = S2;

end

s3:begin

if(half) next_state = s4;

else if(one) next_state = s5;

else next_state = S3;

end

s4:begin

if(half) next_state = s5;

else if(one) next_state = s6;

else next_state = S4;

end

s5:begin

next_state = s0;

end

s6:begin

next_state = s0;

end

default: next_state = s0;

end

//第三段,写出输出

assign out = (curr_state == s5) || (curr_State = s6) ? 1:0;

assign cout = (curr_state == s6) ? 1:0;

endmodule

FSM 三段式的书写方式

mealy FSM-自动售货机

- 相当于在当前状态,考虑之后输入的状态

- 输入经过组合逻辑之后直接得到输出

module drink_status_moore(

input clk,

input reset,

input half,

input one,

output out,

output cout

);

parameter [2:0] s0 = 3'b000,

s1 = 3'b001,

s2 = 3'b010,

s3 = 3'b011,

s4 = 3'b100; //定义6个状态,变量名需要更加具有含义

reg [2:0] curr_state; //当前状态 CS

reg [2:0] next_state; //下一个状态 NS reg定义的信号不一定是寄存器

//第一段:声明一个寄存器,state transfer

always @ (posedge clk ,negedge reset) begin

if(~reset)

curr_state <= s0; //这里时钟来了之后,就寄存器传输,寄存器功耗比较大,需要给寄存器传输添加条件

else

curr_state <= #1 next_state;

end

//第二段,根据条件写出中间状态转移

always @ (*) begin

case(curr_state)

s0:begin

if(half) next_state = s1; //如果两个投币口,就会出现问题,一次投入可能为1.5元,所以要给输入添加约束

else if(one) next_state = s2; //文件和文件之间需要进行一些约束

else next_state = S0;

end

s1:begin

if(half) next_state = s2;

else if(one) next_state = s3;

else next_state = S1;

end

s2:begin

if(half) next_state = s3;

else if(one) next_state = s4;

else next_state = S2;

end

s3:begin

if(half) next_state = s4;

else if(one) next_state = s0;

else next_state = S3;

end

s4:begin

if(half) next_state = s0;

else if(one) next_state = s0;

else next_state = S4;

end

default: next_state = s0;

endcase

end

//第三段,写出输出

assign out = ((curr_state == s4) & (half | one)) ? 1:

((curr_state == s3) & (one)) ? 1 : 0;

assign cout = (curr_state == s4) & (one) ? 1 : 0;

endmodule

FSM有限状态机的设计步骤

- 接口定义(信号\位宽\约束)

- 状态定义和编码

- 状态转换图

- 按照三段式风格实现RTL代码

- 编写Testbench

- 使用QuestaSim进行编译和仿真

- 通过波形工具查看激励\状态信号和输出信号

- Moore机输出只与当前状态有关

- Mealy输出不仅与当前的状态有关,还与当前的输入有关

状态机的电路逻辑图

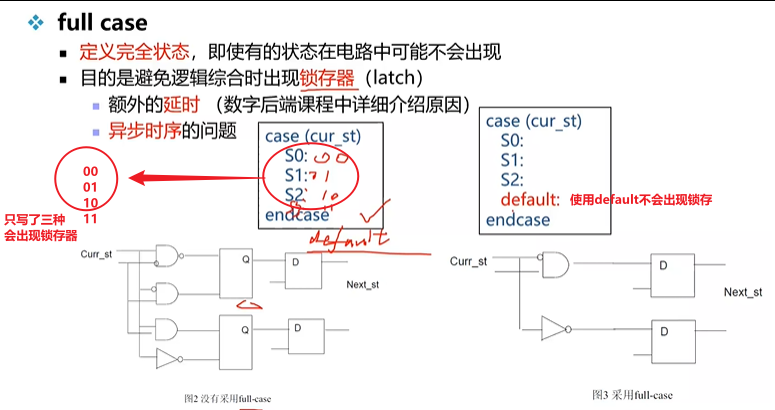

FSM要注意的问题

- case语句,要将所有的case列全

- 使用default语句还原状态;如果不写default,就需要写够所有可能

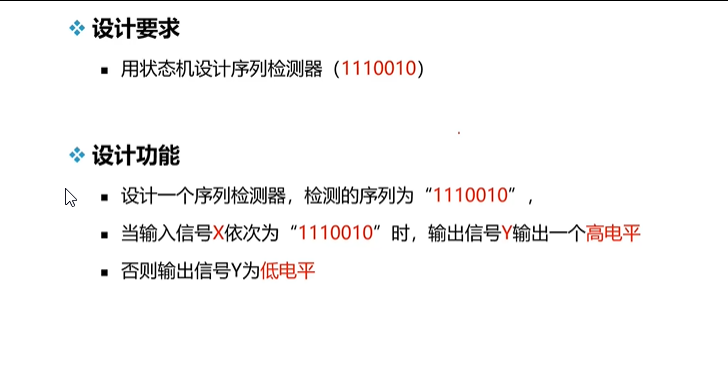

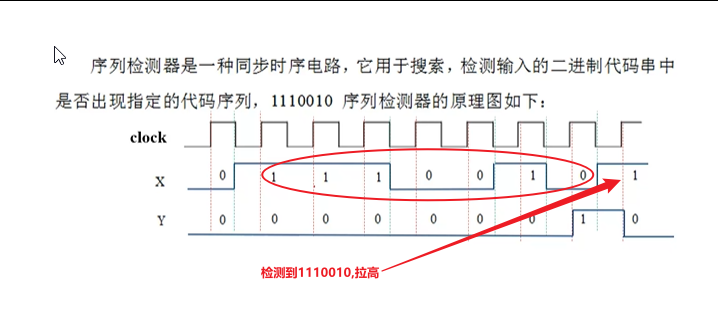

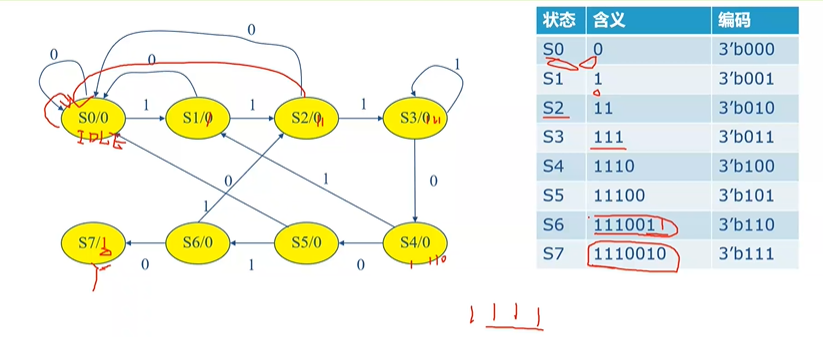

序列检测器

- 输入就是1bit的x,输出的y也是1bity

- 定义当前的状态,存储之前存储的序列是怎样的状态,初始为IDLE,中间状态可能会出现中间状态

- IDLE在定义的时候,检测的序列是从1开始的,IDLE可以直接设计为初始值为1,中间状态出现01,10等不对的状态,可以取消掉

module seq(in,out,clk,reset,state);

input in;

input clk;

input reset;

output out;

output [2:0] state;

reg [2:0] curr_state;

reg [2:0] next_state;

parameter [2:0] s0 = 3'b000,

s1 = 3'b001,

s2 = 3'b010,

s3 = 3'b011,

s4 = 3'b100,

s5 = 3'b101,

s6 = 3'b110,

s7 = 3'b111;

// 定义寄存器

always @ (posedge clk , negedge reset)

begin

if(~reset)

curr_state <= S0;

else

curr_state <= next_state;

end

// 写状态转移

always @ (in,curr_state)

begin

case(curr_state)

s0 : begin

if(in == 0) next_state <= s0;

else next_state <= s1;

end

s1 : begin

if(in == 0) next_state <= s0;

else next_state <= s2;

end

s2 : begin

if(in == 0) next_state <= s0;

else next_state <= s3;

end

s3 : begin

if(in == 0) next_state <= s4;

else next_state <= s3;

end

s4 : begin

if(in == 0) next_state <= s5;

else next_state <= s1;

end

s5 : begin

if(in == 0) next_state <= s0;

else next_state <= s6;

end

s6 : begin

if(in == 0) next_state <= s7;

else next_state <= s2;

end

s7 : begin

if(in == 0) next_state <= s0;

else next_state <= s1;

end

default: next_state <= s0;

endcase

end

// 输出

assign out = (curr_state == s7) ? 1 : 0 ;

endmodule

11-verilog-有限状态机的更多相关文章

- verilog语法学习目录

verilog语法实例学习(1) Verilog中的注释 Verilog中的信号 标识符 信号的值 Verilog中的数字 Verilog中的参数 verilog语法实例学习(2) 线网类型 变量类型 ...

- 跟着我从零开始入门FPGA(一周入门XXOO系列)-1、Verilog语法

(本连载共七部分,这是第一部分) 作者:McuPlayer2013 (EETOP FPGA版块版主) 原帖地址:http://bbs.eetop.cn/thread-385362-1-1.html ...

- Linux基础命令列表

命令列表 A alias apt apt-get arp -n -s arping ab B bc basename bash -n -x bzip2 bunzip2 bzcat blkid brct ...

- IC设计基础

一 前言 这一周连续两场线下面试,紧接着又是微信视频面试,从连续三天的面试中,收获颇丰! 存在的问题: 一是对项目细节模糊: 二是IC基础知识薄弱: 具体表现是,在面试过程中,如被问到DDR3和千兆以 ...

- 地区sql

/*Navicat MySQL Data Transfer Source Server : localhostSource Server Version : 50136Source Host : lo ...

- verilog语法实例学习(11)

同步时序电路的一般形式 时序电路由组合逻辑以及一个或多个触发器实现.一般的架构如下图所示:W为输入,Z为输出,触发器中存储的状态为Q.在时钟信号的控制下,触发器通过加在其输入端的组合逻辑输入,使得电路 ...

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- 有限状态机FSM(自动售报机Verilog实现)

有限状态机FSM(自动售报机Verilog实现) FSM 状态机就是一种能够描述具有逻辑顺序和时序顺序事件的方法. 状态机有两大类:Mealy型和Moore型. Moore型状态机的输出只与当前状态有 ...

- Verilog学习笔记设计和验证篇(三)...............同步有限状态机的指导原则

因为大多数的FPGA内部的触发器数目相当多,又加上独热码状态机(one hot code machine)的译码逻辑最为简单,所以在FPGA实现状态机时,往往采用独热码状态机(即每个状态只有一个寄存器 ...

- verilog学习笔记(4)_有限状态机

有限状态机: 有限状态机是由寄存器组和组合逻辑构成的硬件时序电路: - 其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态: - 究竟转 ...

随机推荐

- Android对接微信登录记录

Android对接微信登录记录 - Stars-One的杂货小窝 Android项目要对接下微信登录,稍微记录下踩坑点 代码 1.添加依赖 implementation 'com.tencent.mm ...

- vue 2实战系列 —— 复习Vue

复习Vue 近期需要接手 vue 2的项目,许久未写,语法有些陌生.本篇将较全面复习 vue 2. Tip: 项目是基于 ant-design-vue-pro ant-design-vue-pro 由 ...

- IPv6规模部署和应用成必然趋势,IPv6监测具有很大市场潜力

日前,中央网信办.国家发展改革委.工业和信息化部联合印发<深入推进IPv6规模部署和应用2021年工作安排>.这更深入的表明,IPv6规模部署和应用是互联网演进升级的必然趋势,是网络技术创 ...

- 文心一言 VS chatgpt (17)-- 算法导论4.1 3~4题

三.在你的计算机上实现最大子数组问题的暴力算法和递归算法.请指出多大的问题规模n0是性能交叉点一一从此之后递归算法将击败暴力算法?然后,修改递归算法的基本情况一一当问题规模小于 n0 时采用暴力算法. ...

- PLG SaaS 案例:如何实践外链自动增长策略?

首先任何的商业逻辑,光流量增长,没法变现是没用的. 就像博客群发提效工具,得有对应的用户,更得有对应付费用户群体的画像.剩下的就是靠增长,被动让他们找到你的产品,用产品解决他们痛点,他们自然而然会付费 ...

- 从4个特点为你解密华为云媒体网络底座AND

本文分享自华为云社区<解密华为云媒体网络底座ADN>,作者: Satan.D . 互联网的痛点与解决思路 互联网自1968年起源依赖,已经发展了半个多世纪.互联网仅从中文字面意思,可以简单 ...

- 聊聊Java的异常机制问题

摘要:java异常指在程序运行时可能出现的一些错误,如:文件找不到.网络连接失败.非法参数等.异常是一个事件,它发生在程序运行期间,中断了正在执行的程序的正常指令流. 本文分享自华为云社区<Ja ...

- CWE 视图层级关系解析:节点关系查询

本文分享自华为云社区<CWE视图层级关系的解析 之 CWE节点关系的查询>,作者: Uncle_Tom. 1. CWE 转换成 SQLite 表 依据<CWE视图层级关系的解析 之 ...

- HBuilderX获取iOS证书的打包步骤

简介: 目前app开发,很多企业都用H5框架来开发,而uniapp又是这些h5框架里面最成熟的,因此hbuilderx就成为了开发者的首选.然而,打包APP是需要证书的,那么这个证书又是如何获得呢? ...

- ByteHouse:基于ClickHouse的实时数仓能力升级解读

更多技术交流.求职机会,欢迎关注字节跳动数据平台微信公众号,回复[1]进入官方交流群 ByteHouse是火山引擎上的一款云原生数据仓库,为用户带来极速分析体验,能够支撑实时数据分析和海量数据离 ...