ZYNQ笔记(6):普通自定义IP封装实现PL精准定时中断

软件的定时中断很难控制精准触发沿的位置,可以通过 PL-PS 的中断完成精准的定时中断。PL 的中断通过 Verilog 代码产生,这样紧密结合 PS-PL 的处理,发挥各自的优势。

一、PL 侧定时中断

1.实际要求

① 上升沿中断;

② 高电平宽度不小于1us;

③ 中断计数器的时钟为 200Mhz;

④ 有两个中断: 3ms 和 .5ms

2.Verilog中断代码

//**************************************************************************

// *** 名称 : genintr3ms05ms.v

// *** 作者 : xianyu_FPGA

// *** 博客 :https://www.cnblogs.com/xianyufpga/

// *** 日期 :2019-08-10

// *** 描述 : 3ms和0.5ms精准延时

//************************************************************************** module genintr3ms05ms

//==================<端口>==================================================

(

//input -----------------------------------------

input wire clk , //时钟,200Mhz

input wire rst , //复位,高电平有效

//output ----------------------------------------

output reg intr3ms , //3ms中断

output reg intr05ms //0.5ms中断

);

//==================<参数>==================================================

parameter CNT3MS_END = ;

parameter CNT05MS_END = ;

parameter PULSEW = ; //中断高电平维持时间

//==================<信号>==================================================

reg [:] cnt3ms ;

wire add_cnt3ms ;

wire end_cnt3ms ;

reg [:] cnt05ms ;

wire add_cnt05ms ;

wire end_cnt05ms ; //==========================================================================

//== 0.5ms延时

//==========================================================================

always @(posedge clk) begin

if(rst)

cnt3ms <= ;

else if(add_cnt3ms) begin

if(end_cnt3ms)

cnt3ms <= ;

else

cnt3ms <= cnt3ms + ;

end

end assign add_cnt3ms = ;

assign end_cnt3ms = add_cnt3ms && cnt3ms== CNT3MS_END-; always @(posedge clk) begin

if(rst) begin

intr3ms <= ;

end

else if(end_cnt3ms) begin

intr3ms <= ;

end

else if(add_cnt3ms && cnt3ms==PULSEW-) begin

intr3ms <= ;

end

end //==========================================================================

//== 3ms延时

//==========================================================================

always @(posedge clk) begin

if(rst)

cnt05ms <= ;

else if(add_cnt05ms) begin

if(end_cnt05ms)

cnt05ms <= ;

else

cnt05ms <= cnt05ms + ;

end

end assign add_cnt05ms = ;

assign end_cnt05ms = add_cnt05ms && cnt05ms== CNT05MS_END-; always @(posedge clk) begin

if(rst) begin

intr05ms <= ;

end

else if(end_cnt05ms) begin

intr05ms <= ;

end

else if(add_cnt05ms && cnt05ms==PULSEW-) begin

intr05ms <= ;

end

end endmodule

3.PL中断封装成私有IP

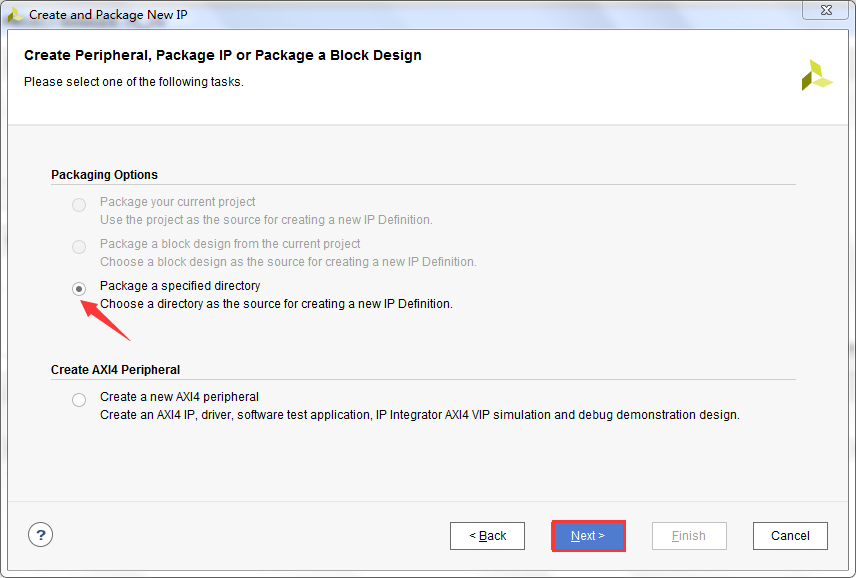

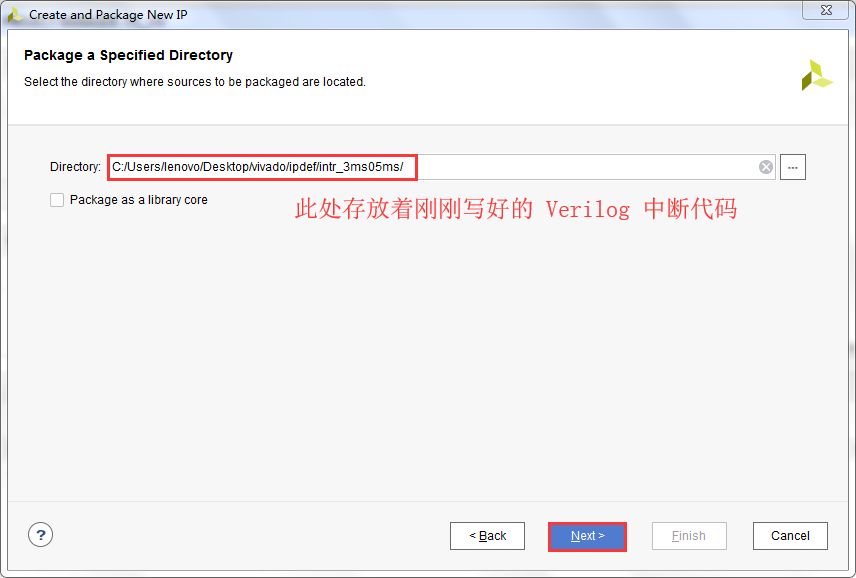

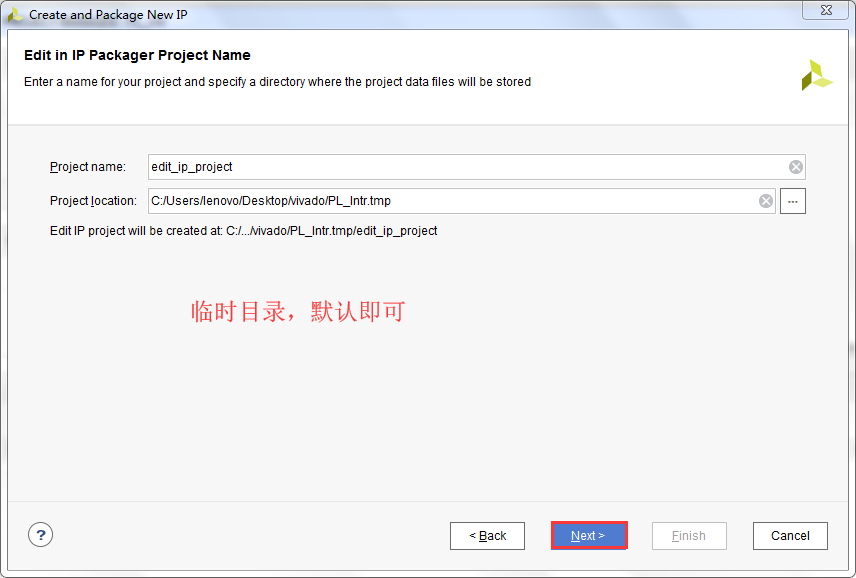

①打开 Vivado,新建工程,然后选择菜单栏 Tools --- Create and Package New IP...

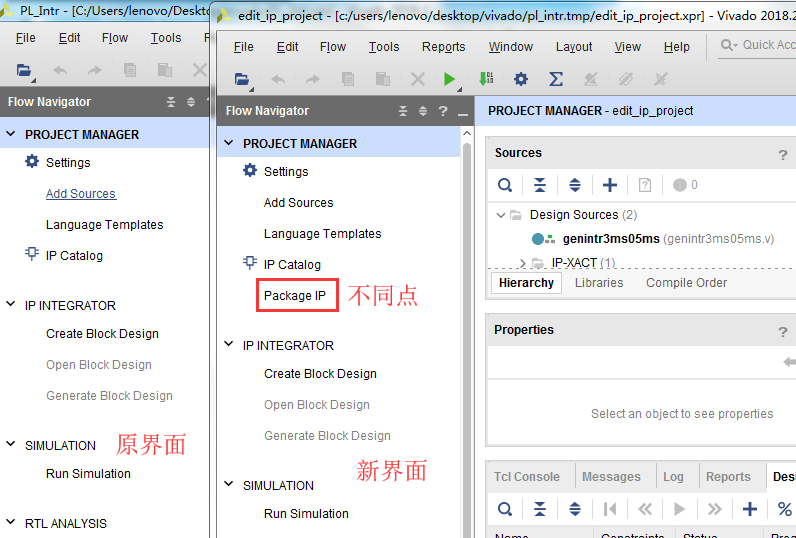

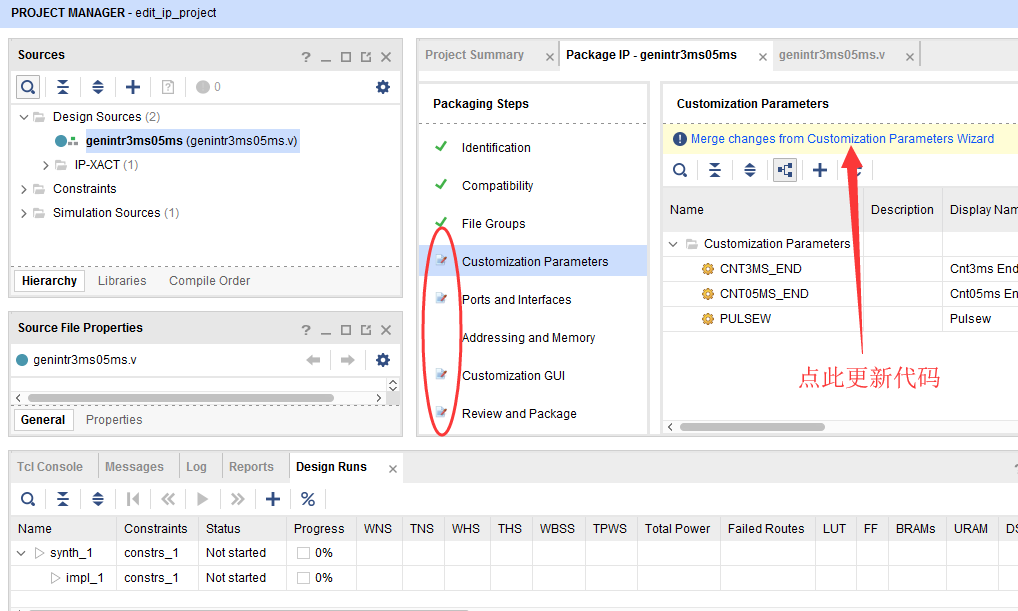

②Vivado 打开了一个新的界面,类似于原界面,但是多了一个选项

这时如果 Verilog 有语法错误,Source处会显示红色波浪线。也可以在此新界面修改代码,修改后保存,页面显示成编辑图标,必须点击更新才行。

③默认情况下,复位是低有效,我们可以手动改成高有效

④选择 Review and Package 可以看到 Package IP ,点击它即可完成 IP 的封装

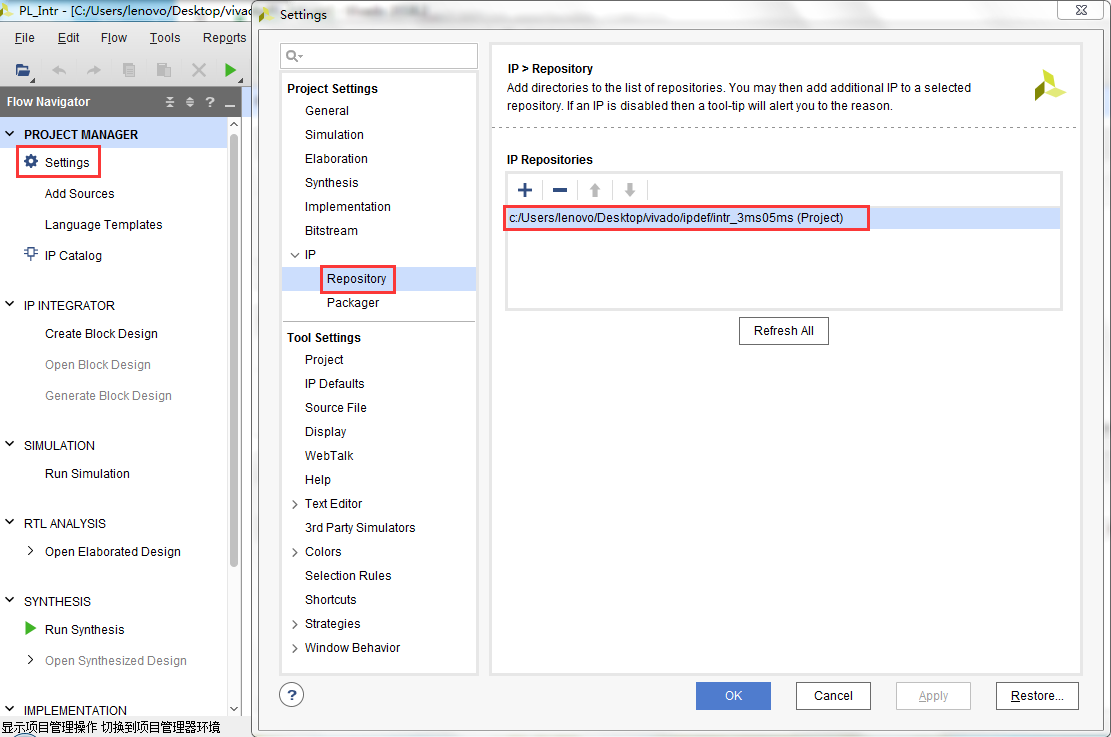

⑤此页面自动关闭,回到原页面,可以在 Settings --- IP --- Repository 中可以看到这个自定义 IP,此页面也可以手动添加第三方 IP

⑥生成 bit 文件并以此加载 SDK。

二、ZYNQ硬中断的使用

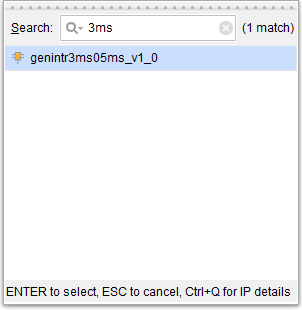

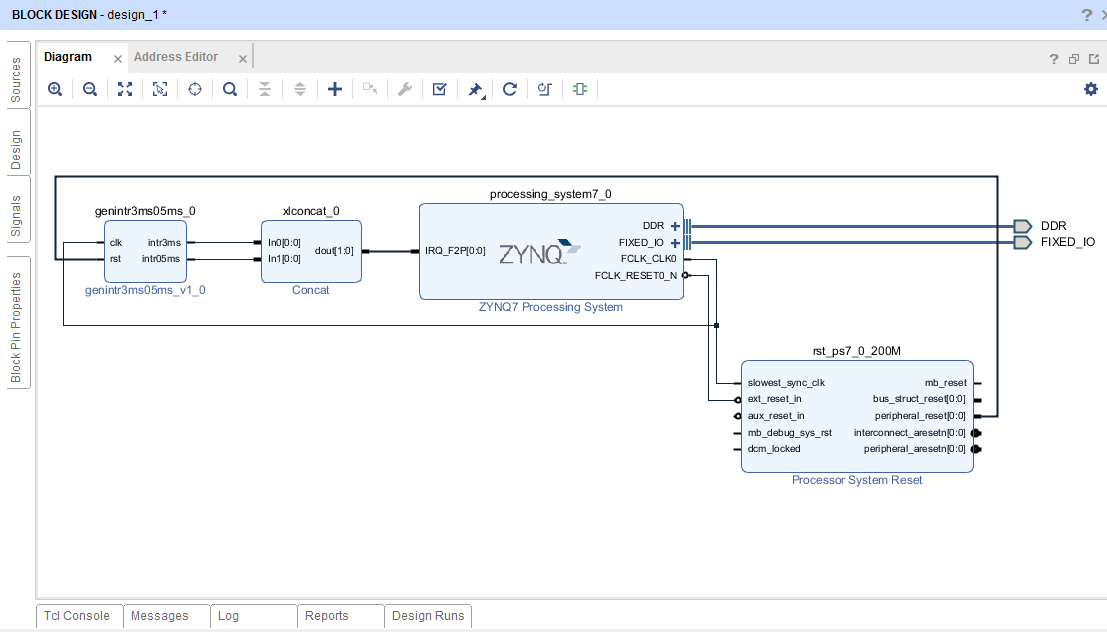

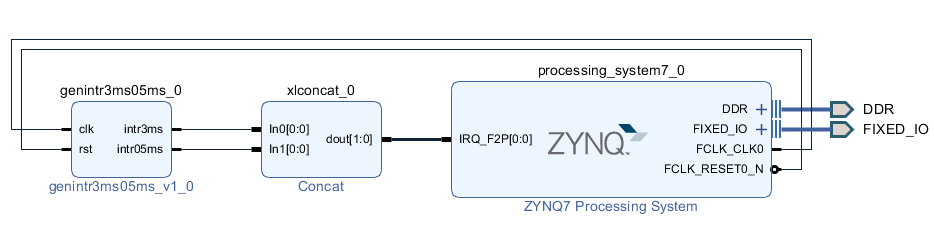

1.进入到 Create Block Design 中,输入 genintr3ms05ms 即可添加该自定义 IP

2.添加 ZYNQ,复位选上,时钟频率设置为 200Mhz,同时记得勾选中断

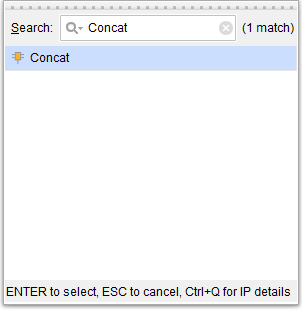

3.连线,两个中断,但只有一个接口,我们借用一个 Concat IP 即可

4.连线可以直接点击上方 Run 自动布线,会多出一个 Processor System Reset模块,中断复位是高有效,而ZYNQ复位是低有效,此模块会协调好。而手动布线则可能出错。

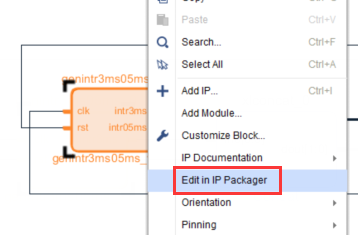

5.如果布线时发现自定义 IP 需要修改,可以选中该 IP,右键进入修改

之后就可以进入到SDK进行中断代码编写了,和普通PL中断是类似的。

参考资料:

[1]V3学院FPGA教程

ZYNQ笔记(6):普通自定义IP封装实现PL精准定时中断的更多相关文章

- ZYNQ笔记(7):AXI从口自定义IP封装

使用 AXI_Lite 从口实现寄存器列表的读写,并且自己封装为一个自定义 IP,以便以后使用.本次记录的是 M_AXI_GP0 接口,此接口是 ARM 作为主机,FPGA 作为从机,配置 FPGA ...

- Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core.通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core ...

- AXI-Lite总线及其自定义IP核使用分析总结

ZYNQ的优势在于通过高效的接口总线组成了ARM+FPGA的架构.我认为两者是互为底层的,当进行算法验证时,ARM端现有的硬件控制器和库函数可以很方便地连接外设,而不像FPGA设计那样完全写出接口时序 ...

- vivado设计三:一步一步生成自己的自定义IP核

开发环境:xp vivado2013.4 基于AXI-Lite的用户自定义IP核设计 这里以用户自定义led_ip为例: 1.建立工程 和设计一过程一样,见vivado设计一http://blog. ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- vivado设计四:自定义IP核测试

在vivado设计三中:http://blog.chinaaet.com/detail/37177已经建立了vivado工程和封装好了自定义IP核. 那么接下来,我们对这个自定义IP核进行测试了:我们 ...

- 强大的Vivado IP工具——自定义IP的使用

首先,要指出,本文不描述任何IP的功能与使用. 在开发一个大型FPGA项目时,多人协作是必不可少的.这个时候,如何提交设计给负责集成的人,是项目开发中最关键的问题之一. 常用的一个方法是,提交网表 ...

- asp.net mvc 自定义pager封装与优化

asp.net mvc 自定义pager封装与优化 Intro 之前做了一个通用的分页组件,但是有些不足,从翻页事件和分页样式都融合在后台代码中,到翻页事件可以自定义,再到翻页和样式都和代码分离, 自 ...

- 使用requireJS,backboneJS,和underscoreJS完成自定义模板封装

使用requireJS,backboneJS,和underscoreJS完成自定义模板封装 原来的代码 当我们进行一个列表的数据填充的时候,是这样做的: //获取美食列表 function getFo ...

随机推荐

- FCC-学习笔记 Pig Latin

FCC-学习笔记 Pig Latin 1>最近在学习和练习FCC的题目.这个真的比较的好,推荐给大家. 2>中文版的地址:https://www.freecodecamp.cn/;英文版 ...

- python3 内建函数filter

Python内建的filter()函数用于过滤序列. 和map()类似,filter()也接收一个函数和一个序列.和map()不同的是,filter()把传入的函数依次作用于每个元素,然后根据返回值是 ...

- android开发中json与java对象相互转换

json与java对象的相互转换.(使用com.google.gson) 在Android开发过程中,客户端总是需要从服务器获取数据,包括XML和json格式,目前json格式的数据使用较为普遍,所以 ...

- pymysql操作(老版本的,新版有基础不同)

导入库 import pymysql 创建链接 conn=pymysql.connect(host='127.0.0.1',port='3306',user='root',passwd='123456 ...

- spring-data-redis 关于订阅客户端不断创建新线程的问题

项目中使用了spring-data-redis 实现消息订阅功能,原来的配置是这样子: <redis:listener-container connection-factory="je ...

- Linux—— 记录所有登陆用户的历史操作记录

前言 记录相应的人登陆服务器后,做了那些操作,这个不是我自己写的,因为时间久了,原作者连接也无法提供,尴尬. 步骤 history是查询当前连接所操作的命令,通过编写以下内容添加至/etc/profi ...

- 【大数据】0002---MongoDB集群自动分离创建新集群

场景:MongoDB集群运行后,自动产生新的集群 解答:可能没有理解问题,理清思路如下 1.日志分析 2.配置文件检查(日期.版本) 3.网络IP变化 4.github 5.stack overflo ...

- jquery保存cookie,php读取cookie操作

//保存时间 var Days = 30; var exp = new Date(); exp.setTime(exp.getTime() + Days*24*60*60*1000); //保存内容, ...

- Centos7安装MySQL(多图)

文章目录 一.在线安装1.替换网易yum源2.清理缓存3.下载rpm文件4.安装MySQL数据库二.本地安装1.上传MySQL安装包2.安装依赖的程序包3.卸载mariadb程序包4.安装MySQL程 ...

- 动态规划:数字和为sum的方法数

题目描述 给定一个有n个正整数的数组A和一个整数sum,求选择数组A中部分数字和为sum的方案数.当两种选取方案有一个数字的下标不一样,我们就认为是不同的组成方案. 输入描述: 输入为两行: 第一行为 ...