Verilog小总结

Verilog小总结

基础

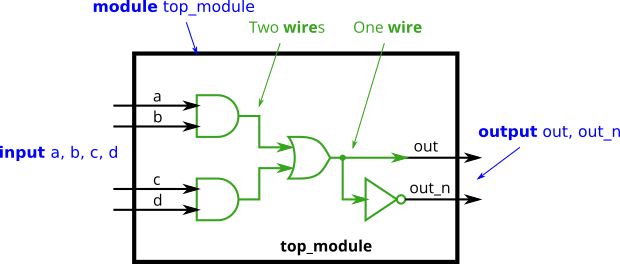

assign

assign作为一个组合逻辑常用的语句,可认为是将电线连接起来,当然它能做的不仅仅是将一个输入直接输出,它能把输入信号进行逻辑运算后再输出。当assign左右两边位宽不相等时,将自动进行零扩展或截断以匹配左边的位宽。

eg:

module top_module (

input a,

input b,

input c,

input d,

output out,

output out_n );

wire w1, w2; // Declare two wires (named w1 and w2)

assign w1 = a&b; // First AND gate

assign w2 = c&d; // Second AND gate

assign out = w1|w2; // OR gate: Feeds both 'out' and the NOT gate

assign out_n = ~out; // NOT gate

endmodule

Vectors

声明向量

type [upper:lower] vector_name;

type指定向量的数据类型,通常是wire或reg。如果要声明输入或输出端口,则该类型还可以另外包括端口类型(例如,input或output)

wire [7:0] w; // 8-bit wire

reg [4:1] x; // 4-bit reg

output reg [0:0] y; // 1-bit reg that is also an output port (this is still a vector)

input wire [3:-2] z; // 6-bit wire input (negative ranges are allowed)

output [3:0] a; // 4-bit output wire. Type is 'wire' unless specified otherwise.

wire [0:7] b; // 8-bit wire where b[0] is the most-significant bit.

部分选择

使用向量名称访问整个向量,但是当assign左右两边位宽不相等时,将自动进行零扩展或截断以匹配左边的位宽。

使用vector_name[up:low]的形式获取部分向量,注意方向应与定义的一致,如定义了一个a[3:0],那么不能反向获取a[0:3]。

矢量运算

- 位运算

| 符号 | 功能 |

|---|---|

~ |

按位取反 |

& |

按位与 |

| |

按位或 |

^ |

按位异或 |

^~ |

按位同或 |

注意:除了~外均为双目运算符;若进行双目运算时左右两个操作数位数不一样,位数少的将在相应的高位用0扩展。

- 逻辑运算

逻辑运算会将整个向量视为布尔值(真=非零,假=零),并且产生1位输出,如有input [2:0] a和input [2:0] b 那么他们的逻辑或运算即为assign out = a || b;,a和b均视为一个布尔值。

- 缩减运算

对一个向量的每一位进行位操作,如有a[2:0],那么b=&a相当于b=(a[0]&a[1])&a[2]

矢量串联

串联运算符{a,b,c}用来将小向量串联起来创建一个更大的向量。串联中不允许使用不定尺寸的常量。如{1,2,3}是非法的,因为Verilog不知道他们的位宽。

还可以用{n{vec}}的形式来复制向量,如{6{a}}和{a,a,a,a,a,a}是一样的,同时注意两组大括号都是必须的,即{1'b1,6{1'b0}}是非法的,因为其中的6{1'b0}少了一组大括号,正确的写法是{1'b1,{6{1'b0}}}。这其实比较好理解,串联运算符{a,b,c}中的abc均为一个向量,{n{vec}}也代表了一个向量,因此{a,b,{n{c}}}也是一个向量

模块

mod_name instance_name (signal_name1,signal_name2,signal_name3);//by position

mod_name instance_name (.port_name1(signal_name1),.port_name2(signal_name2),.port_name3(signal_name3));//by name

可以理解为一个函数,注意括号内的是外部连接到模块的信号。

always块

组合逻辑

使用always @(*)可以类似于assign的效果,当右方有变量发生改变时,左边输出随之立即改变。assign out1 = a & b | c ^ d; 和always @(*) out2 = a & b | c ^ d;是一样的

时序逻辑

- 同步与异步复位

//同步复位

always @(posedge clk) begin

if(reset == 1) begin

//reset

end

end

//异步复位

always @(posedge clk,posedge areset) begin

if(areset == 1) begin

//reset

end

end

- 阻塞赋值非阻塞赋值

一般来说,我们在组合逻辑的always块中使用阻塞赋值(x = y;);在时序逻辑的always块中使用非阻塞赋值(x <= y;)

case

always @(*) begin //这是一个组合逻辑

case (in)

1'b1: begin

out = 1'b1;

end

1'b0: out = 1'b0;

default: out = 1'bx;

endcase //一定记得写endcase

end

注意一定要写endcase。

另外还有case的好兄弟casez,他可以匹配形如4'bzzz1的向量,z表示无关位。

eg:优先编码器

module top_module (

input [7:0] in,

output reg [2:0] pos );

always @(*) begin

casez (in)

8'bzzzzzzz1 : pos = 0;

8'bzzzzzz1z : pos = 1;

8'bzzzzz1zz : pos = 2;

8'bzzzz1zzz : pos = 3;

8'bzzz1zzzz : pos = 4;

8'bzz1zzzzz : pos = 5;

8'bz1zzzzzz : pos = 6;

8'b1zzzzzzz : pos = 7;

default: pos =0;

endcase

end

endmodule

for

组合for循环

与C语言的用法类似。

eg:人口计数器

module top_module (

input [254:0] in,

output reg [7:0] out

);

always @(*) begin //组合逻辑always块

out = 0; //一定要初始化为0

for (int i=0;i<255;i++)

out = out + in[i];

end

endmodule

生成for循环

当对矢量中多个位进行重复操作时,或进行多个模块的实例化引用的重复操作时,可使用生成块简化程序。写法如下

genvar i;//只能用genvar作为循环变量

generate

for (i=1;i<99;i=i+1) begin: add_loop//这个名字是必须的

mod_name instance_name(......);//括号里写由i推出的信号

end

endgenerate

eg:Bcdadd100

module top_module(

input [399:0] a, b,

input cin,

output cout,

output [399:0] sum );

genvar i;

wire [99:0]cout1;

bcd_fadd mod1(a[3:0],b[3:0],cin,cout1[0],sum[3:0]);

generate

for (i=1;i<99;i=i+1) begin: addloop

bcd_fadd mod2(a[(4*i+3):(4*i)],b[(4*i+3):(4*i)],cout1[i-1],cout1[i],sum[(4*i+3):(4*i)]);

end

endgenerate

bcd_fadd mod3(a[399:396],b[399:396],cout1[98],cout,sum[399:396]);

endmodule

状态机写法

Moore型

三段式写法:使用一个state用于存当前状态,使用一个next_state用于存下一状态。第一段用于写状态转换逻辑,第二段用于状态转移,第三段用于输出。

reg state, next_state;

//第一段:

always @(*) begin //一个组合逻辑always块,用于写状态转换逻辑,当in改变时,next_state将立即改变。

case(state)

A: next_state = f(in)//关于in的函数

B: next_state = f(in)

...

endcase

end

//第二段(异步):

always @(posedge clk, posedge areset) begin

if(areset == 1) begin

state <= 0;//reset

end

else state <= next_state;

end

//第二段(同步):

always @(posedge clk) begin

if(reset == 1) begin

state <= 0;//reset

end

else state <= next_state;

end

//第三段(assign法)

assign out = (state == ...);//判断state

//第三段(组合逻辑always块法)

always@(*) begin

case (state)

A: {out3,out2,out1} = 3'b111;

B: {out3,out2,out1} = 3'b110;//对每一种状态输出

...

endcase

end

Mealy型

仅仅第三段发生了改变,可使用{state,in}来做输出判断。

//第三段(assign法)

assign out = f(state,in);//关于state和in的函数

//第三段(组合逻辑always块法)

always@(*) begin

case ({state,in})

4'b0000: {out3,out2,out1} = 3'b111;

4'b0001: {out3,out2,out1} = 3'b110;//对每一种state与in做输出

...

end

(希望明天P1能过呜呜呜

Verilog小总结的更多相关文章

- Windows上使用iverilog+gtkwave仿真

主要参考了: https://www.cnblogs.com/lsgxeva/p/8280662.html 谢谢! ------------------------------------------ ...

- verilog学习笔记(1)_两个小module

第一个小module-ex_module module ex_module( input wire sclk,//声明模块的时候input变量一定是wire变量 input wire rst_n,// ...

- Verilog中关于wire使用的一些小知识

1.Verilog中如果wire连接到常量,而常量没有说明他的位宽,那么将会默认为32位 如: input [:] x ; wire [:] a; assign a = + x; 上述代码在综合的时候 ...

- verilog 实用的小技巧

(之后还会持续的更新) 移位操作的实现: verilog有一种非常简单的移位操作实例如下: reg [3:0] source; reg out; {out,source[3:0]}={source[3 ...

- verilog学习笔记(3)_task/case小例子及其tb

module ex_case `timescale lns/1ns module ex_case( input wire rst_n, input wire sclk, output reg [7:0 ...

- verilog学习笔记(2)_一个小module及其tb

module-ex_cnt module ex_cnt( input wire sclk, input wire rst_n, output wire[9:0] cnt ); reg [9:0] cn ...

- Verilog HDL小练习

5s内15Hz4个LED闪烁,再两秒熄灭,循环往复. 引入en,可以使得4个LED灯全亮,以及恢复周期变化. module led(clk_27MHZ, en, led1, led2, led3, l ...

- verilog $fopen 函数的小缺陷

system task $fopen 的argument 为1.文件名字(可以包含具体的文件路径但是注意用)2.打开方式比如"r"."w"."a&qu ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

随机推荐

- Linux安装软件方法总结

相比于windows系统,Linux安装程序就比较复杂了,很多需要root用户才能安装.常见的有以下几种安装方法 源码安装 rpm包安装 yum安装 (RedHat.CentOS) apt-get安装 ...

- Java知识系统回顾整理01基础05控制流程04 for

一.for 比较for和while public class HelloWorld { public static void main(String[] args) { //使用while打印0到4 ...

- 《穷查理年鉴》金钱 & 生意 & 律师(关于金钱)

金钱 025.钱还得快才会借得快. 030.钱和人有着复杂的友谊:人能让钱变坏,钱也能让人变坏. 034.绝望增加债务,勤奋偿还债务. 037.只有一无所有的人才会没有烦恼. 049.穷人为他的胃找食 ...

- 用于ASP.net的MVC模块

下载MVCBricks_SRC - 492.58 KB 表的内容 介绍系统要求游戏闪屏的最终考虑历史 介绍 自从我写上一篇关于ASP的文章以来,已经有很长时间了.净的话题.这次我决定写一些关于它的东西 ...

- Eating Peach (peach)

Description On this day, the little monkey went looking for food. He came to a rectangular peach gar ...

- ansible-playbook模板化(jinja2)

1. ansible-playbook模板化(jinja2)条件与循环 1.1) jinja使用结构图 2. 编写jinja2的循环 2.1) 编写jinja2模板 1 [root@test-1 ...

- Python+Appium自动化测试(14)-yaml配置Desired capabilities

一,前言 在之前的appium自动化测试示例中,我们都是把构造driver实例对象的数据(即Desired Capabilities)写在业务代码里,如下: # -*- coding:utf-8 -* ...

- day19 Pyhton学习 递归函数

# 函数的递归 : 在一个函数的内部调用它自己 # import sys # sys.setrecursionlimit(1000000) # 设置递归的最大深度 # 总结 # 1.递归函数的定义 : ...

- 快速掌握ES6语法

常量变量 let and const 先说说常量和变量的概念吧, 常量是说那种进行一次赋值后不会更改的值,比如说游戏账户的 ID, 变量是说赋值后有更改的需求的,比如游戏名,游戏密码. 在之前的 Ja ...

- 【UER #1】DZY Loves Graph

UOJ小清新题表 题目内容 UOJ链接 DZY开始有\(n\)个点,现在他对这\(n\)个点进行了\(m\)次操作,对于第\(i\)个操作(从\(1\)开始编号)有可能的三种情况: Add a b: ...