03-ASIC和FPGA中的时钟结构

1 ASIC 中时钟的结构

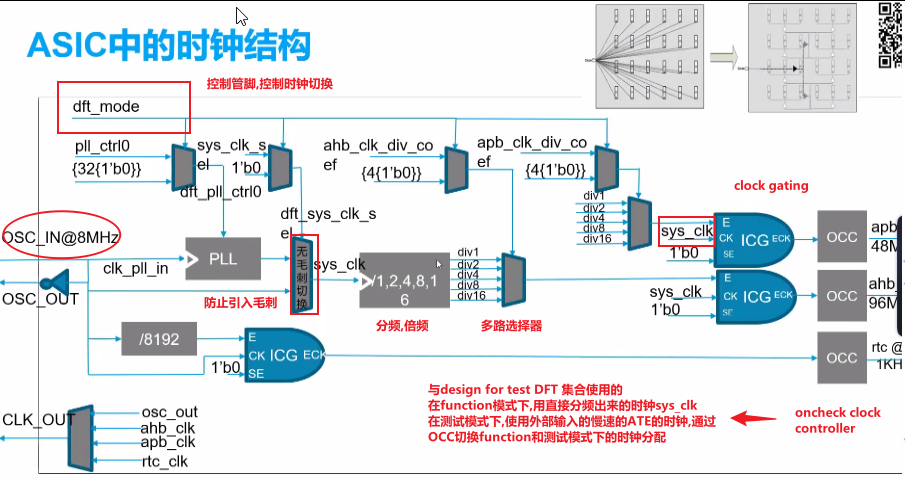

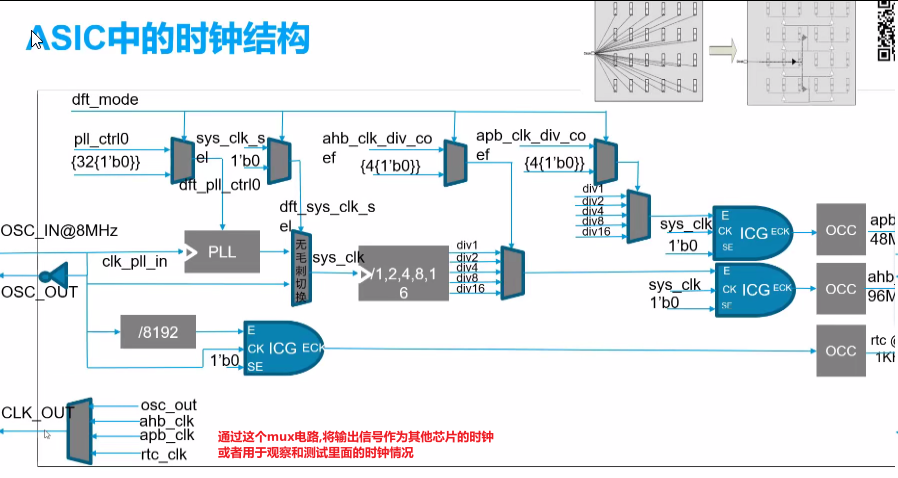

ASIC电路中的时钟的结构。这是一个非常典型的MCU的时钟结构图。它的时钟结构和功能的划分。首先,我们通过外部振荡器发送了一个8MHz的时钟给PLL,经过分分频和倍频产生更多的一些时钟。这些时钟再经过一些多路选择器来送给后面的电路。从上图里面看,我们把它做了1,2,4,8,16的分频。

送给后面的时钟以后我们这里面有个ICG,也称作门控时钟。来控制这个时钟在什么时间关断和打开,门控时钟输出了以后,接的这个OCC(oncheck clock controller)。它的作用是和design for test dft来结合来使用的。也就是说,在function模式或者功能的模式下,用直接接的分频出来的时钟system clock时钟。

如果在测试模式下,可能要用外部输入的慢速的ATE时钟,那么通过这个OCC的逻辑来选择或者是切换function模式和test模式下时钟的分配。这个切换的模式,就用dft的模式。dft模式是一个控制管脚,可以控制相关的时钟切换。在切换的过程中,我们为了防止切换导致或者引入一些毛刺时钟。我们有一个无毛刺切换电路来切换function和测试模式,时钟。

这些输出也可以通过这个mux电路来把输出作为其他的芯片的时钟,或者是说我们来观测观察我们这个时钟里面的情况。

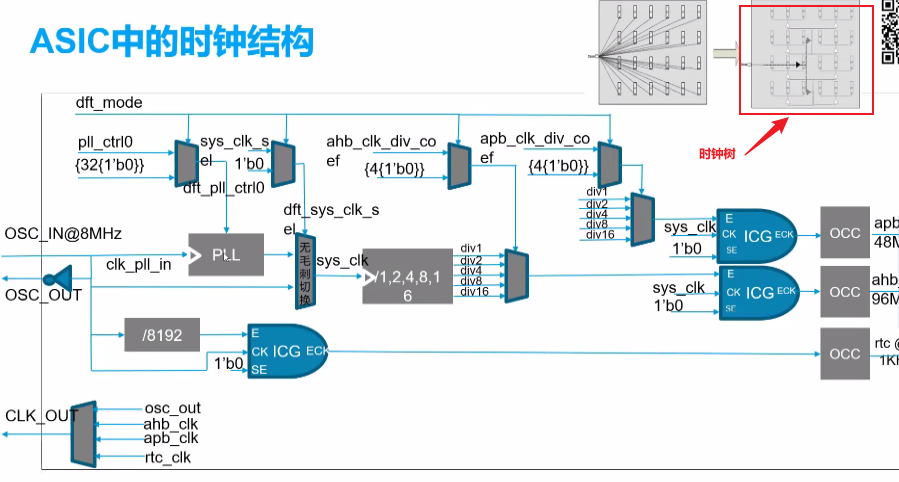

在ASIC设计中有一个重要的概念,就是叫clock tree synthesis。我们简称为CTS。逻辑上,时钟会接到寄存器的时钟端,它是一个网状的结构。为了达到功能的正确或者时序的正确,期望时钟到达各个寄存器的延迟信息差不多。那么根据要求,我们就可以插入buffer,相当于一个大树,有树枝树叉,这样的一个结构。可以来确保我们源头时钟到各个寄存器的时钟的延迟差不多。这就叫clock tree synthesis,这是在ASIC设计中的一个重要的特点。

在ASIC设计中有很多的时钟,这里面就有一个问题,对这些时钟,各个时钟打出的信号之间该怎么处理呢?或者clock 1送给另外一个时钟clock 2它们之间有什么样的情况会导致功能出错。这是我们在ASIC设计中非常重要观念。

2 FPGA 中时钟的结构

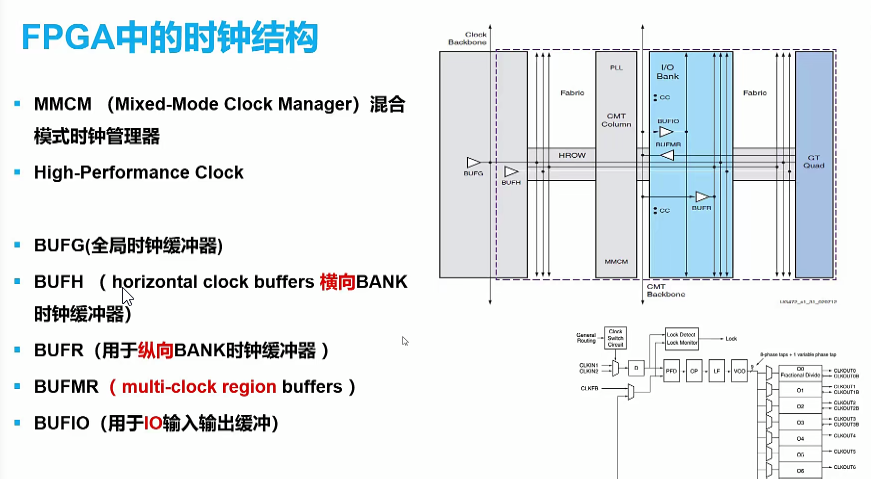

下面我们讲一下FPGA中的使用的结构。FPGA的时钟结构和ASIC时钟结构是不一样的,为什么呢?ASIC设计可以通过后端的工具来插入clock tree和很多的处理功能,定制化的来做相关的电路时钟的处理。而FPGA中时钟的驱动电路和它的连接资源,其实在FPGA中已经把它做好了。你只能利用它或者调用它。用它的功能来完成相关时钟的驱动或者是分配。

首先,我们有MMCM,我们称之为混合模式的时钟管理器。它里面包含了锁相环,也会产生多个不同的时钟输出。这个输出可以分频倍频以及相位的调整。在一个FPGA里面,有很多个MMCM这些管理模块,也就是说它可以给你提供很多个时钟信号。时钟产生了以后,我们要通过一些时钟缓冲器。

bufferG全局时钟缓冲器。全局时钟缓冲器,它可以驱动FPGA中全局的时钟线路,也就是说它可以连接到在不同的位置的寄存器。

bufferH是横向组的时钟缓冲器,可以把它理解成为一个局域的局部的一个时钟区域驱动。bufferR用于纵向的组的时钟缓冲区,你也可以把它理解为一个局部区域的时钟。

bufferMR,它是multi clock region buffers,就是它可以驱动多个时钟域。

bufferIO,它只能用于驱动IO里面的相关的时钟。

bufferH和bufferR,也可以驱动lO里面相关的时钟。所以这就是bufferH,bufferR,bufferIO它的区别之一。

在实际电路设计中,要充分考虑或者要充分的了解你这个FPGA中里面它有多少个全局的缓冲区?有多少个bufferH,bufferR, bufferMR,bufferIO?来决定通过什么样的方式应用它来驱动相关的逻辑电路。

同步时钟异步处理

如果在ASIC设计中做好以后,很多设计要转到FPGA上,这时候该怎么处理呢?首先如果在ASIC这个设计中,很多时钟可能是同源时钟,但是它跨越了很多的时钟域。有时候我们为了更简单或者更方便的布局布线或者做clock tree。在设计中也会按异步对这些同源时钟

来做处理。也就是说,原是同步的时钟,但是,因为考虑到布局布线要多次迭代。这样的话,这个时间和效果可能不是很好,也把这些同源的时钟的关系作为一些异步处理。可以节省后端迭代的次数,进而可以缩短开发的周期。当然,代价是增加了一部分的设计面积,但这个代价在设计里面,往往可以,折中的考虑。

MMCM代替ASIC中时钟产生电路

(2)如果ASIC设计转到FPGA的时候,如果已经做了同步时钟的处理的话,仅需要在时钟产生模块的输出中给每个时钟都插入bufferG,就可以使每个生成时钟域的时钟偏差最小。但是,如果电路里面有很多倍频分频生成的时钟,在ASIC设计中,这时候我们可以充分利用FPGA里面的时钟产生模块,比如我们的MMCM。把我们这些ASIC设计中的时钟产生电路用MMCM或者PLL锁相环来替代。也就是说我们不用ASIC中时钟产生电路,直接用MMCM里面的模块来帮我们产生对应的分频或者倍频的一些时钟,这样我们再把这些时钟通过bufferG再进入各个模块,这样效果会更好一点。

扇出少的信号,不适用bufferG

(3)如果生成的时钟较多,但是每个时钟的扇出并不是很大。这时候按理说用bufferG来做时钟的驱动会更好。或者是用bufferH或bufferMR来做启动驱动比较好。但是,有一个小的问题,因为在FPGA中布线资源连接关系都布好了,需要把它通过一些连接来配置它。如果你扇出小的信号,一般不需要利用全局缓冲器的大驱动,为什么呢?因为你时钟生成的逻辑,如果处于普通的CLB中,从CLB到全局的时钟线,再到bufferG,然后再经过全局时钟线,进入本地的连线直接要驱动的目标的寄存器,这个路径会很长。此时,时钟源和它其他的生成的时钟,以及它们再生成的时钟的偏移会比较大。即我们用bufferG,并没有减到或者减减小,或者说体现减小时钟偏差的作用。这时候如果你不使用bufferG布局布线,使用FPGA里面的布局布线工具会自动的把相关的逻辑放在很近的位置。虽然我们。使用的是较慢的本地的逻辑的连线,但是由于路径短,经过的开关少时钟的偏差反而较小。

03-ASIC和FPGA中的时钟结构的更多相关文章

- 【转】关于FPGA中建立时间和保持时间的探讨

时钟是整个电路最重要.最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错:因而明确FPGA设计中决定系统时钟的因素,尽 ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA学习之基本结构

如何学习FPGA中提到第一步:学习.了解FPGA结构,FPGA到底是什么东西,芯片里面有什么,不要开始就拿个开发板照着别人的东西去编程.既然要开始学习FPGA,那么就应该从其基本结构开始.以下内容是我 ...

- FPGA中竞争冒险问题的研究

什么是竞争冒险? 1 引言 现场可编程门阵列(FPGA)在结构上由逻辑功能块排列为阵列,并由可编程的内部连线连接这些功能块,来实现一定的逻辑功能. FPGA可以替代其他PLD或者各种中小规模数 ...

- FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会.硬件逻辑实现的除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成.因此FPGA实现除法运算并不是一个&qu ...

- FPGA中计数器设计探索

FPGA中计数器设计探索,以计数器为32位为例: 第一种方式,直接定义32位计数器. reg [31:0]count; quartus ii 下的编译,资源消耗情况. 85C模型下的时钟频率. 0C模 ...

- 低成本FPGA中实现动态相位调整

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的.ALTERA的高端FPGA,如STRATIX(r) 系列中自带有DPA电路,但低端的F ...

- FPGA中的“门”

逻辑门 在ASIC的世界里,衡量器件容量的常用标准是等效门.这是因为不同的厂商在单元库里提供了不同的功能模块,而每个功能模块的实现都要求不同数量的晶体管.这样在两个器件之间比较容量和复杂度就很困难. ...

- 理解FPGA中的RAM、ROM和CAM;ROM、RAM、DRAM、SRAM、FLASH

目前大多数FPGA都有内嵌的块RAM(Block RAM),可以将其灵活地配置成单端口RAM(DPRAM,Single Port RAM).双端口RAM(DPRAM,Double Ports RAM) ...

- 数字设计中的时钟与约束(gate)

转载:https://www.cnblogs.com/IClearner/p/6440488.html 最近做完了synopsys的DC workshop,涉及到时钟的建模/约束,这里就来聊聊数字中的 ...

随机推荐

- 【Python】【OpenCV】轮廓检测

Code: 1 import cv2 2 import numpy as np 3 4 img = np.zeros((200, 200), dtype=np.uint8) 5 img[50:150, ...

- 安装Office

安装Office 第一步 访问: https://otp.landian.vip/zh-cn/ 点击立即下载 选择: 第二步 打开下载好的zip,解压,启动程序 第三步 选择部署(在这里可以看到电脑已 ...

- CentOS7 安装Python3.9以上版本时。编译报错,原因是openssl版本低

openssl-1.1.1安装 1.前因 python 导入clickhouse_driver需要import ssl和_ssl,报错 File"/home/oracle/python3/l ...

- springsecurity 使用浅谈(一)

1. 背景 springsecurity框架主要用于Web应用的认证和授权.所谓认证就是验证当前访问系统的是不是本系统的用户,并且要确认具体是哪个用户.而授权就是经过认证后判断当前用户是否有权 限进行 ...

- 22、Scaffold属性 抽屉菜单Drawer

在Scaffold组件里面传入drawer参数可以定义左侧边栏,传入endDrawer可以定义右侧边栏.侧边栏默 认是隐藏的,我们可以通过手指滑动显示侧边栏,也可以通过点击按钮显示侧边栏. class ...

- 一文详解kube-apiserver认证鉴权能力

本文分享自华为云社区<kube-apiserver认证鉴权能力>,作者: 可以交个朋友. HTTPS为什么要进行身份验证 首先不管是kubectl还是API调用都是通过HTTPS访问kub ...

- 细说SQL与ETL之间的小秘密

本文分享自华为云社区<GaussDB数据库SQL系列-SQL与ETL浅谈>,作者:Gauss松鼠会小助手2. 一.前言 在SQL语言中,ETL(抽取.转换和加载)是一种用于将数据从源系统抽 ...

- AIGC的阿克琉斯之踵

摘要:现在,越来越多的企业和个人使用AIGC生成文章.图片.音乐甚至视频等内容,AIGC已经成为一种必备的工具.在游戏和原画师行业,甚至已经出现了第一批因为AI而失业的人. 本文分享自华为云社区< ...

- 如果云是水滴,Kubernetes就是水滴管理平台

摘要:云是由很多小水滴组成的,把每一个计算机想象成小水滴,联合起来就形成了云.一般水滴先出现,然后出现管理水滴的平台(如OpenStack,Kubernetes). 一.云计算–独立宇宙 1.云是由很 ...

- 10年经验总结,华为fellow教你如何成为一名优秀的架构师?

摘要:华为云首席架构师分享成为架构师必备的一些特质和能力. 本文分享自华为云社区<10年经验总结,华为fellow教你如何成为一名优秀的架构师?>,作者: 技术火炬手 . 在<云享人 ...