低成本FPGA中实现动态相位调整

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自带有DPA电路,但低端的FPGA,如CYCLONE(r)系列中是没有的。下面介绍如何在低端FPGA中实现这个DPA的功能。

实现架构

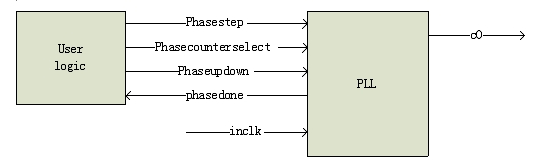

在LVDS输入接收时,时钟和数据的相位可能是不确定的,因此我们需要将时钟的相位作出调整,使得时钟能稳定的采集到输入数据。工作的核心就是用锁相环PLL的相位调整功能,产生若干个时钟的不同相位,看哪些相位能准确的采集到输入数据,然后取窗口中间的一个时钟相位,作为正常工作时的采样时钟。比如通过PLL产生0,45,90,135,……,315度8个相移的时钟,如果0,45,90度相移的时钟能正确采样到输入,那么最后选取中间相位,即45度的时钟作为采样时钟。这样接口上具有最大的时序裕量,从而保证链路的可靠性。下图为这个设计的基本结构,通过PLL调整相位的接口,产生了时钟的不同相位来采集数据,最后选择一个最合适的相位。

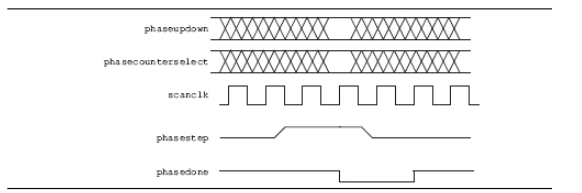

CYCLONE系列的PLL的相位调整接口时序如下图所示:

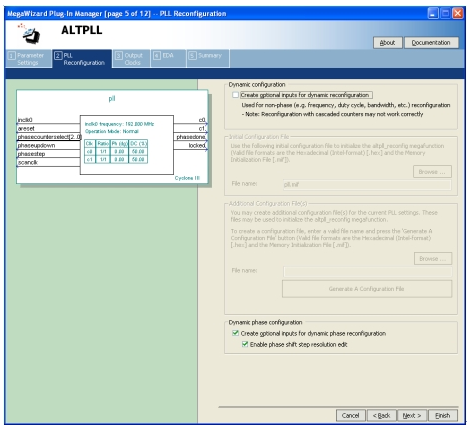

当用户逻辑控制phasestep, phasecounterselect与phaseupdown信号时,PLL的输出时钟C0就改变一次相位。在QII生成PLL时,用户必须选上create optional inputs for dynamic phase reconfigure,否则缺省是不会有这些管脚的,如下图所示。另外必须在output clock tab中写入phase shift step resolution的值,这样才能确定每次相位调整的步长。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

低成本FPGA中实现动态相位调整的更多相关文章

- FPGA中IBERT核的应用(转)

https://wenku.baidu.com/view/50a12d8b9ec3d5bbfd0a74f7.html (必看) 摘要 IBERT即集成式比特误码率测试仪,是Xilinx专门用于具 ...

- FPGA中竞争冒险问题的研究

什么是竞争冒险? 1 引言 现场可编程门阵列(FPGA)在结构上由逻辑功能块排列为阵列,并由可编程的内部连线连接这些功能块,来实现一定的逻辑功能. FPGA可以替代其他PLD或者各种中小规模数 ...

- 理解FPGA中的RAM、ROM和CAM;ROM、RAM、DRAM、SRAM、FLASH

目前大多数FPGA都有内嵌的块RAM(Block RAM),可以将其灵活地配置成单端口RAM(DPRAM,Single Port RAM).双端口RAM(DPRAM,Double Ports RAM) ...

- 巧用FPGA中资源

随着FPGA的广泛应用,所含的资源也越来越丰富,从基本的逻辑单元.DSP资源和RAM块,甚至CPU硬核都能集成在一块芯片中.在做FPGA设计时,如果针对FPGA中资源进行HDL代码编写,对设计的资源利 ...

- 深入理解javascript中的动态集合——NodeList、HTMLCollection和NamedNodeMap

× 目录 [1]NodeList [2]HTMLCollection [3]NamedNodeMap[4]注意事项 前面的话 一说起动态集合,多数人可能都有所了解.但是,如果再深入些,有哪些动态集合, ...

- Quartz 在 Spring 中如何动态配置时间--转

原文地址:http://www.iteye.com/topic/399980 在项目中有一个需求,需要灵活配置调度任务时间,并能自由启动或停止调度. 有关调度的实现我就第一就想到了Quartz这个开源 ...

- ZBrush中的动态网格该怎么进行运用

DynaMesh是ZBrush最新的基础模型创建工具,该命令用于基本模型的起稿到中模的制作.使用DynaMesh完全不启用考虑模型的拓扑,可以从一个图形拉扯出整个模型的分支,本文将以一个实例简单介绍Z ...

- (待续)C#语言中的动态数组(ArrayList)模拟常用页面置换算法(FIFO、LRU、Optimal)

目录 00 简介 01 算法概述 02 公用方法与变量解释 03 先进先出置换算法(FIFO) 04 最近最久未使用(LRU)算法 05 最佳置换算法(OPT) 00 简介 页面置换算法主要是记录内存 ...

- FPGA中的delay与latency

delay和latency都有延迟的意义,在FPGA中二者又有具体的区别. latency出现在时序逻辑电路中,表示数据从输入到输出有效经过的时间,通常以时钟周期为单位. delay出现在组合逻辑电路 ...

随机推荐

- 多线程-模拟阻塞queue队列

前阵子学习了多线程,现在进行总结一下,模拟队列. 分析问题: (1)首先需要一个容器存放元素,这里用linkedList队列. (2)每次像容器中添加或删除元素的时候需要计数,所以这里需要一个计数器, ...

- WebSocket相关

原文:http://www.cnblogs.com/jinjiangongzuoshi/p/5062092.html 前言 今天看了一些资料,记录一下心得. websocket是html5引入的一个新 ...

- 自己用java实现飞鸽传书 2 - 实现文件传输

第二步:实现文件传递. 上一步只是从服务端传递了一个字符串到客户端,这次需要对代码进行调整,实现从服务端获取文件,在客户端将文件存入目标地址. 调整后的代码: 服务端: import java.io. ...

- PowerDesigner之SQL表格设计

设计表格我觉得用PowerDesigner比起在SQL Server中设计表格简单快捷许多. 首先,我们新建一个Model(可以使用快捷键Ctrl + N) 在PowerDesigner中侧边栏有浮动 ...

- MongoDB在linux下的启动

最近公司数据库用到MongoDB,而之前只关注知道它是分布式非关系数据库,数据以文档的形式存储,数据格式是类似json的bson格式.而对于具体用法以及java如何调用并没有过多接触,今天花费一天的时 ...

- Go-gin CORS 跨域中间件

原文:https://stackoverflow.com/questions/29418478/go-gin-framework-cors func CORSMiddleware() gin.Hand ...

- Docker 简单应用

Docker 允许你在容器内运行应用程序, 使用 docker run 命令来在容器内运行一个应用程序. 输出Hello world runoob@runoob:~$ docker run ubunt ...

- 【枚举】【最小生成树】【kruscal】bzoj3754 Tree之最小方差树

发现,若使方差最小,则使Σ(wi-平均数)2最小即可. 因为权值的范围很小,所以我们可以枚举这个平均数,每次把边权赋成(wi-平均数)2,做kruscal. 但是,我们怎么知道枚举出来的平均数是不是恰 ...

- SSM三大框架整合(Spring+SpringMVC+MyBatis)

一. 导包 18个必须的包 二.配置Spring MVC的web文件 <?xml version="1.0" encoding="UTF-8"?> ...

- make和makefile介绍

<strong>先附上一个比较简单的,测试代码用的Makefile</strong> </pre><pre code_snippet_id="463 ...