Verilog实现奇分频电路

在FPGA中,计数器电路用途很广,一般计数器电路都可作为分频电路。实现占空比为50的偶分频电路很好实现。但实现占空比为50的奇分频电路有点难度。下面给出一个简单例子,记录学习奇分频电路的过程。

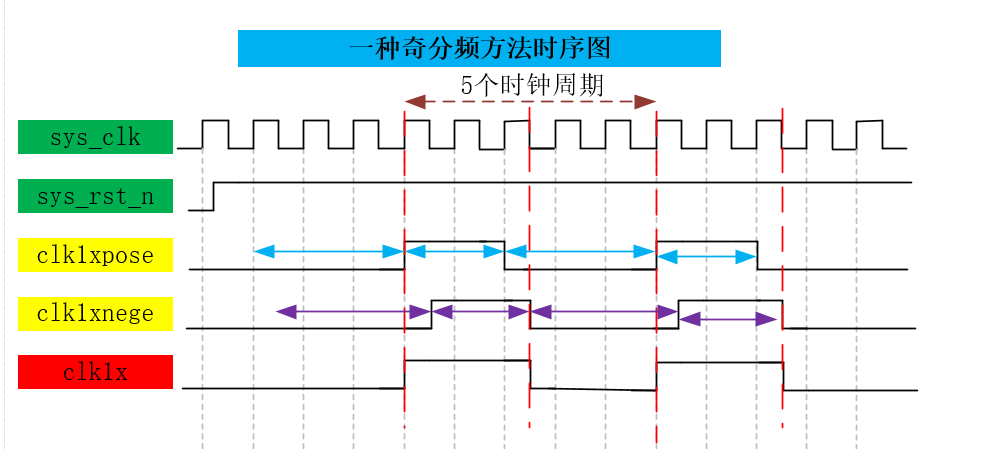

实现占空比为50的5分频电路,高低电平应都为2.5个时钟周期。即应当在上升沿和下降沿都要采样,这样才会产生出0.5个时钟周期的差。

公式为 奇分频 N 边沿的采集 每隔 N/2 翻转 和 每隔 N-1 翻转。

仿真波形图如下所示:

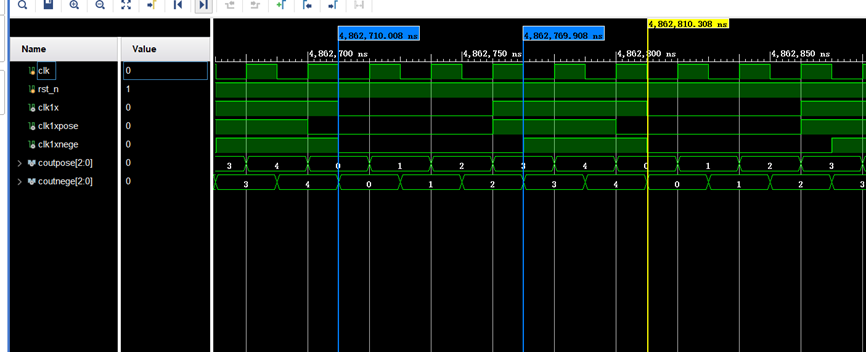

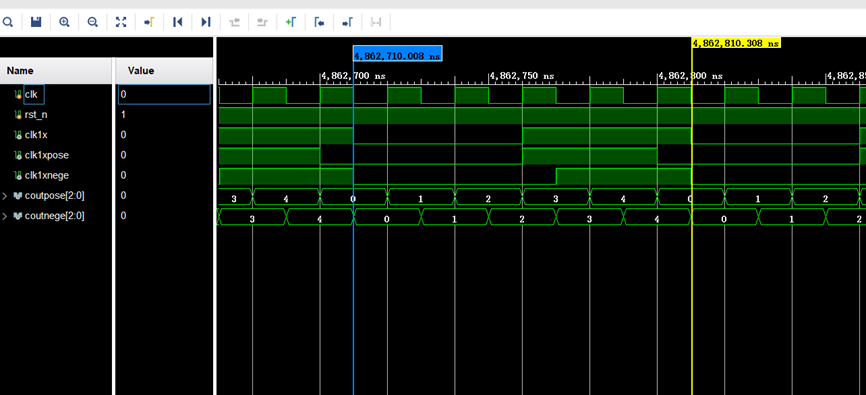

上升沿:

下降沿:

整体:

其中在上升沿采集中,低电平持续3个时钟周期,高电平持续2个时钟周期。其中在下升沿采集中,低电平持续3个时钟周期,高电平持续2个时钟周期。上升沿与下降沿之间错0.5个时钟周期,即整体为2.5+2.5=5。以后奇分频都可以这样操作。

下附代码和测试激励。

module divfreq(

input clk,

input rst_n,

output clk1x,

output reg clk1xpose,

output reg clk1xnege,

output reg [2:0] coutpose,

output reg [2:0] coutnege

);

parameter N=5;

parameter div1 = N/2 , div2 = N-1; // div1 = 5 / 2, div2 = 5 - 1 always@(posedge clk or negedge rst_n) //上升沿触发波形

begin

if(!rst_n)

clk1xpose = 0;

else if(coutpose == div1)

clk1xpose = ~clk1xpose;

else if(coutpose == div2)

clk1xpose = ~clk1xpose;

else

clk1xpose = clk1xpose;

end always@(negedge clk or negedge rst_n) //下降沿触发波形

begin

if(!rst_n)

clk1xnege = 0;

else if(coutnege == div1)

clk1xnege = ~clk1xnege;

else if(coutnege == div2)

clk1xnege = ~clk1xnege;

else

clk1xnege = clk1xnege;

end always@(posedge clk or negedge rst_n) //上升沿计数5

begin

if(!rst_n)

coutpose = 0;

else if(coutpose == div2)

coutpose = 0;

else

coutpose = coutpose + 1;

end always@(negedge clk or negedge rst_n) //下降沿计数5

begin

if(!rst_n)

coutnege = 0;

else if(coutnege == div2)

coutnege = 0;

else

coutnege = coutnege + 1;

end assign clk1x = clk1xpose | clk1xnege; //输出波形 endmodule

`timescale 1ns/1ns

module tb_divfreq (); reg clk ;

reg rst_n ;

wire clk1x ;

wire clk1xpose ;

wire clk1xnege ;

wire [2:0] coutpose ;

wire [2:0] coutnege ; initial

begin

clk = 1'b1 ;

rst_n <= 1'b0 ;

#10

rst_n <=1'b1 ;

end always #10 clk=~clk; divfreq divfreq_inst (

.clk (clk) ,

.rst_n (rst_n) ,

.clk1x (clk1x) ,

.clk1xpose (clk1xpose) ,

.clk1xnege (clk1xnege) ,

.coutpose (coutpose) ,

.coutnege (coutnege)

); endmodule

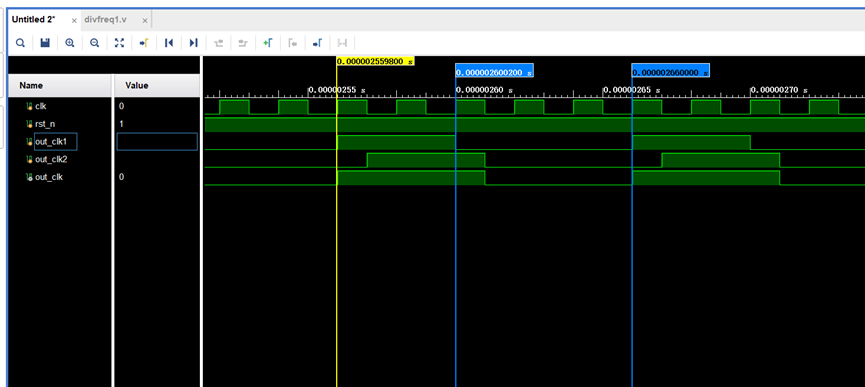

后附正点原子中的另外一种代码风格,但整体思路一致。

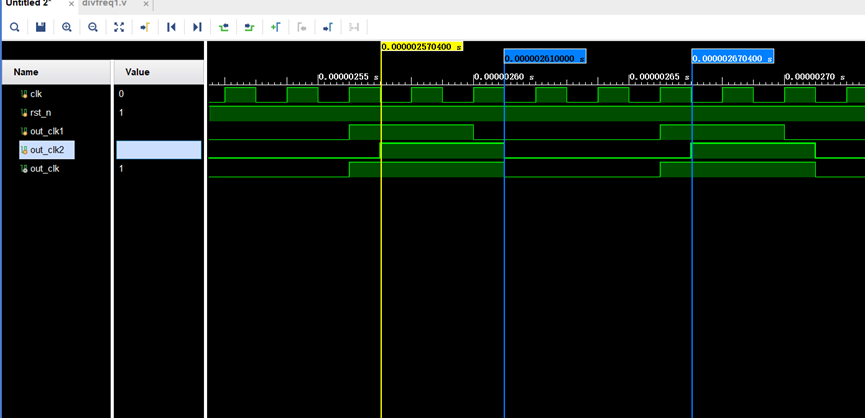

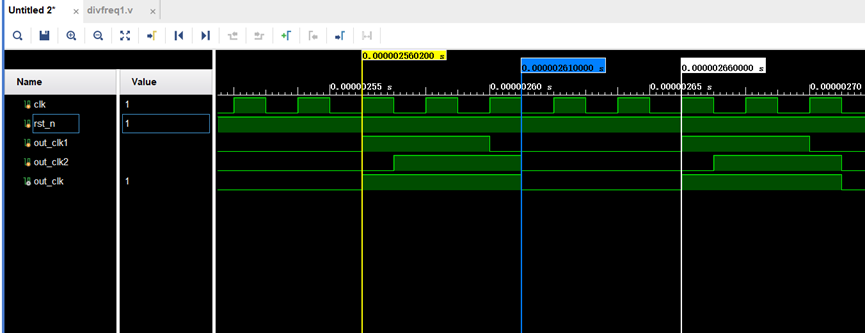

波形仿真:

上升沿:

下降沿:

整体:

后附正点原子奇分频代码和激励代码。

module divfreq1

(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

output out_clk // output signal

); parameter N = 5 ; reg [N/2 :0] cnt_1 ;

reg [N/2 :0] cnt_2 ; reg out_clk1 ;

reg out_clk2 ; //=====================================================================

// ------------------------- MAIN CODE -------------------------------

//=====================================================================

always @(posedge clk or negedge rst_n) begin //上升沿输出 out_clk1

if(!rst_n) begin

out_clk1 <= 0;

cnt_1 <= 1; //这里计数器从 1 开始

end

else begin

if(out_clk1 == 0) begin

if(cnt_1 == N/2+1) begin

out_clk1 <= ~out_clk1;

cnt_1 <= 1;

end

else

cnt_1 <= cnt_1+1;

end

else if(cnt_1 == N/2) begin

out_clk1 <= ~out_clk1;

cnt_1 <= 1;

end

else

cnt_1 <= cnt_1+1;

end

end always @(negedge clk or negedge rst_n) begin //下降沿输出 out_clk2

if(!rst_n) begin

out_clk2 <= 0;

cnt_2 <= 1; //这里计数器从 1 开始

end

else begin

if(out_clk2 == 0) begin

if(cnt_2 == N/2+1) begin

out_clk2 <= ~out_clk2;

cnt_2 <= 1;

end

else

cnt_2 <= cnt_2+1;

end

else if(cnt_2 == N/2) begin

out_clk2 <= ~out_clk2;

cnt_2 <= 1;

end

else

cnt_2 <= cnt_2+1;

end

end assign out_clk = out_clk1 | out_clk2; //输出最后波形 endmodule

`timescale 1ns/1ns

module tb_divfreq1 (); reg clk ;

reg rst_n ;

wire out_clk ; initial

begin

clk = 1'b1 ;

rst_n <= 1'b0 ;

#10

rst_n <=1'b1 ;

end always #10 clk=~clk; divfreq1 divfreq1_inst

(

.clk (clk) , // system clock 50Mhz on board

.rst_n (rst_n) , // system rst, low active

.out_clk (out_clk) // output signal

); endmodule

参考资料:

1、正点原子逻辑设计指南

2、某奇分频笔试题

Verilog实现奇分频电路的更多相关文章

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- 你要的fpga&数字前端笔面试题都在这儿了

转自http://ninghechuan.com 你要的FPGA&数字前端笔面试题来了 FPGA&ASIC基本开发流程 题目:简述ASIC设计流程,并列举出各部分用到的工具. 勘误:C ...

- 基于verilog的分频器设计(奇偶分频原理及其电路实现:上)

在一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率太高)进行分频.分频器主要分为奇数分频,偶数分频,半整数分频和小数分频,在对时钟要求不是很严格的FPGA系统中 ...

- Verilog设计分频器(面试必看)

分频器是指使输出信号频率为输入信号频率整数分之一的电子电路.在许多电子设备中如电子钟.频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种 ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- 惠威的M200MK3的前级电子分频板

M200MKIII是惠威融合了尖端有源电子分频技术而诞生的全新产品:双4声道运算放大器.高档玻璃纤维电路板.全SMT制作工艺.红宝石滤波电容阵列.进口金属化聚丙稀分频电容.超大功率TDA7294功放芯 ...

- 时钟晶振32.768KHz为什么是15分频?

实时时钟晶振为什么选择是32768Hz的晶振,在百度上搜索的话大部分的答案都是说2的15次方是32768,使用这个频率的晶振,人们可以很容易的通过分频电路得到1Hz的计时脉冲.但是话有说回来了,2的整 ...

- Verilog分频器的设计

大三都要结束了,才发现自己太多东西没深入学习. 对于偶分频:(计数到分频数的一半就翻转) 注: 图中只用了一个计数器,当然也可以用多个: 图中只计数到需要分频的一半,当然也可计数到更多: 图中从第一个 ...

- FPGA基础(verilog语言)——语法篇

verilog语言简介 verilog语言是一种语法类似于c的语言,但是与c语言也有不同之处,比如: 1.verilog语言是并行的,每个always块都是同时执行,而c语言是顺序执行的 2.veri ...

随机推荐

- Win Pycharm + Appium + 真机 实现APP自动化

前言: 测试的APP:亿通行 手机型号:OPPO 系统:安卓10 一.安装Python3.x 1.直接登录Python官网https://www.python.org/,下载最新版本即可 2.安装Py ...

- Pwn系列之Protostar靶场 Stack1题解

(gdb) disasse main Dump of assembler code for function main: 0x08048464 <main+0>: push ebp 0x0 ...

- MySQL(Zip版)安装配置

MySQL官网下载地址:MySQL 将压缩包内文件夹解压至任意目录,以mysql-5.7.40版本为例 第一步 添加环境变量 将mysql-5.7.40-winx64文件夹内的bin文件夹添加到环境变 ...

- 2022-04-30:在无限的平面上,机器人最初位于 (0, 0) 处,面朝北方。注意: 北方向 是y轴的正方向。 南方向 是y轴的负方向。 东方向 是x轴的正方向。 西方向 是x轴的负方向。 机器人

2022-04-30:在无限的平面上,机器人最初位于 (0, 0) 处,面朝北方.注意: 北方向 是y轴的正方向. 南方向 是y轴的负方向. 东方向 是x轴的正方向. 西方向 是x轴的负方向. 机器人 ...

- ChatGPT Plugin开发setup - Java(Spring Boot) Python(fastapi)

记录一下快速模板,整体很简单,如果不接auth,只需要以下: 提供一个/.well-known/ai-plugin.json接口,返回openAI所需要的格式 提供openAPI规范的文档 CORS设 ...

- vue全家桶进阶之路16:自定义过滤器及开发插件

过渡 过渡(transition)是Vue提供的一种在元素在插入.更新或移除时,自动添加动画效果的方式.Vue提供了多种过渡效果,其中包括基于CSS动画的过渡,以及JavaScript过渡. 过渡可以 ...

- pywin32和wmi的安装和测试

E:\pyAPP\Madking\MadKingClient>python bin\NedStark.py collect_dataE:\pyAPP\Madking\MadKingClientT ...

- R 绘制 GWAS 研究的 Manhattan 图

曼哈顿图本质上是一个散点图,用于显示大量非零大范围波动数值,最早应用于全基因组关联分析(GWAS)研究展示高度相关位点.它得名源于样式与曼哈顿天际线相似(如下图). 近几年,在宏基因组领域,尤其是差异 ...

- 800名科学家Nature联名发文主张废除p值!

每年,全球有数百万学生修读统计学课程.随着世界上的数据量越来越大,统计学已成为越来越受欢迎的话题.如果大多数学生都从这门课中记住一点,那可能就是"统计显著性"和"p 值& ...

- .NET7 中Autofac依赖注入整合多层,项目中可直接用

一.配置Autofac替换内置DI 1.安装Nuget包:Autofac.Extensions.DependencyInjection 2.Program.cs中加上 builder.Host.Use ...