TCAM CAM 说明 原理 结构 Verilog 硬件实现

TCAM 三态内容地址查找存储器,CAM内容地址查找存储器。区别在于TCAM多了一级掩码功能,也就是说可以指定某几位是dont care。匹配的时候0,1都行的意思。

广泛应用于数据流处理领域,本文简要介绍TCAM和CAM的逻辑组成和Verilog实例。

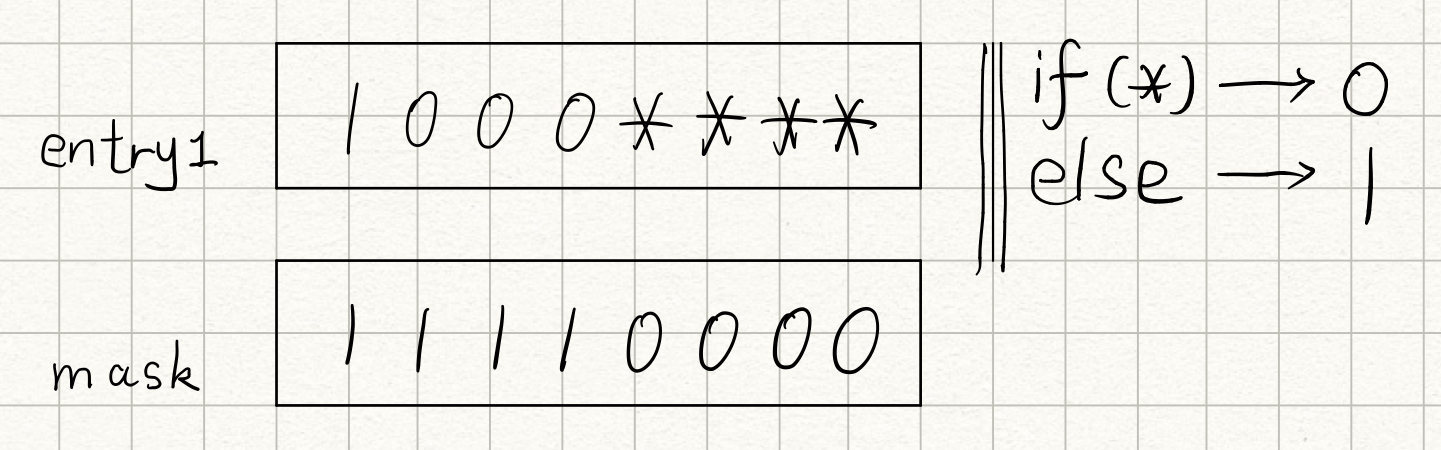

TCAM对于一个带mask的表项,如:“1000 * * * * ”。

为表达流表项,我们在下载流表之前我们需要做一步计算,

首先将其分解为entry1 和 mask:

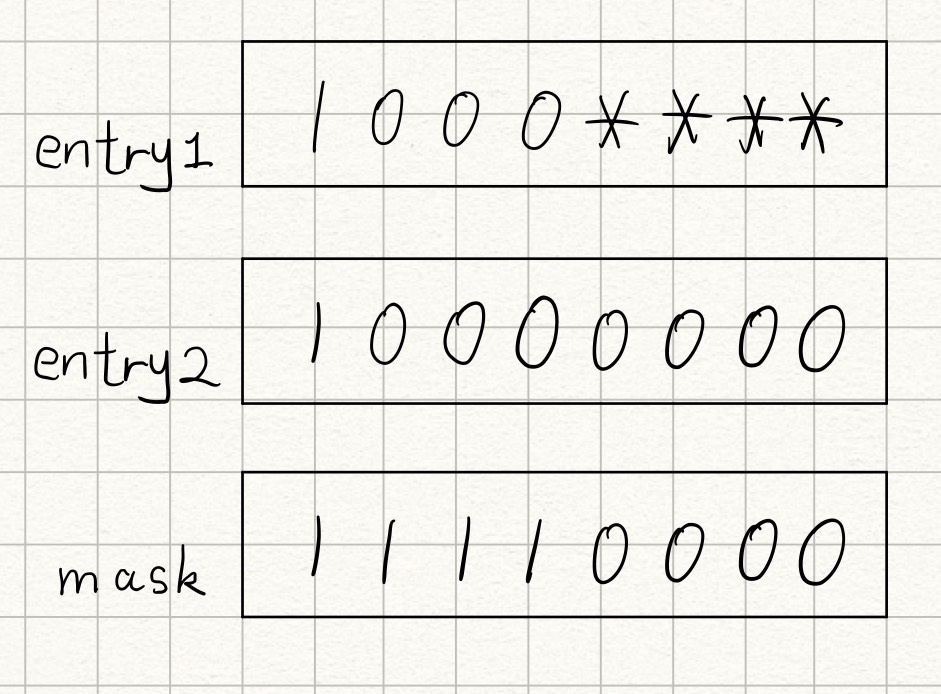

第二步,令entry2 = entry & mask

所以entry2 = 10000000

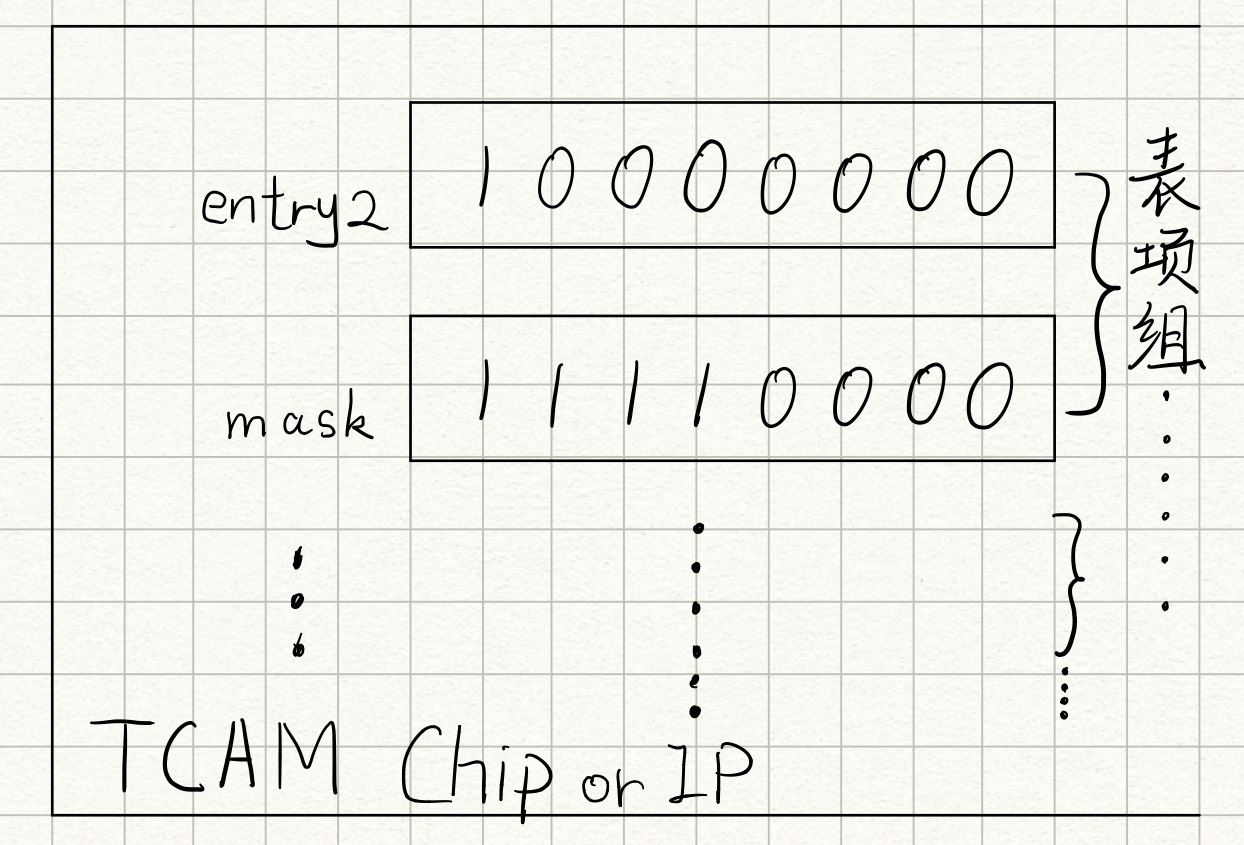

将entry2 和mask 下载存入TCAM表项组中:

在做查找的时候,key广播到每个表项组中。之后将key和当前表项组中的mask做与运算,如key = 10001010. key& mask = 10001010 & 11110000 = 10000000

最后再和entry做比较,如果相等则将1写入结果寄存器。之后所有的结果汇总到优先级选路器中。并得到id编号。

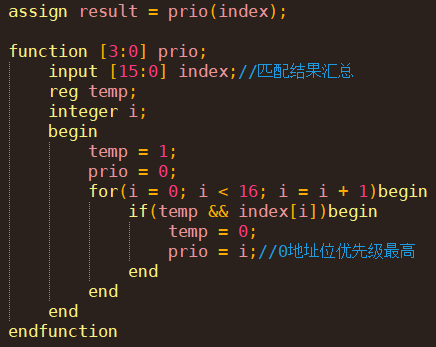

优先级选路器:

可以用function函数实现:

参考代码请看这里一个粗糙的实现:https://github.com/qiaosiyi/progASICp4SWITCH/blob/master/tcam.v

这样我们基本上就可以用Verilog语言去实现了,其次要注意的是,广播,复制,或者做逻辑运算,都会比较占用时延,不要在一个时钟周期去做,很可能无法完成时序约束。

建议一个操作使用一个时钟周期,所以tcam查找我这里延迟了四个周期,但是fully-pipeline。吞吐还是一周期一次。

有时候表项很多,也许优先级选路器timing收不了,其实可以考虑将这一步延长俩周期做。其实本质相当于降低了tcam处理频率。

关于CAM:

CAM与TCAM类似,CAM是精确匹配,key广播到每个entry,然后比较出结果汇总到优先选路器中,得到id。比tcam操作步骤减少了一些,而且逻辑资源也减少了很多。

可以在这里看一下我粗糙的代码:https://github.com/qiaosiyi/progASICp4SWITCH/blob/master/cam.v

========================

qsy

15MAR2019

TCAM CAM 说明 原理 结构 Verilog 硬件实现的更多相关文章

- 【接口时序】4、SPI总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 【接口时序】3、UART串口收发的原理与Verilog实现

一.软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45- ...

- SPI总线的原理与Verilog实现

转载地址:https://www.cnblogs.com/liujinggang/p/9609739.html 一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件 ...

- 【接口时序】6、IIC总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE .ChipScope 硬件平台: 1. FPG ...

- 【接口时序】7、VGA接口原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 定点CORDIC算法求所有三角函数及向量模的原理分析、硬件实现(FPGA)

一.CORDIC算法 CORDIC(Coordinate Rotation DIgital Computer)是一种通过迭代对多种数学函数求值的方法,它可以对三角函数.双曲函数和平面旋转问题进行求解. ...

- 格雷码原理与Verilog实现

格雷码原理 格雷码是一个叫弗兰克*格雷的人在1953年发明的,最初用于通信.格雷码是一种循环二进制码或者叫作反射二进制码.格雷码的特点是从一个数变为相邻的一个数时,只有一个数据位发生跳变,由于这种特点 ...

- 我的 FPGA 学习历程(04)—— 练习 verilog 硬件描述语言

这篇讲的是使用 verilog 硬件描述语言编写一个 3 - 8 译码器. 3 - 8 译码器是一个简单的组合逻辑,用于实现并转串,其输入输出关系如下: | 输入 | 输出 | -------- ...

- FIR滤波原理及verilog设计

FIR(Finite Impulse Response)Filter:有限冲激响应滤波器,又称为非递归线性滤波器. FIR滤波器的冲击响应是一个值为滤波器抽头系数的采样序列,其脉冲响应由有限个采样值构 ...

随机推荐

- 雷林鹏分享:Ruby Socket 编程

Ruby Socket 编程 Ruby提供了两个级别访问网络的服务,在底层你可以访问操作系统,它可以让你实现客户端和服务器为面向连接和无连接协议的基本套接字支持. Ruby 统一支持应用程的网络协议, ...

- 理解 Git 的基本概念 ( Merging Collaborating Rebasing)

合并 Merging 在分支上开发新功能后,如何把新功能加入到主分支,让其它人得到你的修改呢?你需要使用命令 git merge 或 git pull. 这两个命令的语法如下: git merge [ ...

- Java——抽象类、接口

body, table{font-family: 微软雅黑; font-size: 10pt} table{border-collapse: collapse; border: solid gray; ...

- 面筋: 奇虎360 c++ 后台开发 实习生 面试

投的是360上海的商业化部门,岗位是C++服务端开发实习生,记录一下面试历程: 视频面试,但是是有代码框让你写代码的. 一面: Q:先说一下个人信息,做过的项目 A:.......... Q:先写个翻 ...

- Artix-7 50T FPGA试用笔记之Create a simple MicroBlaze System

前言:之前笔者的试用博文提到安富利这块板子非常适合MicroBlaze开发,同时网上关于MicroBlaze的资料非常少(或含糊不清),没有一篇能完整介绍VIVADO SDK的设计流程,所以笔者带来这 ...

- java- Collection Set集合

首先HashSet类创建集合对象和遍历对象 package set; import java.util.HashSet; import java.util.Iterator; //hashset储存字 ...

- Beta阶段第2周/共2周 Scrum立会报告+燃尽图 14

作业要求[https://edu.cnblogs.com/campus/nenu/2018fall/homework/2411] 版本控制:https://git.coding.net/liuyy08 ...

- 通过iframe 实现upload file无刷新

<html> <head> </head> <body> <form encType="multipart/form-data&q ...

- scikit-learn 学习笔记-- Generalized Linear Models (三)

Bayesian regression 前面介绍的线性模型都是从最小二乘,均方误差的角度去建立的,从最简单的最小二乘到带正则项的 lasso,ridge 等.而 Bayesian regression ...

- 学习ThinkPHP第一天

今天开始学习PHP框架了,刚开始学,感觉挺兴奋的,离自己建立自己的博客又仅了一步,在linux环境下配置一定要赋予新创建的文件夹权限: sudo chmod -R 0777 filePath 这样 ...