基于INTEL FPGA硬浮点DSP实现卷积运算

概述

卷积是一种线性运算,其本质是滑动平均思想,广泛应用于图像滤波。而随着人工智能及深度学习的发展,卷积也在神经网络中发挥重要的作用,如卷积神经网络。本参考设计主要介绍如何基于INTEL 硬浮点的DSP Block实现32位单精度浮点的卷积运算,而针对定点及低精度的浮点运算,则需要对硬浮点DSP Block进行相应的替换即可。

原理分析

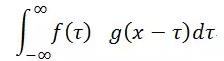

设:f(x), g(x)是两个可积函数,作积分:

随着x的不同取值,该积分定义了一个新的函数h(x),称为函数f(x)与g(x)的卷积,记为h(x)=f(x)*g(x)。

如果卷积的变量是序列x(n)和h(n),则卷积的结果为

其中*表示卷积。因此两个序列的卷积,实际上就是多项式的乘法,用个例子说明其工作原理。a = [7,5,4]; b = [6,7,9];则实现a和b的卷积,就是把a和b作为一个多项式的系数,按多项式的升幂或降幂排列,即为:

因此得到a*b=[42,79,122,73,36];与Matlab运算结果一致。而二维卷积可以采用通用多项式乘积方法实现卷积运算。

基于INTEL FPGA的实现分析

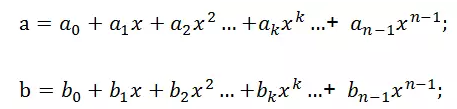

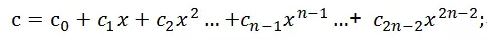

如上我们确定了两个序列的卷积等同于两个多项式的乘法,因此当我们需要计算序列[a0,a1,a2, …,an-1]与[b0,b1,b2, …,bn-1]的卷积结果时,可以成立a,b两个n阶多项式,如下所示:

则[a0,a1,a2, …,an-1]与[b0,b1,b2, …,bn-1]的卷积结果即为由a*b得到的多项式的各项系数所组成的序列。令c=a*b,得到

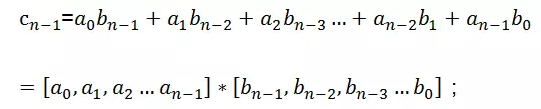

则由多项式c的各阶系数所组成的新的序列[c0,c1,c2, …,c2n-1]即为[a0,a1,a2, …,an-1]与[b0,b1,b2, …,bn-1]的卷积结果。则按照高阶多项式计算展开可得到:

┆┆

┆┆

因此卷积的运算可以转化为行向量与列向量相乘的结果,即乘累加的运算结构。

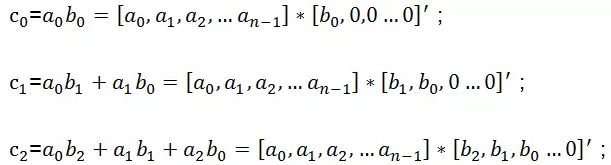

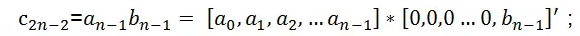

Intel FPGA在Arria10DSP Block中首次支持了单精度硬浮点DSP block,是行业内第一个支持单精度DSP block,硬浮点DSP block架构如图1所示:

图1 硬浮点DSPblock架构

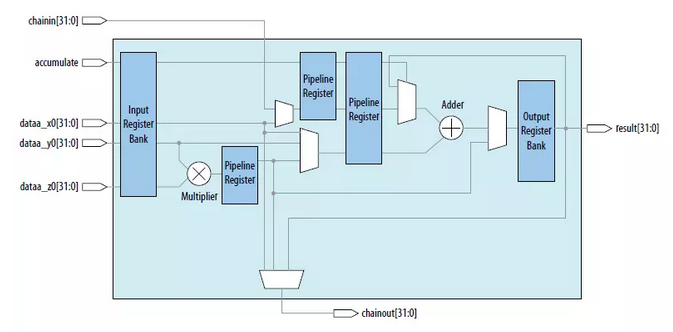

硬浮点DSP Block包含硬浮点乘法器,硬浮点加法器,支持乘累加运算,因此采用硬浮点DSPblock实现行列向量相乘是非常好的方式。下面我们针对一个实际的卷积运算,介绍如何基于INTEL硬浮点DSP block实现。假设我们需要求随机数组a=[4,8,9,11]与b=[10,5,7,13]的卷积运算结果,则根据上面的分析,保持数组a顺序不变,而数组b需根据上述分析结果,针对每一个卷积结果产生新的序列。所以整个实现包括数列重组模块和硬浮点乘法器模块及输出处理。下面是实现框图及仿真结果。

图2 实现框图

图3 Modelsim仿真结果

仿真结果与Matlab实现结果一致,并且该设计中充分考虑了FPGA并行扩展特性,对于低速率要求的设计可采用DSP Block复用的方式节约DSP block数量。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

基于INTEL FPGA硬浮点DSP实现卷积运算的更多相关文章

- 关于INTEL FPGA设计工具DSP Builder

一段时间以来,MathWorks一直主张使用Matlab和Simulink开发工具进行基于模型的设计,因为好的设计技术使您能够在更短的时间内开发更高质量的复杂软件.基于模块的设计采用了数学和可视化的方 ...

- OpenCL设计优化(基于Intel FPGA SDK for OpenCL)

1.首先了解Intel FPGA SDK for OpenCL实现OpenCL的设计组件,包括: kernels, global memory interconnect, local memory, ...

- Intel FPGA Clock Region概念以及用法

目录 Intel FPGA 的Clock Region概念 Intel 不同系列FPGA 的Clock Region 1. Clock Region Assignments in Intel Stra ...

- TI科学家谈浮点DSP未来发展

自十多年前浮点数字信号处理器(DSP)诞生以来,便为实时信号处理提供了算术上更为先进的备选方案.不过,定点器件至今仍是业界的主流.当然低成本是主要原因.定点DSP每器件产品的价格很低,这对大规 ...

- 基于Intel x86 Android的RAD游戏开发

zip文件还包含编译的"MonkeyGame-debug".可以在模拟器中运行的二进制文件.在"game.build"文件夹中有一个HTML5 build.在C ...

- 基于Xilinx FPGA的视频图像采集系统

本篇要分享的是基于Xilinx FPGA的视频图像采集系统,使用摄像头采集图像数据,并没有用到SDRAM/DDR.这个工程使用的是OV7670 30w像素摄像头,用双口RAM做存储,显示窗口为320x ...

- ARMCC和GCC编译ARM代码的软浮点和硬浮点问题 【转】

转自:http://houh-1984.blog.163.com/blog/static/31127834201211112129167/ 本文介绍了ARM代码编译时的软浮点(soft-float)和 ...

- ARMCC和GCC编译ARM代码的软浮点和硬浮点问题【转】

转自:https://blog.csdn.net/hunanchenxingyu/article/details/47003279 本文介绍了ARM代码编译时的软浮点(soft-float)和硬浮点( ...

- 基于FPGA的光口通信开发案例|基于Kintex-7 FPGA SFP+光口的10G UDP网络通信开发案例

前言 自著名华人物理学家高锟先生提出"光传输理论",实用化的光纤传输产品始于1976年,经历了PDH→SDH→DWDM→ASON→MSTP的发展历程.本世纪初期,ASON/OADM ...

随机推荐

- Sql sever 事务

SQL事务 一.事务概念 事务是一种机制.是一种操作序列,它包含了一组数据库操作命令,这组命令要么全部执行,要么全部不执行.因此事务是一个不可分割的工作逻辑单元.在数据库系统上执行并发操作时事务 ...

- C++设计模式之-建造者模式

建造者模式的定义将一个复杂对象的构建与它的表示分离,使得同样的构建过程可以创建不同的表示(DP).<大话设计模式>举了一个很好的例子——建造小人,一共需建造6个部分,头部.身体.左右手.左 ...

- mysql的sql编程

sql编程 变量 变量分为两种:系统变量和自定义变量 系统变量 系统定义好的变量:大部分的时候用户根本不需要使用系统变量,系统变量时用来控制服务器的表现的,如:auto_commit. 查看系统变量 ...

- APUE学习笔记——10.11~10.13 信号集、信号屏蔽字、未决信号

如有转载,请注明出处:Windeal专栏 首先简述下几个概念的关系: 我们通过信号集建立信号屏蔽字,使得信号发生阻塞,被阻塞的信号即未决信号. 信号集: 信号集:其实就是一系列的信号.用sigset_ ...

- Python报错IOError: [Errno 22] invalid mode ('r') or filename

IOError: [Errno 22] invalid mode ('r') or filename: 这种错误的出现是在使用built-in函数file()或者open()的时候. 或者是因为文件的 ...

- height 与 min-height 的继承

min-height: inherit; 继承父元素的 min-height: 80px; 但,不能继承父元素的 height: 200px; height: inherit; 能继承父元素的: he ...

- 【集成学习】lightgbm调参案例

lightgbm使用leaf_wise tree生长策略,leaf_wise_tree的优点是收敛速度快,缺点是容易过拟合. # lightgbm关键参数 # lightgbm调参方法cv 代码git ...

- LOJ2500 NOIP2014 飞扬的小鸟 【背包DP】*

LOJ2500 NOIP2014 飞扬的小鸟 LINK 题目大意就是说有n个柱子,在每一秒你可以选择不点下降高度y和点p次上升x∗p,若果当前位置加上x∗p大于上界m,就会停在m. 如果可以成功穿越所 ...

- BZOJ2753 SCOI2012 滑雪与时间胶囊 【最小生成树】*

BZOJ2753 SCOI2012 滑雪与时间胶囊 Description a180285非常喜欢滑雪.他来到一座雪山,这里分布着M条供滑行的轨道和N个轨道之间的交点(同时也是景点),而且每个景点都有 ...

- 关于ehcache缓存的使用(简单对比redis)

前言 最近在做一个项目,某个接口查询数据到返回数据总计需要7000+毫秒,一直在考虑优化的问题,优化也有原来的一家一家查询到一次查询所有的,在查询不同天数.结果是1500+,虽然优化了不少,但是数据结 ...