FIR基本型仿真_03

作者:桂。

时间:2018-02-05 20:50:54

链接:http://www.cnblogs.com/xingshansi/p/8419452.html

一、仿真思路

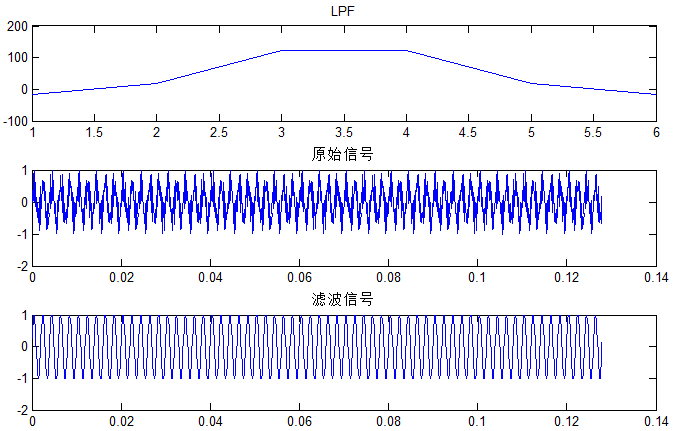

设计低通滤波器(5阶,6个系数),滤波器特性:

借助低通滤波器对信号进行滤波:

二、VIVADO仿真

首先利用MATLAB生成定点补码:

%=============设置系统参数==============%

f1=500; %设置波形频率

f2=3600;

Fs=8000; %设置采样频率

L=1024; %数据长度

N=16; %数据位宽

%=============产生输入信号==============%

t=0:1/Fs:(1/Fs)*(L-1);

y=sin(2*pi*f1*t)+sin(2*pi*t*f2);

y_n=round(y*(2^(N-3)-1)); %N比特量化;如果有n个信号相加,则设置(N-n)

%=================画图==================%

a=10; %改变系数可以调整显示周期

stem(t,y_n);

axis([0 L/Fs/a -2^N 2^N]); %显示

%=============写入外部文件==============%

fid=fopen('sin_data.txt','w'); %把数据写入sin_data.txt文件中,如果没有就创建该文件

for k=1:length(y_n)

B_s=dec2bin(y_n(k)+((y_n(k))<0)*2^N,N);

for j=1:N

if B_s(j)=='1'

tb=1;

else

tb=0;

end

fprintf(fid,'%d',tb);

end

fprintf(fid,'\r\n');

end fprintf(fid,';');

fclose(fid);

vivado的testbench:

`timescale 1ns / 1ps

module tb;

// Inputs

logic Clk;

logic rst;

// Outputs

logic signed [23:0] Yout;

//Generate a clock with 10 ns clock period.

initial Clk <= 0; always #5 Clk = ~Clk; //Initialize and apply the inputs.

//-------------------------------------//

parameter data_num = 32'd1024;

integer i = 0;

reg [15:0] Xin[1:data_num];

reg [15:0] data_out; initial begin

rst = 1;

#20

rst = 0;

#40

$readmemb("D:/PRJ/vivado/simulation_ding/009_lpf6tap/matlab/sin_data.txt",Xin);

end always @(posedge Clk) begin

if(rst)

begin

data_out <= 0;

end

else

begin

data_out <= Xin[i];

i <= i + 8'd1;

end

end fir_6tap uut (

.Clk(Clk),

.Xin(data_out),

.Yout(Yout)

);

endmodule

子模块 fir_6tap:

`timescale 1ns / 1ps

module fir_6tap(

input Clk,

input signed [15:0] Xin,

output reg signed [23:0] Yout

); //Internal variables.

wire signed [7:0] H0,H1,H2,H3,H4,H5;

wire signed [23:0] MCM0,MCM1,MCM2,MCM3,MCM4,MCM5,add_out1,add_out2,add_out3,add_out4,add_out5;

wire signed [23:0] Q1,Q2,Q3,Q4,Q5; //filter coefficient initializations.

//H = [-2 -1 3 4].

assign H0 = -15;

assign H1 = 19 ;

assign H2 = 123;

assign H3 = 123;

assign H4 = 19;

assign H5 = -15; //Multiple constant multiplications.

assign MCM5 = H5*Xin;

assign MCM4 = H4*Xin;

assign MCM3 = H3*Xin;

assign MCM2 = H2*Xin;

assign MCM1 = H1*Xin;

assign MCM0 = H0*Xin; //adders

assign add_out1 = Q1 + MCM4;

assign add_out2 = Q2 + MCM3;

assign add_out3 = Q3 + MCM2;

assign add_out4 = Q4 + MCM1;

assign add_out5 = Q5 + MCM0;

//flipflop instantiations (for introducing a delay).

DFF dff1 (.Clk(Clk),.D(MCM5),.Q(Q1));

DFF dff2 (.Clk(Clk),.D(add_out1),.Q(Q2));

DFF dff3 (.Clk(Clk),.D(add_out2),.Q(Q3));

DFF dff4 (.Clk(Clk),.D(add_out3),.Q(Q4));

DFF dff5 (.Clk(Clk),.D(add_out4),.Q(Q5));

//Assign the last adder output to final output.

always@ (posedge Clk)

Yout <= add_out5; endmodule

DFF:

`timescale 1ns / 1ps

module DFF

(input Clk,

input [23:0] D,

output reg [23:0] Q

); always@ (posedge Clk)

Q = D; endmodule

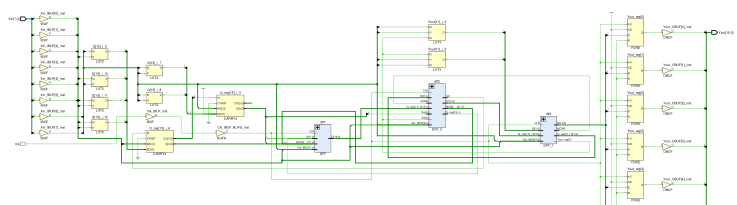

主要电路图(4阶为例):

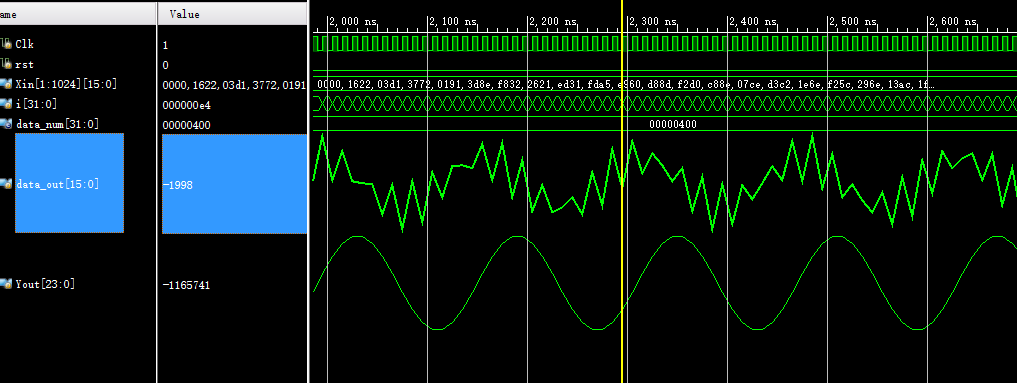

仿真结果,与MATLAB测试一致:

FIR基本型仿真_03的更多相关文章

- FIR特性及仿真实现_01

作者:桂. 时间:2018-02-05 19:01:21 链接:http://www.cnblogs.com/xingshansi/p/8419007.html 前言 本文主要记录FIR(finit ...

- Xilinx 常用模块汇总(verilog)【01】

作者:桂. 时间:2018-05-07 19:11:23 链接:http://www.cnblogs.com/xingshansi/p/9004492.html 前言 该文私用,不定期更新,主要汇总 ...

- 关于FIR的modelsim

(1)FIR ip核仿真 (2)FIR 多通道应用 (3)多通道fir ip核需要注意的复位问题 =================================================== ...

- FIR仿真module_04

作者:桂. 时间:2018-02-06 12:10:14 链接:http://www.cnblogs.com/xingshansi/p/8421001.html 前言 本文主要记录基本的FIR实现, ...

- modelsim 仿真xilinx fir ip

到现在不管fir ip 用的对不对,但是在使用modelsim是可以仿真fir ip的. 具体步骤: 1.仿真库,添加到modelsim目录配置文件: 2.将这个文件中的: :List of dyna ...

- 基于FPGA的音频信号的FIR滤波(Matlab+Modelsim验证)

1 设计内容 本设计是基于FPGA的音频信号FIR低通滤波,根据要求,采用Matlab对WAV音频文件进行读取和添加噪声信号.FFT分析.FIR滤波处理,并分析滤波的效果.通过Matlab的分析验证滤 ...

- DVB-C系统中QAM调制与解调仿真

本文简单记录一下自己学习<通信原理>的时候调试的一个仿真DVB-C(Cable,数字有线电视)系统中QAM调制和解调的程序.自己一直是研究"信源"方面的东西,所以对&q ...

- 声反馈抑制使用matlab/simulink仿真

第一份工作时做啸叫抑制的仿真,调大0.3可以有大的啸叫产生,下图的SIMULINK仿真模型 实现移相有多种方法: 1.iir实现 2.FFT实现 3.使用FIR实现 所有信号均可以由正弦信号叠加而成.

- FIR调用DSP48E_05

作者:桂. 时间:2018-02-06 17:52:38 链接:http://www.cnblogs.com/xingshansi/p/8423457.html 前言 到目前为止,本文没有对滤波器实 ...

随机推荐

- SHELL字符串使用总结

1.获取字符串的长度,${#str} #设置字符串 $ str="liqiu" #打印字符串 $ echo $str liqiu #继续打印字符串 $ echo ${str} li ...

- JAVA设计模式(全部)

一篇一篇的重写意义不大,不如把整个PDF文档上传上来看着方便,下载链接

- tshark使用说明

tshark -h TShark (Wireshark) (v2.-gf42a0d2b6c) Dump and analyze network traffic. See https://www.wir ...

- Spring Boot 之 RESTfull API简单项目的快速搭建(二)

1.打包 -- Maven build 2.问题 [WARNING] The requested profile "pom.xml" could not be activated ...

- logback的简单配置

logback的简单配置: <?xml version="1.0" encoding="UTF-8"?> <configuration> ...

- 【shell】创建长目录,目录存在则忽略,缺失则创建

有时候,我们需要创建一个空目录树,如果给定路径包含目录,那么还必须检查这些目录是否存在: mkdir –p /qinys/oliver/tmp/ 执行上述命令即可创建长目录,并且有则忽略,无则创建原则 ...

- Axure 地区选择(选择省份之后可以选择对应的地级市)

百度网盘:http://pan.baidu.com/s/1c1ZjUPq

- python之模块配置文件ConfigParser(在python3中变化较大)

# -*- coding: utf-8 -*- #python 27 #xiaodeng #python之模块ConfigParser(在python3中为configparser) #特别注意:py ...

- 跟我学Shiro---无状态 Web 应用集成

无状态 Web 应用集成 在一些环境中,可能需要把 Web 应用做成无状态的,即服务器端无状态,就是说服务器端不会存储像会话这种东西,而是每次请求时带上相应的用户名进行登录.如一些 REST 风格的 ...

- 抗衡Win Linux全凭这些桌面环境

2012年01月25日 元老级桌面环境KDE Linux操作系统最早使用在服务器上,而桌面操作系统并不是Linux的重点突围.但是,近几年Linux桌面操作系统有崛起的趋势,抢夺了部分桌面操作 ...