quartus ii FFT核使用

quartus ii FFT核使用

导入自己程序自带的txt文件,写出控制模块

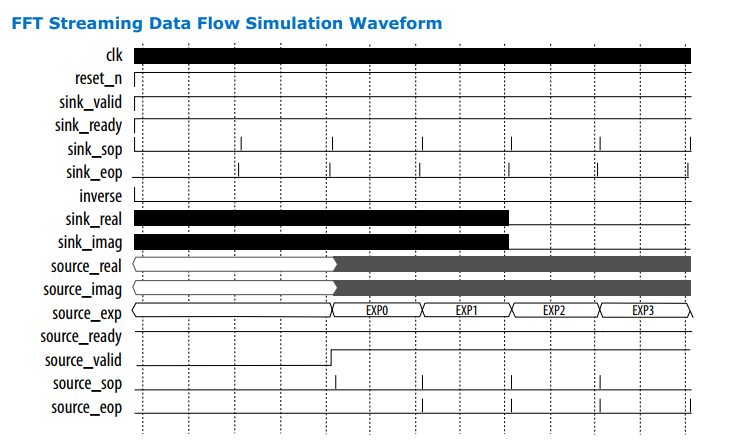

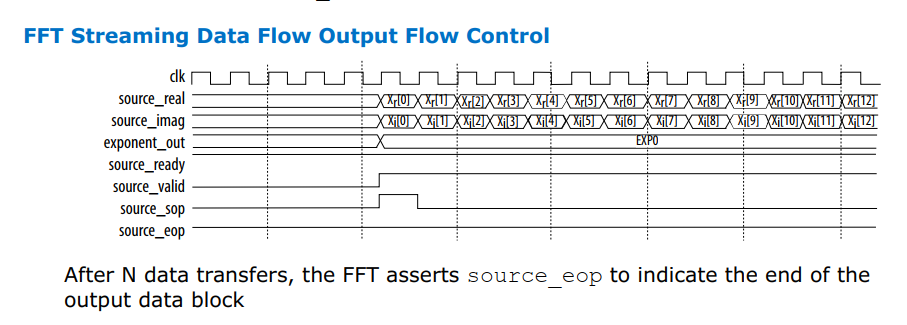

时序图

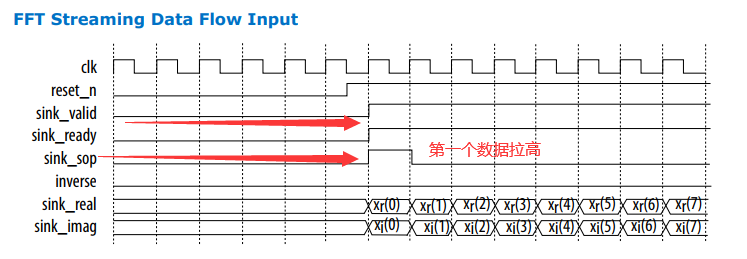

FFT核文件给出的时序图输入

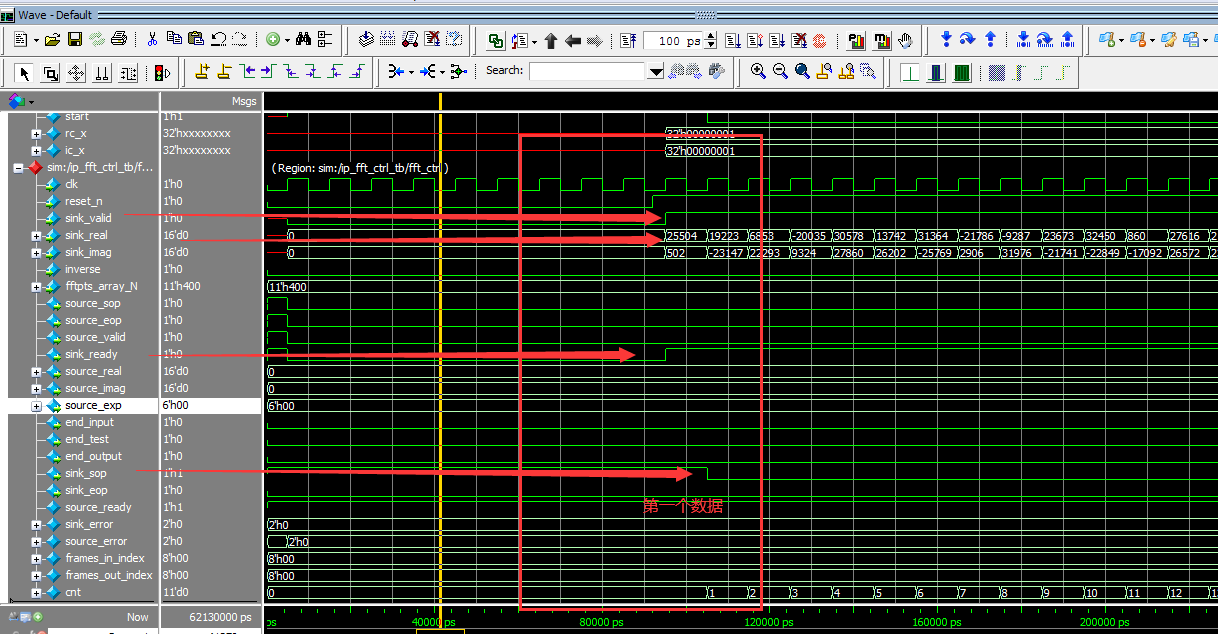

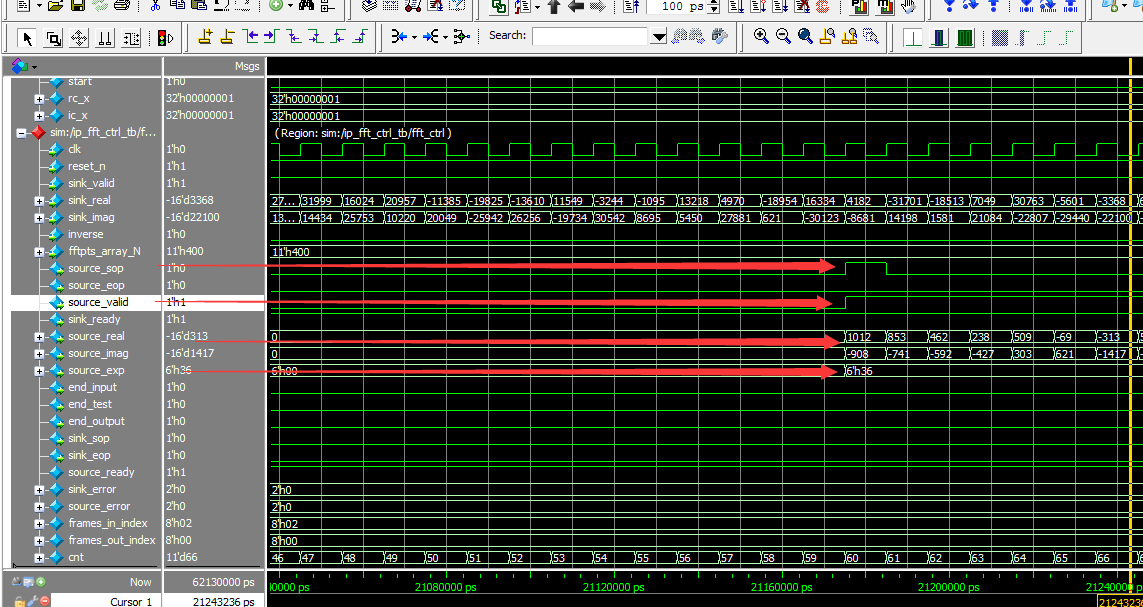

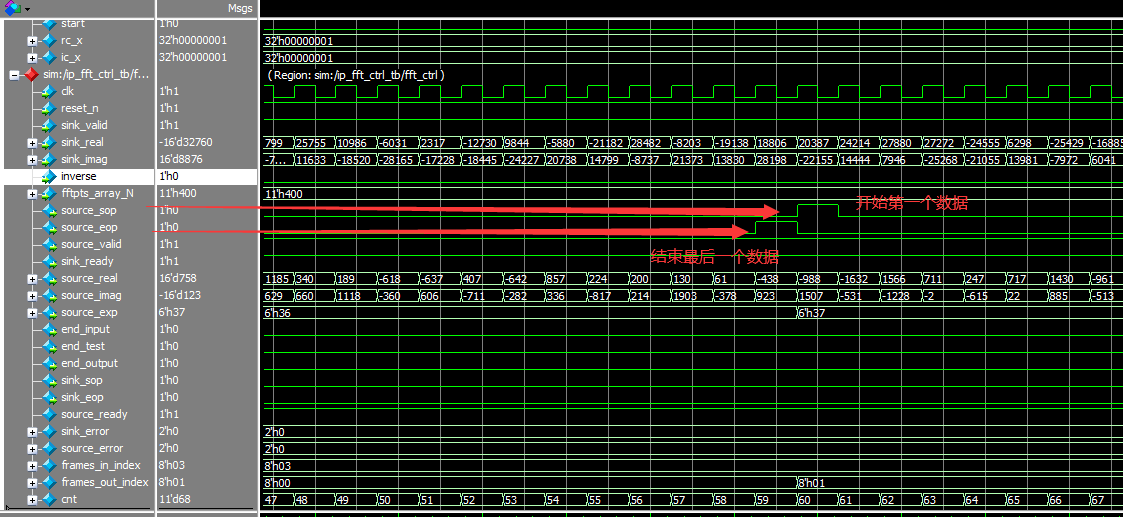

仿真时序图

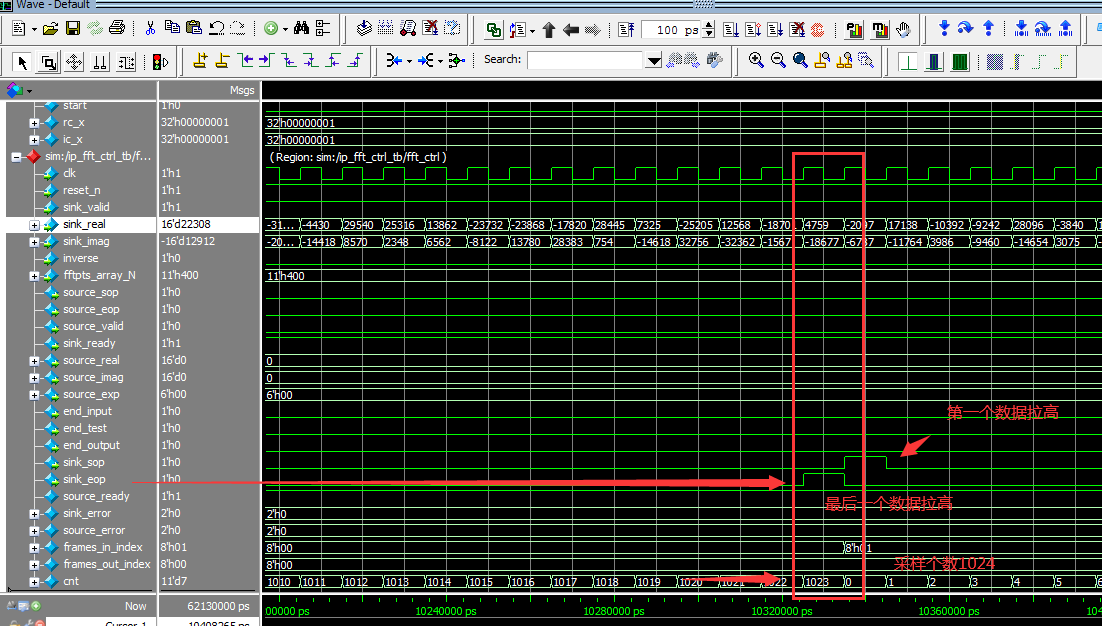

1024个采样点数,输入结束

fft数据输出

2、代码

`timescale 1ns/1ns

module fft_ctrl

#(

parameter [:] fftpts_n = 'd11,

parameter [:] real_imag_wei = 'd16

)

(

//inputs

clk ,

reset_n ,

sink_valid ,//拉高表示通知FFT即将有N个数据输入

sink_real ,//输入数据的实部

sink_imag ,//输入数据的虚部

inverse ,//0 - FFT 1 - IFFT

fftpts_array_N , //采样的点数 //output

source_sop , //输出数据起始标记

source_eop , //输出数据结束标记

source_valid , //置高,准备输出结果

//从时序看应该是sink_ready和sink_valid同步的

sink_ready ,//FFT模块准备就绪,可以接收数据 output

sink_sop ,//输入数据起始标记脉冲(维持一个时钟的高电平),与第一个数据同步

sink_eop ,//输入数据结束标记脉冲(维持一个时钟的高电平),与最后一个数据同步

source_real ,//变换后输出数据的实部

source_imag ,//变换后输出数据的虚部

source_exp , //结果数据缩放因子:这

end_input , //数据输入结束

end_test , //数据输入结束 置1

end_output //数据输出结束 ); //******************************* input and output *********************// //inputs

input clk ;

input reset_n ;

input sink_valid ;//拉高表示通知FFT即将有N个数据输入

input [real_imag_wei - :] sink_real ;//输入数据的实部

input [real_imag_wei - :] sink_imag ;//输入数据的虚部

input inverse ;//0 - FFT 1 - IFFT

input [fftpts_n - :] fftpts_array_N; //采样的点数 //output

output source_sop ; //输出数据起始标记

output source_eop ; //输出数据结束标记

output source_valid ; //置高,准备输出结果

//从时序看应该是sink_ready和sink_valid同步的

output sink_ready ;//FFT模块准备就绪,可以接收数据 output

output [real_imag_wei - : ] source_real ;//变换后输出数据的实部

output [real_imag_wei - : ] source_imag ;//变换后输出数据的虚部

output [:] source_exp ; //结果数据缩放因子:这

output end_input; //数据输入结束

output reg end_test; //输入的数据结束 置1

output end_output; //数据输出结束

output sink_sop;//输入数据起始标记脉冲(维持一个时钟的高电平),与第一个数据同步

output sink_eop;//输入数据结束标记脉冲(维持一个时钟的高电平),与最后一个数据同步 //***************************** parameter and interface *************************// wire source_ready;//表明downstream模块(理解为FFT的后续接收数据模块)可以接收数据 input

wire [:] sink_error;

wire [:] source_error; localparam NUM_FRAMES_c = ; //输入数据的次数

//parameter MAXVAL_c = 2**(16 -1);

//parameter OFFSET_c = 2**(16);

//parameter MAXVAL_EXP_c = 2**5;

//parameter OFFSET_EXP_c = 2**6; //reg start;

//number of input frames

reg [:] frames_in_index;

//number of output frames

reg [:] frames_out_index;

// signal the end of the input data stream and output data stream.

reg [fftpts_n - :] cnt; ///////////////////////////////////////////////////////////////////////////////////////////////

// Clock Generation

///////////////////////////////////////////////////////////////////////////////////////////////

///////////////////////////////////////////////////////////////////////////////////////////////

// Set FFT Direction

// '0' => FFT

// '1' => IFFT

// assign inverse = 1'b0; //no input error

assign sink_error = 'b0; // for example purposes, the ready signal is always asserted.

assign source_ready = 'b1; ///////////////////////////////////////////////////////////////////////////////////////////////

// All FFT MegaCore input signals are registered on the rising edge of the input clock, clk and

// all FFT MegaCore output signals are output on the rising edge of the input clock, clk.

////////////////////////////////////////////////////////////////////////////////////////////// // start valid for first cycle to indicate that the file reading should start.

/*

always @ (posedge clk or negedge reset_n)

begin

if (reset_n == 1'b0)

start <= 1'b1;

else

begin

if (sink_valid == 1'b1 & sink_ready == 1'b1)

start <= 1'b0;

end

end

*/

//sop and eop asserted in first and last sample of data

always @ (posedge clk or negedge reset_n)

begin

if (reset_n == 'b0)

cnt <= 'd0;

else

begin

if (sink_valid == 'b1 & sink_ready == 1'b1)

begin

if (cnt == fftpts_array_N - )

cnt <= 'd0;

else

cnt <= cnt + 'b1;

end

end

end // count the input frames and increment the index

always @(posedge clk or negedge reset_n)

begin

if (reset_n == 'b0)

frames_in_index <= 'd0;

else

begin

if (sink_eop == 'b1 & sink_valid == 1'b1 & sink_ready == 'b1 & frames_in_index < NUM_FRAMES_c -1)

frames_in_index <= frames_in_index + 'b1;

end

end // count the output frames and increment the index

always @(posedge clk or negedge reset_n)

begin

if (reset_n == 'b0)

frames_out_index <= 'd0;

else

begin

if (source_eop == 'b1 & source_valid == 1'b1 & source_ready == 'b1 & frames_out_index < NUM_FRAMES_c -1)

frames_out_index <= frames_out_index + 'b1;

end

end // signal when all of the input data has been sent to the DUT

assign end_input = (sink_eop == 'b1 & sink_valid == 1'b1 & sink_ready == 'b1 & frames_in_index == NUM_FRAMES_c - 1) ? 1'b1 : 'b0; // signal when all of the output data has be received from the DUT

assign end_output = (source_eop == 'b1 & source_valid == 1'b1 & source_ready == 'b1 & frames_out_index == NUM_FRAMES_c - 1) ? 1'b1 : 'b0; // generate start and end of packet signals

assign sink_sop = (cnt == ) ? 'b1 : 1'b0 ;

assign sink_eop = ( cnt == fftpts_array_N - ) ? 'b1 : 1'b0; //halt the input when done

always @(posedge clk or negedge reset_n)

begin

if (reset_n == 'b0)

end_test <= 'b0;

else

begin

if (end_input == 'b1)

end_test <= 'b1;

end

end ip_fft dut(

.clk (clk), //

.reset_n (reset_n), //

.inverse (inverse), //0 - FFT 1 - IFFT

.sink_real (sink_real), //输入数据的实部

.sink_imag (sink_imag), //输入数据的虚部

.sink_sop (sink_sop), //输入数据起始标记脉冲(维持一个时钟的高电平),与第一个数据同步

.sink_eop (sink_eop), //输入数据结束标记脉冲(维持一个时钟的高电平),与最后一个数据同步

.sink_valid (sink_valid), //拉高表示通知FFT即将有N个数据输入

.sink_error (sink_error), //指示数据流的错误信息:00——没有错误;01——丢失SOP;10——丢失EOP;11——多余的EOP;

.source_error (source_error), //表明upstream模块或者FFT模块出了问题,错误信息提示与sink_error一样 output

.source_ready (source_ready), //表明downstream模块(理解为FFT的后续接收数据模块)可以接收数据 input

.sink_ready (sink_ready), //FFT模块准备就绪,可以接收数据 output

.source_real (source_real), //变换后输出数据的实部

.source_imag (source_imag), //变换后输出数据的虚部

.source_exp (source_exp), //结果数据缩放因子:这个指数位的意思打个比方说吧,

//比如它是3,就是说这时输出的虚部和实部的数值要除以2的3次方,如果是10,就要除以2的10次方,

//如果对结果精度要求不高的话,可以直接截去相应的长度,

//比如指数是3,实部输出1011_0111_0111,那么此刻实际的值应该为1_0110_1110.111;取整就是101101110

.source_valid (source_valid), //置高,准备输出结果

.source_sop (source_sop), //输出数据起始标记

.source_eop (source_eop) //输出数据结束标记

); endmodule

// ================================================================================

// Legal Notice: Copyright (C) 1991-2008 Altera Corporation

// Any megafunction design, and related net list (encrypted or decrypted),

// support information, device programming or simulation file, and any other

// associated documentation or information provided by Altera or a partner

// under Altera's Megafunction Partnership Program may be used only to

// program PLD devices (but not masked PLD devices) from Altera. Any other

// use of such megafunction design, net list, support information, device

// programming or simulation file, or any other related documentation or

// information is prohibited for any other purpose, including, but not

// limited to modification, reverse engineering, de-compiling, or use with

// any other silicon devices, unless such use is explicitly licensed under

// a separate agreement with Altera or a megafunction partner. Title to

// the intellectual property, including patents, copyrights, trademarks,

// trade secrets, or maskworks, embodied in any such megafunction design,

// net list, support information, device programming or simulation file, or

// any other related documentation or information provided by Altera or a

// megafunction partner, remains with Altera, the megafunction partner, or

// their respective licensors. No other licenses, including any licenses

// needed under any third party's intellectual property, are provided herein.

// ================================================================================

// `timescale 1ns / 1ps

module ip_fft_ctrl_tb; //inputs

reg clk;

reg reset_n;

reg sink_valid;

reg[ - :] sink_real;

reg[ - :] sink_imag;

reg [:] fftpts_array_N;

reg inverse;

wire sink_sop;

wire sink_eop;

wire sink_ready; wire source_sop;

wire source_eop;

wire source_valid;

wire [:] source_exp;

wire [ - : ] source_real;

wire [ - : ] source_imag;

parameter NUM_FRAMES_c = ;

parameter MAXVAL_c = **( -);

parameter OFFSET_c = **();

parameter MAXVAL_EXP_c = **;

parameter OFFSET_EXP_c = **; // signal the end of the input data stream and output data stream.

wire end_test;

wire end_input;

wire end_output; integer fft_rf, fft_if;

integer expf;

integer data_rf,data_if;

integer data_real_in_int,data_imag_in_int;

integer fft_real_out_int,fft_imag_out_int;

integer exponent_out_int; initial

begin data_rf = $fopen("ip_fft_real_input.txt","r");

data_if = $fopen("ip_fft_imag_input.txt","r");

fft_rf = $fopen("ip_fft_real_output_ver.txt");

fft_if =$fopen("ip_fft_imag_output_ver.txt");

expf = $fopen("ip_fft_exponent_output_ver.txt");

# clk = 'b0;

inverse = ;

fftpts_array_N = 'd1024;

sink_valid = ;

inverse = ;

# reset_n = 'b0;

# reset_n = 'b1; end ///////////////////////////////////////////////////////////////////////////////////////////////

// Clock Generation

///////////////////////////////////////////////////////////////////////////////////////////////

always

begin

if (end_test == 'b1 & end_output == 1'b1)

begin

clk = 'b0;

$finish;

end

else

begin

# clk = 'b1;

# clk = 'b0;

end

end ///////////////////////////////////////////////////////////////////////////////////////////////

//采样的点数

//assign fftpts_array_N = 11'd1024; ///////////////////////////////////////////////////////////////////////////////////////////////

// All FFT MegaCore input signals are registered on the rising edge of the input clock, clk and

// all FFT MegaCore output signals are output on the rising edge of the input clock, clk.

////////////////////////////////////////////////////////////////////////////////////////////// // start valid for first cycle to indicate that the file reading should start.

reg start;

reg sink_valid_r;

always @ (posedge clk)

begin

if (reset_n == 'b0)

start <= 'b1;

else

begin

if (sink_valid_r == 'b1 & sink_ready == 1'b1)

start <= 'b0;

end

end ///////////////////////////////////////////////////////////////////////////////////////////////

// Read input data from files. Data is generated on the negative edge of the clock, clk, in the

// testbench and registered by the core on the positive edge of the clock \n";

///////////////////////////////////////////////////////////////////////////////////////////////

integer rc_x;

integer ic_x;

always @ (posedge clk)

begin

if(reset_n=='b0)

begin

sink_real<='b0;

sink_imag<='b0;

sink_valid_r <= 'b0;

end

else

begin

// send in NUM_FRAMES_c of data or until the end of the file

if((end_test == 'b1) || (end_input == 1'b1))

begin

sink_real<='b0;

sink_imag<='b0;

sink_valid_r <= 'b0;

end

else

begin

if ((sink_valid_r == 'b1 & sink_ready == 1'b1 ) ||

(start == 'b1 & !(sink_valid_r == 1'b1 & sink_ready == 'b0)))

begin

rc_x = $fscanf(data_rf,"%d",data_real_in_int);

sink_real <= data_real_in_int;

ic_x = $fscanf(data_if,"%d",data_imag_in_int);

sink_imag <= data_imag_in_int;

sink_valid_r <= 'b1;

end

else

begin

sink_real<=sink_real;

sink_imag<=sink_imag;

sink_valid_r <= 'b0;

end

end

end

end //////////////////////////////////////////////////////////////////////////////////////////////

// Write Real and Imginary Data Components and Block Exponent to Disk

//////////////////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk)

begin

if((reset_n=='b1) & (source_valid == 1'b1))

begin

fft_real_out_int = source_real;

fft_imag_out_int = source_imag;

$fdisplay(fft_rf, "%d", (fft_real_out_int < MAXVAL_c) ? fft_real_out_int : fft_real_out_int - OFFSET_c);

$fdisplay(fft_if, "%d", (fft_imag_out_int < MAXVAL_c) ? fft_imag_out_int : fft_imag_out_int - OFFSET_c);

exponent_out_int = source_exp;

$fdisplay(expf, "%d", (exponent_out_int < MAXVAL_EXP_c) ? exponent_out_int : exponent_out_int - OFFSET_EXP_c);

end

end ///////////////////////////////////////////////////////////////////////////////////////////////

// FFT Module Instantiation

/////////////////////////////////////////////////////////////////////////////////////////////

fft_ctrl

#(

.fftpts_n('d11),

.real_imag_wei('d16)

) fft_ctrl

(

//inputs

.clk (clk ),

.reset_n (reset_n ),

.sink_valid (sink_valid_r ),//拉高表示通知FFT即将有N个数据输入

.sink_real (sink_real ),//输入数据的实部

.sink_imag (sink_imag ),//输入数据的虚部

.inverse (inverse ),//0 - FFT 1 - IFFT 0

.fftpts_array_N (fftpts_array_N ), //采样的点数 1024 //output

.source_sop (source_sop ), //输出数据起始标记

.source_eop (source_eop ), //输出数据结束标记

.source_valid (source_valid), //置高,准备输出结果

//从时序看应该是sink_ready和sink_valid同步的

.sink_ready (sink_ready ),//FFT模块准备就绪,可以接收数据 output

.sink_sop (sink_sop),//输入数据起始标记脉冲(维持一个时钟的高电平),与第一个数据同步

.sink_eop (sink_eop),//输入数据结束标记脉冲(维持一个时钟的高电平),与最后一个数据同步

.source_real (source_real),//变换后输出数据的实部

.source_imag (source_imag),//变换后输出数据的虚部

.source_exp (source_exp ), //结果数据缩放因子:这

.end_input (end_input ), //数据输入结束

.end_test (end_test ), //数据输入结束 置1

.end_output (end_output )//数据输出结束

); endmodule

quartus ii FFT核使用的更多相关文章

- 关于网上quartus ii 生成fft核出现问题解决

------------恢复内容开始------------ 关于网上quartus ii 生成fft核出现问题解决 1:必须把软件破解啦 2:必须把IP核破解啦 破解步骤网上也有可以直接看,一定要全 ...

- Altera FFT核使用详解

简介 快速傅里叶变换(Fast Fourier Transform)最为一种高效的算法,被广泛的用于信号处理与数据分析等领域.对于设计工程师来讲,自己动手采样可编程语言来实现一个FFT/IFFT模块, ...

- [重要更新][Quartus II][14.1正式版]

[Quartus II][14.1正式版] ----14.1版本最大的变化就是增加了2大系列的器件库: MAX 10和Arria 10.这2大系列据Altera中国区代理 骏龙科技的人说,就是为了和X ...

- 【7集iCore3基础视频】7-6 Quartus II 13.1安装

Quartus II 13.1安装:高清源视频:链接:http://pan.baidu.com/s/1csVRMA 密码:lkth 视频勘误:http://pan.baidu.com/s/1mhCIq ...

- Quartus II USB-Blaster驱动解决

Quartus II USB-Blaster驱动解决 之前安装Quartus II 13.0,但FPGA开发板链接的USB-Blaster链接无法被Quartus识别,改装Quartus II 11. ...

- Quartus II 增量编译

在开发阶段,经常需要改代码,而且往往只改局部代码,但是编译的时候,通常会全部重新编译,这会很浪费时间,使得开发效率大大降低.那么有没有一种方法能够降低不必要的编译时间呢?通过查询Quartus II ...

- Quartus II 与 Modelsim 联调【转】

Quartus II 9.0版本的时候软件还有自带的仿真工具,现在安装的是11.0以上版本,才发现 Quartus II 11.0以上取消了软件自带的波形仿真工具,因此需要波形仿真就要调用专业的仿真工 ...

- Quartus ii 12.1软件破解之后编译原有的工程出现报警错误的解决办法

在Quartus ii 12.1软件破解之后,想用来编译原来编译过的工程,但是编译到最后出现下面两个错误警告: 原来以为没有破解成功或者安装的时候有文件被杀毒软件吃了,导致安装错误,又重新安装了两次都 ...

- Quartus ii 12.0 和ModelSim 10.1 SE安装及连接

quartus ii 10.0后就没有自带的仿真软件,每次写完一个VerilogHDL都想简单仿真一下,结果发现没有了自带仿真软件.这时候就需要第三方仿真软件ModelSim 10.1 SE. Qua ...

随机推荐

- vue项目中使用bpmn-节点篇

前情提要 根据之前的操作,我们可以创建.导入.导出流程图,并对其进预览.通过此篇可以学到: 为节点添加点击.鼠标悬浮等事件 获取流程图内所有指定类型的节点 通过外部更新节点名字 获取节点实例的两种方法 ...

- AI-web-1靶机过关记录

靶机地址:172.16.1.195 Kali地址:172.16.1.107 1.信息收集 端口扫描: 目录扫描: 发现robots.txt敏感文件,查看 存在/m3diNf0/,/se3reTdir7 ...

- Java IO 流 -- 数据流和对象流 DataOutputStream ObjectOutputStream

DataOutputStream 和 ObjectOutputStream的共同点是: 1.写出后读取 2.读取顺序和写出一致 数据流操作: // 写入 ByteArrayOutputStream b ...

- MySQL server has gone away(在执行sql的时候,莫名的报错)

原文:https://cenalulu.github.io/mysql/mysql-has-gone-away/ MySQL Server has gone away报错原因汇总分析 原因1. MyS ...

- php 全局变量和超全局变量

global 全局变量(在当前页面全部地方有效) $GLOBALS['name'] 超全局变量(在整个网站全部地方有效) 一个包含了全部变量的全局组合数组.变量的名字就是数组的键.还有_GET,_PO ...

- 2019-2020-1 20199308《Linux内核原理与分析》第五周作业

<Linux内核分析> 第四章 系统调用的三层机制(上) 4.1 用户态.内核态和中断 与系统调用打交道的方式是通过库函数的方式 用户态与内核态的区分 内核态:高的执行级别下,代码可以执行 ...

- Centos下安装Docker,并配置国内docker源

Centos下安装Docker 替换为国内的yum源(可选): mv /etc/yum.repos.d/CentOS-Base.repo /etc/yum.repos.d/CentOS-Base.re ...

- 日日算法:Dijkstra算法

介绍 Dijistra算法作为一种最短路径算法,可以用来计算一个节点到图上其他节点的最短距离. 主要是通过启发式的思想,由中心节点层层向外拓展,直到找到中点. 适用于无向图和有向图. 算法思想 假设我 ...

- 为物联网而生:高性能时间序列数据库HiTSDB商业化首发!

为什么80%的码农都做不了架构师?>>> 摘要: 近日,阿里云宣布高性能时间序列数据库 (High-Performance Time Series Database , 简称 H ...

- vue 遮罩层阻止默认滚动事件

vue中提供 @touchmove.prevent 方法可以完美解决这个问题. <div class="child" @touchmove.prevent ></ ...