zedboard如何从PL端控制DDR读写(三)——AXI-FULL总线调试

之前的项目和培训中,都只用到了AXI-Lite或者AXI-Stream,对于AXI-FULL知之甚少,主要是每次一看到那么多接口信号就望而却步了。

现在为了调试DDR,痛下决心要把AXI-FULL弄懂。

前面已经介绍了基本的接口信号,本文主要是总结一下使用AXI-FULL调试的过程。

首先想到的是用RAM IP核来测试,方法是通过AXI接口向RAM写入一组数据并读出,看起来很简单,然而试了好久都没能出结果。如下图所示,其实AXI RAM就是在本地RAM接口的基础上套了一个AXI的壳

在使用modelsim仿真的时候总是会抛出一个警告,具体的警告类型忘了,下次有机会再尝试。试了好多次都这样,无解

于是转用FIFO来测试,结果一下子就跑通了。

FIFO的自定义如下图:

一直没搞懂这个ID是用来干嘛的,按理说应该是当系统中存在多个master或者slave的时候,用来标识不同的设备号的,但是也没找到在哪里可以配置这个ID号啊,求解。

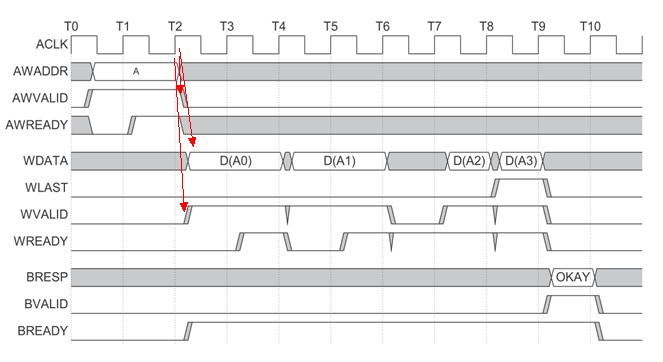

然后就是写状态机了,最初打算是用三段式状态机来实现下图的时序,结果发现三段式好像不太适合这种太紧凑的时序

具体的表现如图中箭头所示,当写时序从AW(写地址通道)切换到W(写数据通道)的时候,我是通过判断valid和ready同时拉高(1)则进入下一个状态即W状态(2)的,但是从(1)到(2)的跳变必须经历一个时钟,紧接着在第三段状态机中检测到(2)并且产生实际的输出(3)这个过程中,又会经历一个时钟,这就会导致图中的T1和T2之间多出来了一个周期,时序不满足了。无奈,又换成一段式状态机继续。

由于是对FIFO进行操作,burst类型自然选择是固定长度突发,写地址直接给0不变。这里说一下个人对wstrb的理解,前面也说了,这个信号是表示写阀门,也就是规定WDATA的哪些字节有效。实际上无论把wstrb写成全0还是全1,读出来的数据都是一样的,那么FIFO内部自然没有判断某些字节有效的逻辑,所以在后续读出的时候,需要由我们自行掩码。

除此之外,个人感觉看着这一大堆的接口,首先不要怕,把所有的接口信号按不同的通道分成5组,一次只操作其中的一组,慢慢的就能完成整个时序的编写了。

最后附上读写的仿真结果:

数据用$random产生,再加上状态机,整个时序如行云流水般的运作起来了,想想还有点小兴奋呢

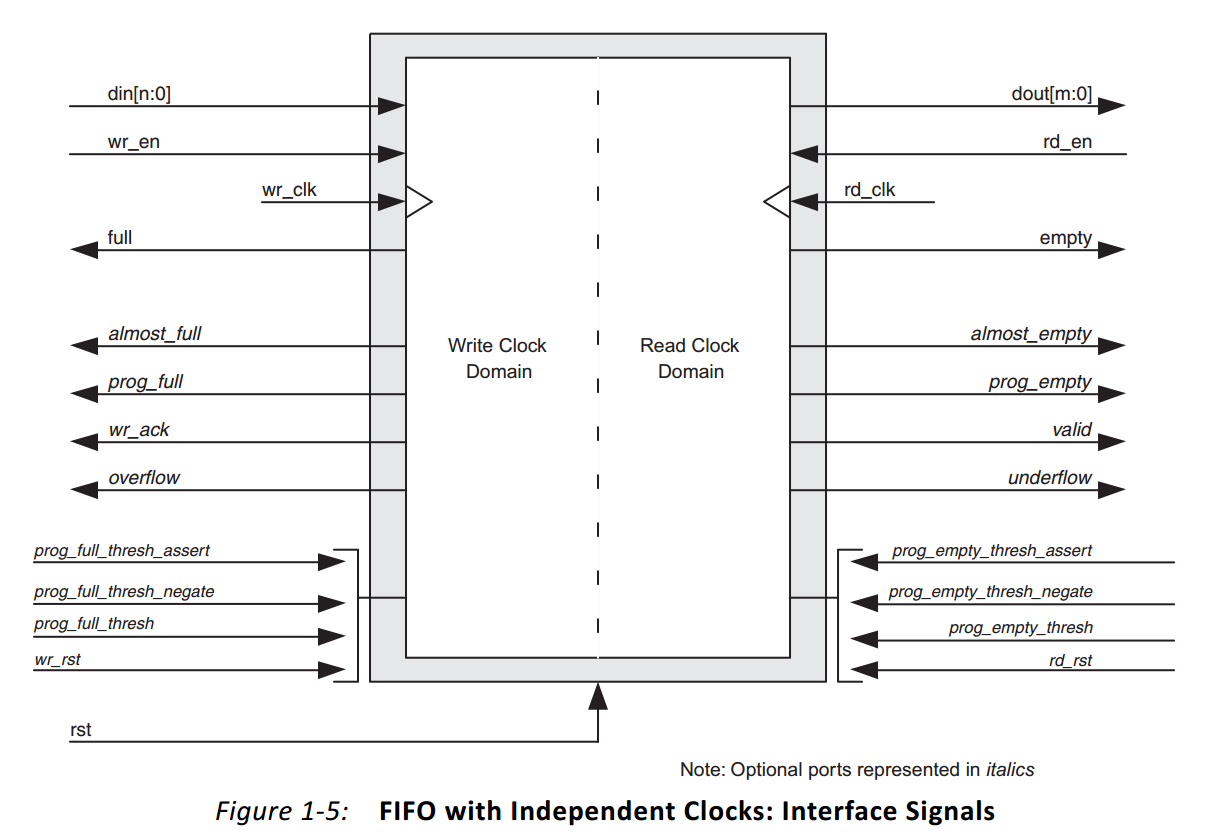

既然已经看了RAM的xilinx文档,那么FIFO的也得看,这样才能显得雨露均沾。

先来一张正常本地端口FIFO结构图

所有的信号都还蛮熟悉,结构也还算了解,无非就是同一个FIFO的两个时钟域。

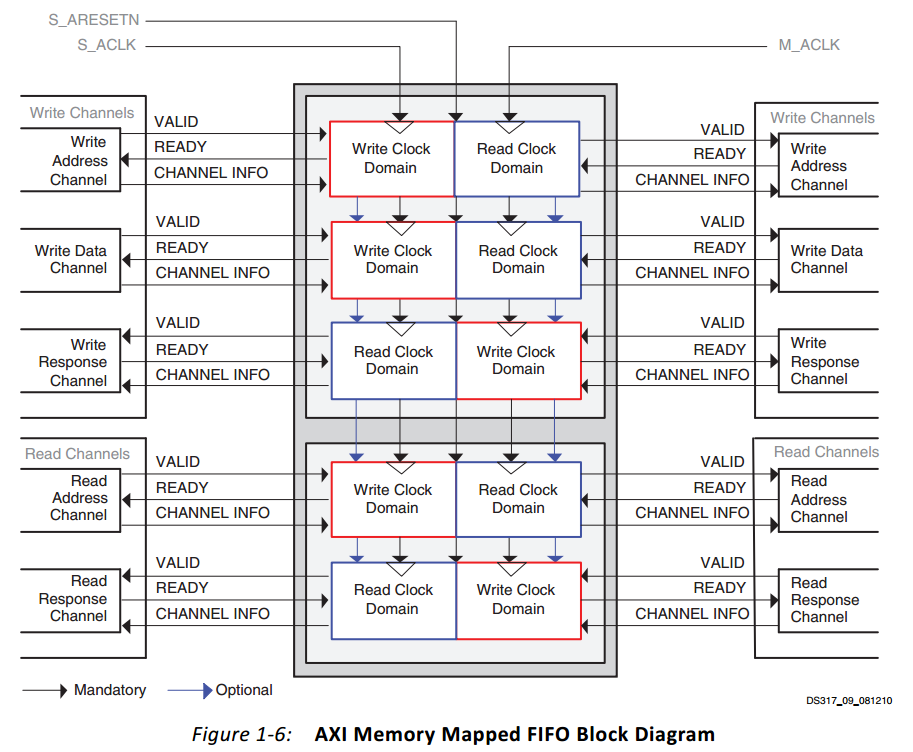

接着再看AXI接口的FIFO:

这都什么鬼啊,红线蓝线,那么多独立的模块,这是要干嘛?

自习阅读官方文档,有这么一段话:

For AXI memory mapped interfaces, AXI specifies Write Channels and Read Channels. Write Channels include a Write Address Channel, Write Data Channel and Write Response Channel. Read Channels include a Read Address Channel and Read Data Channel. The FIFO Generator core provides the ability to generate either Write Channels or Read Channels, or both Write Channels and Read Channels for AXI memory mapped. Three FIFOs are integrated for Write Channels and two FIFOs are integrated for Read Channels. When both Write and Read Channels are selected, the FIFO Generator core integrates five independent FIFOs.

For AXI memory mapped interfaces, the FIFO Generator core provides the ability to implement independent FIFOs for each channel, as shown in Figure 1-6. For each channel, the core can be independently configured to generate a block RAM or distributed memory or built-in based FIFO. The depth of each FIFO can also be independently configured.

也就是说,每一个AXI通道最后都会生成成一个独立的跨时钟域FIFO,我们一开始将FIFO的类型配置成了读写,也就是五个通道全开,那么自然就是五个独立的FIFO了。

这得占用多少资源啊,还好只是测试,不用考虑那么多。

zedboard如何从PL端控制DDR读写(三)——AXI-FULL总线调试的更多相关文章

- zedboard如何从PL端控制DDR读写(二)——AXI总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的. AXI(Ad ...

- zedboard如何从PL端控制DDR读写(七)

前面已经详细介绍了从PL端如何用AXI总线去控制DDR的读写,并且从AXI_BRESP的返回值来看,我们也是成功写入了的.但是没有通过别的方式来验证写入的数据的话,总是感觉差了点什么. 今天试了一把从 ...

- zedboard如何从PL端控制DDR读写(五)

有了前面的一堆铺垫.现在终于开始正式准备读写DDR了,开发环境:VIVADO2014.2 + SDK. 一.首先要想在PL端通过AXI去控制DDR,我们必须要有一个AXI master,由于是测试,就 ...

- zedboard如何从PL端控制DDR读写(六)

上一节说到了DDR寻址的问题,如下图: 从官方文档上我们看到了DDR的地址是从0008_0000开始的,那么我们开始修改Xilinx给我们提供的IP核代码.其实很简单,上一节已经分析了地址停留在000 ...

- zedboard如何从PL端控制DDR读写(四)

PS-PL之间的AXI 接口分为三种:• 通用 AXI(General Purpose AXI) — 一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信.接口是透传的不带缓冲.总共有四个通 ...

- zedboard如何从PL端控制DDR读写(一)

看了一段时间的DDR手册,感觉大体有一点了解了,想要实际上板调试,然而实验室可用的开发板不多,拿了一块zynq板看了看,DDR确实有,但是已经集成了控制器,而且控制器还放到了PS端,PL只能通过AXI ...

- 第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- 第十一章 ZYNQ-MIZ701 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- MIG IP控制DDR3读写测试

本文设计思想采用明德扬至简设计法.在高速信号处理场合下,很短时间内就要缓存大量的数据,这时片内存储资源已经远远不够了.DDR SDRAM因其极高的性价比几乎是每一款中高档FPGA开发板的首选外部存储芯 ...

随机推荐

- mysql server has gone away 与max_allowed_packed

今天在本地测试测试给所有店铺批量发信息的功能,大约2万条记录,在本地和备用linux服务器上测试都没有问题,但上windows时一直报mysql server has gone away的错误,搜索一 ...

- setInterval()和setTimeout()的区别

一.setInterval()函数的语法结构: setInterval(code,interval) setInterval()函数可周期性执行一段代码,也就是说代码会被周期性不断的执行下去. 函数具 ...

- 播放wav聲音格式

1. #import <AudioToolbox/AudioToolbox.h> 2.聲明 成員变量 SystemSoundID soundID; 3.播放 - (void)playSou ...

- Java基础-绘图技术

- {JavaScript}栈和堆内存,作用域

1.栈 stack”和“堆 heap”: 简单的来讲,stack上分配的内存系统自动释放,heap上分配的内存,系统不释放,哪怕程序退出,那一块内存还是在那里.stack一般是静态分配 ...

- HashCode equals

HashCode: hashcode就是一个签名.当两个对象的hashcode一样时,两个对象就有可能一样.如果不一样的话两个对象就肯定不一样.一般用hashcode来进行比较两个东西是不是一样的,可 ...

- Esfog_UnityShader教程_漫反射DiffuseReflection

这篇是系列教程的第三篇,最近工作比较紧,所以这个周六周日就自觉去加了刚回来就打开电脑补上这篇,这个系列的教程我会尽量至少保证一周写一篇的.如果大家看过我的上一篇教程<Esfog_UnitySha ...

- js压缩反压缩

JavaScript unpacker and beautifier JavaScript Beautifier http://prettydiff.com/?m=beautify&s=htt ...

- OC基础(3)

对象的存储细节 函数与方法对比 常见错误 *:first-child { margin-top: 0 !important; } body > *:last-child { margin-bot ...

- Redis附加功能之Redis事务

一.事务 Redis 的事务功能允许用户将多个命令包裹起来,然后一次性地.按顺序地执行被包裹的所有命令.在事务执行的过程中,服务器不会中断事务而改去执行其他命令请求,只有在事务包裹的所有命令都被执行完 ...