zedboard如何从PL端控制DDR读写(七)

前面已经详细介绍了从PL端如何用AXI总线去控制DDR的读写,并且从AXI_BRESP的返回值来看,我们也是成功写入了的。但是没有通过别的方式来验证写入的数据的话,总是感觉差了点什么。

今天试了一把从PS端直接读取DDR里面的数据,刚好跟PL端写入的一样,这下可以放心的认为我们写入成功了。

还是跟前面说的一样,在SDK里面使用hello world的模版就可以了。

准备工作:(这部分参考了【ZYNQ-7000开发之六】使用PS控制DDR3的读写)

1、DDR3的地址

在mem_demo_bsp->ps7->cortexa9_0的路径下,打开xparameters_ps.h这个头文件,这个头文件是cortexA9可以直接控制的外设地址的宏定义。在里面可以找到DDR的地址,可以看到如下代码:

/* Canonical definitions for DDR MEMORY */

#define XPAR_DDR_MEM_BASEADDR 0x00000000

#define XPAR_DDR_MEM_HIGHADDR 0x3FFFFFFF

可以看出来,这里的地址也包括了一部分OCM,等会我们要使用这个地址,对DDR3进行读写操作。

2、读写操作函数

在mem_demo_bsp->ps7->cortexa9_0的路径下,打开xil_io.h这个头文件,这个头文件是cortexA9可以直接控制的内存映射或者映射到了地址空间的IO。在里面可以看到如下代码:

//从某个地址读数据

u8 Xil_In8(INTPTR Addr);

u16 Xil_In16(INTPTR Addr);

u32 Xil_In32(INTPTR Addr); //向某个地址写数据。

void Xil_Out8(INTPTR Addr, u8 Value);

void Xil_Out16(INTPTR Addr, u16 Value);

void Xil_Out32(INTPTR Addr, u32 Value);

有了这些就可以简单的对DDR进行续写操作了。在这里,我们只尝试从PL写入,从PS读取。(你问我为什么不测试从PS写入,从PL读取,因为PL部分的代码之前已经写好了,再去综合一遍太麻烦 )

)

代码如下:

/*

* Copyright (c) 2009-2012 Xilinx, Inc. All rights reserved.

*

* Xilinx, Inc.

* XILINX IS PROVIDING THIS DESIGN, CODE, OR INFORMATION "AS IS" AS A

* COURTESY TO YOU. BY PROVIDING THIS DESIGN, CODE, OR INFORMATION AS

* ONE POSSIBLE IMPLEMENTATION OF THIS FEATURE, APPLICATION OR

* STANDARD, XILINX IS MAKING NO REPRESENTATION THAT THIS IMPLEMENTATION

* IS FREE FROM ANY CLAIMS OF INFRINGEMENT, AND YOU ARE RESPONSIBLE

* FOR OBTAINING ANY RIGHTS YOU MAY REQUIRE FOR YOUR IMPLEMENTATION.

* XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO

* THE ADEQUACY OF THE IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO

* ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE

* FROM CLAIMS OF INFRINGEMENT, IMPLIED WARRANTIES OF MERCHANTABILITY

* AND FITNESS FOR A PARTICULAR PURPOSE.

*

*/ /*

* helloworld.c: simple test application

*

* This application configures UART 16550 to baud rate 9600.

* PS7 UART (Zynq) is not initialized by this application, since

* bootrom/bsp configures it to baud rate 115200

*

* ------------------------------------------------

* | UART TYPE BAUD RATE |

* ------------------------------------------------

* uartns550 9600

* uartlite Configurable only in HW design

* ps7_uart 115200 (configured by bootrom/bsp)

*/ #include <stdio.h>

#include "platform.h"

#include "xparameters.h"

#include "xparameters_ps.h"

#include "xil_printf.h"

#include "xil_io.h" #define DDR_BASEARDDR XPAR_DDR_MEM_BASEADDR + 0x3ffff000 //只读取DDR中的一部分数据

#define DDR_HIGHADDR XPAR_DDR_MEM_HIGHADDR //void print(char *str); int main()

{

init_platform(); int i=;

int rev; print("Hello World\n\r"); while(DDR_BASEARDDR+i*<DDR_HIGHADDR){

rev = Xil_In32(DDR_BASEARDDR+i*);

xil_printf("the address at %x data is : %d \n\r" ,DDR_BASEARDDR+i*, rev);

++i;

} cleanup_platform(); return ;

}

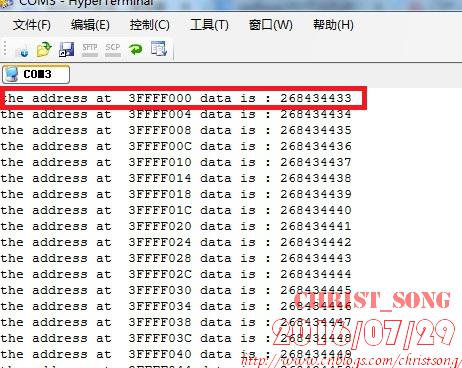

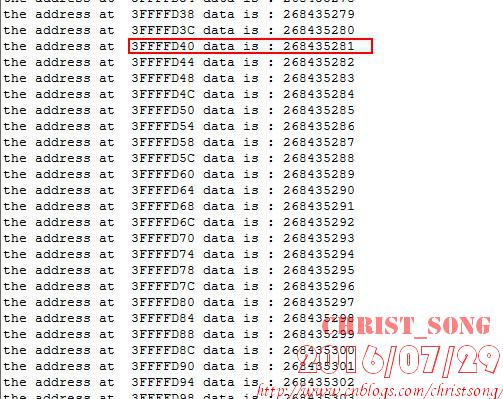

我是从0x3ffff000开始读取数据的,当然从开头读起来也一样。接下来看串口返回的部分数据:

完全正确!接下来我要去别的地方闷声发大财了

zedboard如何从PL端控制DDR读写(七)的更多相关文章

- zedboard如何从PL端控制DDR读写(五)

有了前面的一堆铺垫.现在终于开始正式准备读写DDR了,开发环境:VIVADO2014.2 + SDK. 一.首先要想在PL端通过AXI去控制DDR,我们必须要有一个AXI master,由于是测试,就 ...

- zedboard如何从PL端控制DDR读写(六)

上一节说到了DDR寻址的问题,如下图: 从官方文档上我们看到了DDR的地址是从0008_0000开始的,那么我们开始修改Xilinx给我们提供的IP核代码.其实很简单,上一节已经分析了地址停留在000 ...

- zedboard如何从PL端控制DDR读写(四)

PS-PL之间的AXI 接口分为三种:• 通用 AXI(General Purpose AXI) — 一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信.接口是透传的不带缓冲.总共有四个通 ...

- zedboard如何从PL端控制DDR读写(一)

看了一段时间的DDR手册,感觉大体有一点了解了,想要实际上板调试,然而实验室可用的开发板不多,拿了一块zynq板看了看,DDR确实有,但是已经集成了控制器,而且控制器还放到了PS端,PL只能通过AXI ...

- zedboard如何从PL端控制DDR读写(三)——AXI-FULL总线调试

之前的项目和培训中,都只用到了AXI-Lite或者AXI-Stream,对于AXI-FULL知之甚少,主要是每次一看到那么多接口信号就望而却步了. 现在为了调试DDR,痛下决心要把AXI-FULL弄懂 ...

- zedboard如何从PL端控制DDR读写(二)——AXI总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的. AXI(Ad ...

- 第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- 第十一章 ZYNQ-MIZ701 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- MIG IP控制DDR3读写测试

本文设计思想采用明德扬至简设计法.在高速信号处理场合下,很短时间内就要缓存大量的数据,这时片内存储资源已经远远不够了.DDR SDRAM因其极高的性价比几乎是每一款中高档FPGA开发板的首选外部存储芯 ...

随机推荐

- 表单验证 jQuery Validate

http://www.runoob.com/jquery/jquery-plugin-validate.html http://www.cnblogs.com/linjiqin/p/3431835.h ...

- Python 基礎 - 數據類型

標準數據類型 Python3 中有六個標準的數據類型 1 Number(數字) 2 String(字符串) 3 List (列表) 4 Tuple (元組) 5 Sets (集合) 6 Diction ...

- sge学习 (转)

转自http://biancheng.dnbcw.info/linux/417992.html 命令: qsub - submit a batch job to Grid Engine. qsh ...

- linux iftop流量查看工具的安装与使用

1.安装依赖包yum install flex byacc libpcap ncurses ncurses-devel libpcap-devel 2.下载iftop wget http://www ...

- github 如何合并不同分支

From: http://stackoverflow.com/questions/1123344/merging-between-forks-in-github 1. 添加remote origina ...

- AndroidStudio开发出现Warning:Gradle version 2.10 is required. Current version is 2.8. If u

Warning:Gradle version 2.10 is required. Current version is 2.8. If using the gradle wrapper, try ed ...

- Nginx-ngx_lua模块原理和内置函数

ngx_lua模块的原理: 1.每个worker(工作进程)创建一个Lua VM,worker内所有协程共享VM:2.将Nginx I/O原语封装后注入 Lua VM,允许Lua代码直接访问:3.每个 ...

- ArcGIS+API+for+JS测距

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/ ...

- Sea.js学习5——Sea.js的构建工具spm

如果项目遵循推荐的标准目录结构: foo-module/ |-- dist 存放构建好的文件 |-- src 存放 js.css 等源码 | |-- foo.js | `-- style.css `- ...

- gridview的行选择的一个问题

我想实现这样一个效果:单击gridview的行内任意地方都可以选择该行(就是行内复选框被选中),同时修改该行的背景色.当再次单击行内任意地方又可以取消选择.另外,当单击选择行内复选框时,我希望可以选择 ...