Cortex-M3内核介绍

目录

Cortex Vendor - ARM介绍

- ARM主要提供指令集,需要授权

- ARM使用的RSIC结构,功耗比较低

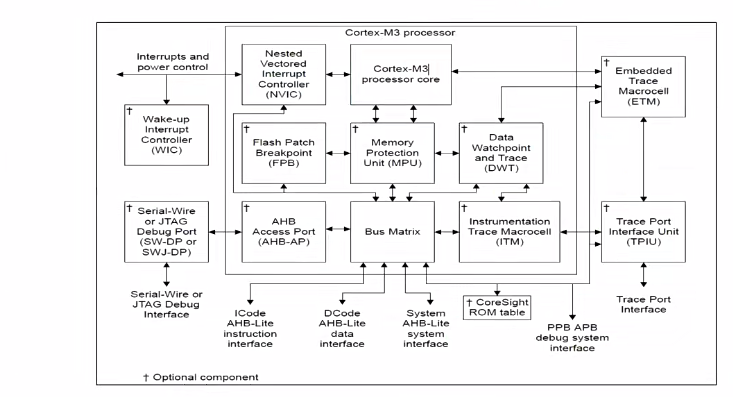

Cortex M3整体架构

- 核心是Processor Core - 包含寄存器和累加单元,指令的取指,译码,执行单元

- Nested Vectored Interrupt Controller(向量中断控制) - 外部中断进来,可以直接上报,不需要查中断号及服务程序;

- Processor Core有指令总线和数据总线 - 指令和数据分离,指令和数据可以并行处理

- Memory Protection Unit(MPU)- 对地址进行约束和保护,一些地址只能是指令单元访问,不能数据单元访问,防止内存踩踏,可以理解为特殊地址单元的保护;可以设置privilege和user权限,priviledge用于操作系统访问,user用于用户软件访问,有些地址可以操作系统进行读写,用户不能读写,进行区分

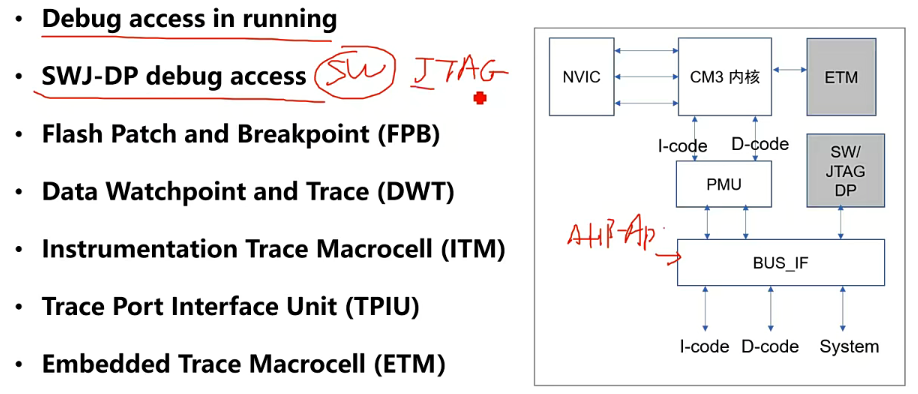

- Flash Patch Breakpoint(FPB)

- Data Watchpoint and Trace(DWT)

- Bus Matrix - 进行指令的译码

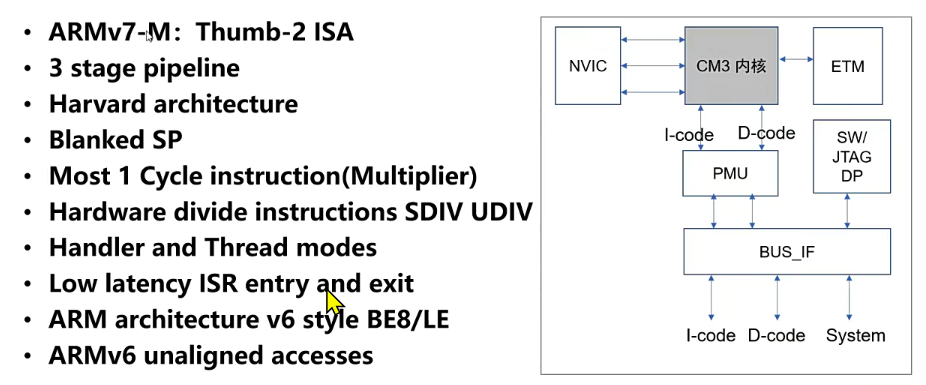

Cortex CM3 内核特性

- 支持Thumb 16bit的指令集,ARM 32bit指令集;ARM指令集位宽多,功能更强

- 支持Thumb-2 ISA 可以支持16bit和32bit指令

- 支持3级流水-取指\译码\执行的时候可以同时执行

- harvard architecture - 将指令存储和数据存储进行分开

- blanked SP - 有两套堆栈,一个是系统进行访问的,一个是用户进行访问的

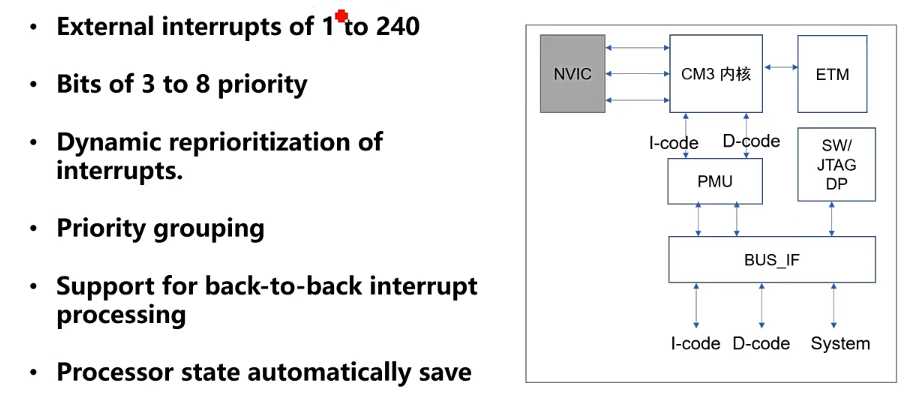

Cortex CM3 嵌套中断向量

- priority - 不同的中断可以设置不同的中断的优先级

- back-to-back - 中断的咬尾操作,高优先级的中断可以终止低优先级的中断,低优先级的中断不用进行出栈操作,可以提高中断处理程序的执行效率

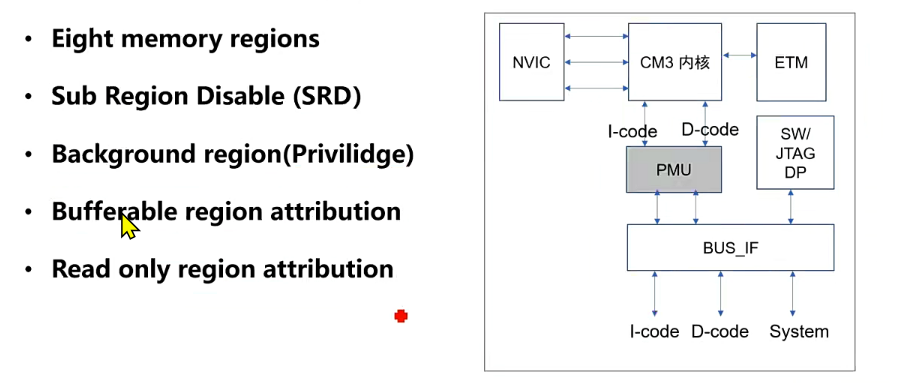

Cortex M3 MPU保护单元

- 支持8个memory region - 可以指定不同区域设置不同的访问权限

- 设置缓存进行加速

- 可以设置读写权限

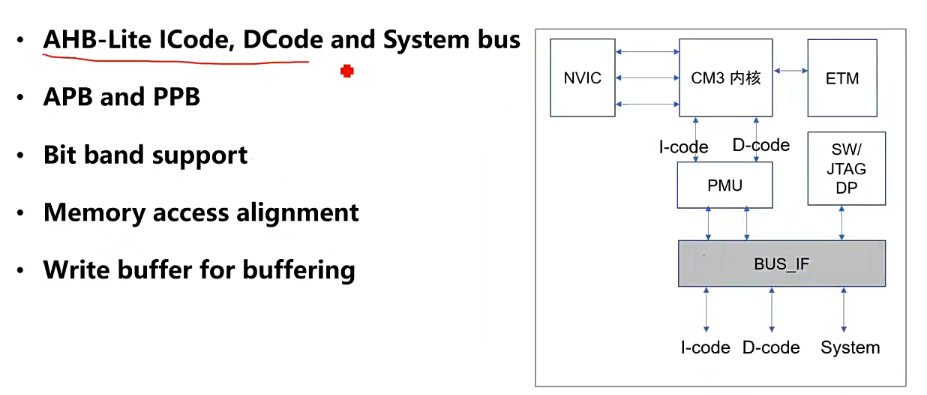

Cortex M3 总线接口

- PPB BUS - 用于调试单元

Cortex M3 低成本调试接口

Cortex-M3内核介绍的更多相关文章

- ARM Cortex M3系列GPIO口介绍(工作方式探讨)

一.Cortex M3的GPIO口特性 在介绍GPIO口功能前,有必要先说明一下M3的结构框图,这样能够更好理解总线结构和GPIO所处的位置. Cortex M3结构框图 从图中可以看出 ...

- stm32和cortex M3学习内核简单总结

1.stm32综述 2.寄存器组 3.操作模式和特权级别 4.存储器映射 5.中断和异常 6.其他 Stm32综述 这可以说是我第一款认真学习的单片机了,学完这个就要开启我通往arm9的大门了,接下来 ...

- STM32 M3内核的位带操作原理及步骤

STM32 M3内核的位带操作原理及步骤 一.位带操作有什么用?什么是位带操作 位带操作的作用:可以实现对某一GPIO口寄存器(或SRAM内存中)的某一bit位直接写0或1,达到控制GPIO口输出(或 ...

- ARM 架构、ARM7、ARM9、STM32、Cortex M3 M4 、51、AVR 之间有什么区别和联系?(转载自知乎)

ARM架构: 由英国ARM公司设计的一系列32位的RISC微处理器架构总称,现有ARMv1~ARMv8种类. ARM7: 一类采用ARMv3或ARMv4架构的,使用冯诺依曼结构的内核. ...

- STM32学习之路入门篇之指令集及cortex——m3的存储系统

STM32学习之路入门篇之指令集及cortex——m3的存储系统 一.汇编语言基础 一).汇编语言:基本语法 1.汇编指令最典型的书写模式: 标号 操作码 操作数1, 操作数2,... ...

- 【freertos】002-posix模拟器设计与cortex m3异常处理

目录 前言 posix 标准接口层设计 模拟器的系统心跳 模拟器的task底层实质 模拟器的任务切换原理 cortex M3/M4异常处理 双堆栈指针 双操作模式 栈帧 EXC_RETURN 前言 如 ...

- ARM Cortex M3(V7-M架构)硬件启动程序 一

Cortex-m3启动代码分析笔记 启动代码文件名是STM32F10X.S,它的作用先总结下,然后再分析. 启动代码作用一般是: 1)堆和栈的初始化: 2)中断向量表定义: 3)地址重映射及中断向量表 ...

- Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors

Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors The goal of the pro ...

- 【ARM-Linux开发】ARM7 ARM9 ARM Cortex M3 M4 有什么区别

ARM7 ARM9 ARM Cortex M3 M4 区别 arm7 arm9 可以类比386和奔腾, 不同代,arm9相比arm7指令集和性能都有所增强,arm7和arm9都有带mmu和无mmu的版 ...

- 各大浏览器内核介绍(Rendering Engine)

在介绍各大浏览器的内核之前,我们先来了解一下什么是浏览器内核. 所谓浏览器内核就是指浏览器最重要或者说核心的部分"Rendering Engine",译为"渲染引擎&qu ...

随机推荐

- Critical error detected c0000374

我发现出现上述错误是 free 两次内存 float* dd=new float[2]; delete[] dd; delete[] dd;

- Scrapy在pipeline中集成mongodb

settings.py中设置配置项 MONGODB_HOST = "127.0.0.1" MONGODB_PORT = 27017 MONGODB_DB_NAME = " ...

- Keepass调用Xshell、SecureCRT、RDP、Putty的方法(一劳永逸版)

依次点击"工具"--"选项"--"集成"--"网址替代"--"添加"--添加"方案&quo ...

- C语言之输出孪生素数

1.题目内容: 孪生素数是指间隔为 2 的相邻素数,例如最小的孪生素数对是3和5,5和7也是(5虽重复但算作2组). 2.输入格式: 输入N,找出2至N之间的孪生素数的组数. 这里要注意输入的N不要超 ...

- 扩展 jQurey.i18n.properties 的能力来向 vue-i18n 靠齐

jQuery.i18n.properties 是 jQuery 老项目的国际化框架,其实国际化方案本质上都大同小异,都是需要用翻译函数包裹词条,然后根据词条文件来进行翻译 就是使用上与其他框架不太一样 ...

- JavaFx之整合JFoenix(十四)

JavaFx之整合JFoenix JFoenix是JavaFx流行的UI框架之一 github:https://github.com/sshahine/JFoenix 整合Maven <!--h ...

- 目标检测 | Point Cloud RoI Pooling

目录 目标检测 | Point Cloud RoI Pooling Point Cloud RoI Pooling 概述 Pooling RoI Pooling Point Cloud RoI Poo ...

- 斯坦福 UE4 C++ ActionRoguelike游戏实例教程 14. 使用GameplayTag实现防守反击技能

斯坦福课程 UE4 C++ ActionRoguelike游戏实例教程 0.绪论 概述 本篇文章对应Lecture 17 - GameplayTags, 70节.本文将会结合前几节课使用的能力系统和G ...

- 微信小程序中的数组有许多常用的方法和用法

声明和初始化一个数组: var array = []; // 声明一个空数组 var array = [1, 2, 3]; // 声明并初始化一个有元素的数组 获取数组长度: var length = ...

- 关于GaussDB(DWS)的正则表达式知多少?人人都能看得懂的详解来了!

摘要:GaussDB(DWS)除了支持标准的POSIX正则表达式句法,还拥有一些特殊句法和选项,这些你可了解?本文便为你讲解这些特殊句法和选项. 概述 正则表达式(Regular Expression ...