A/X家FPGA架构及资源评估

评估对比xilinx以及altera两家FPGA芯片逻辑资源。

首先要说明,

- 现今FPGA除了常规逻辑资源,还具有很多其他片内资源比如块RAM、DSP单元、高速串行收发器、PLL、ADC等等,用以应对不同的场合,逻辑量只能作为选型的重要依据之一。

- 不同厂家FPGA架构各异,具有很多独有的专利设计,量级相当的FPGA在应对不同应用场景下(比如视频处理、通讯总线、加密算法)时表现可能会差异很大,逻辑资源评估只是作为通常意义上的选型参考。

本文以占有率最大的X家和A家为例来进行比较。

首先对比下两家的芯片架构,

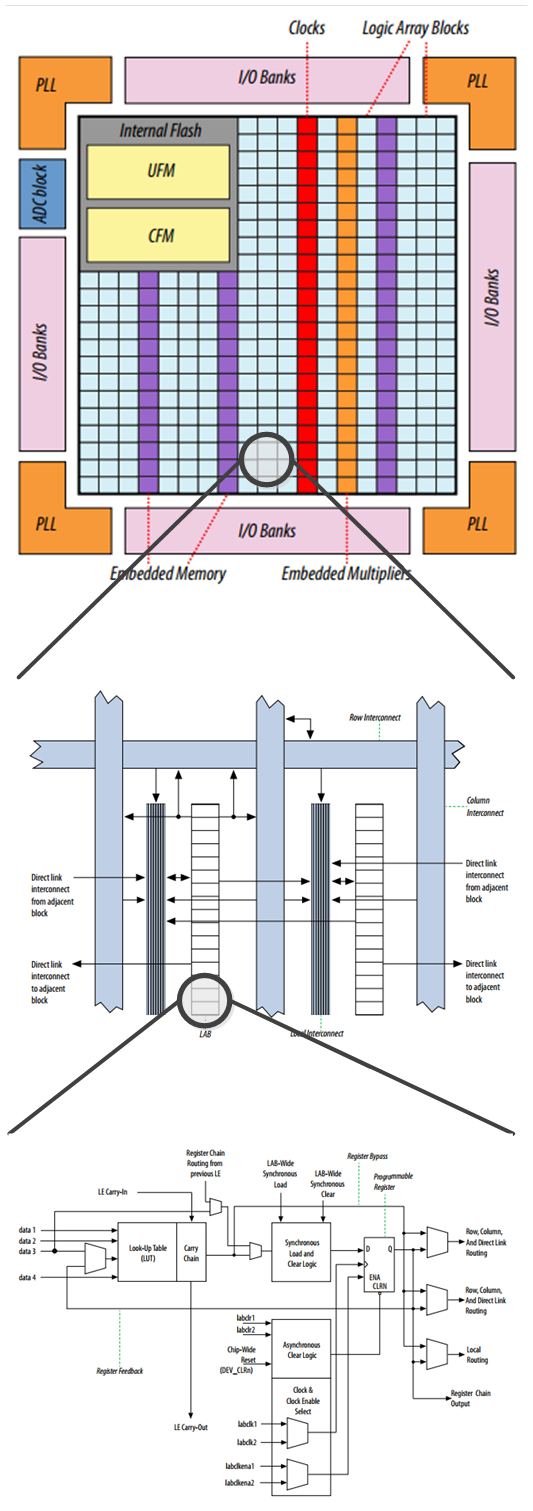

Altera LUT4架构(以入门级MAX10为例,以下材料来源于m10_handbook)

基本的逻辑单元由LAB组成,每个LAB包含16个LE,LE主要由一个LUT-4以及一个触发器。

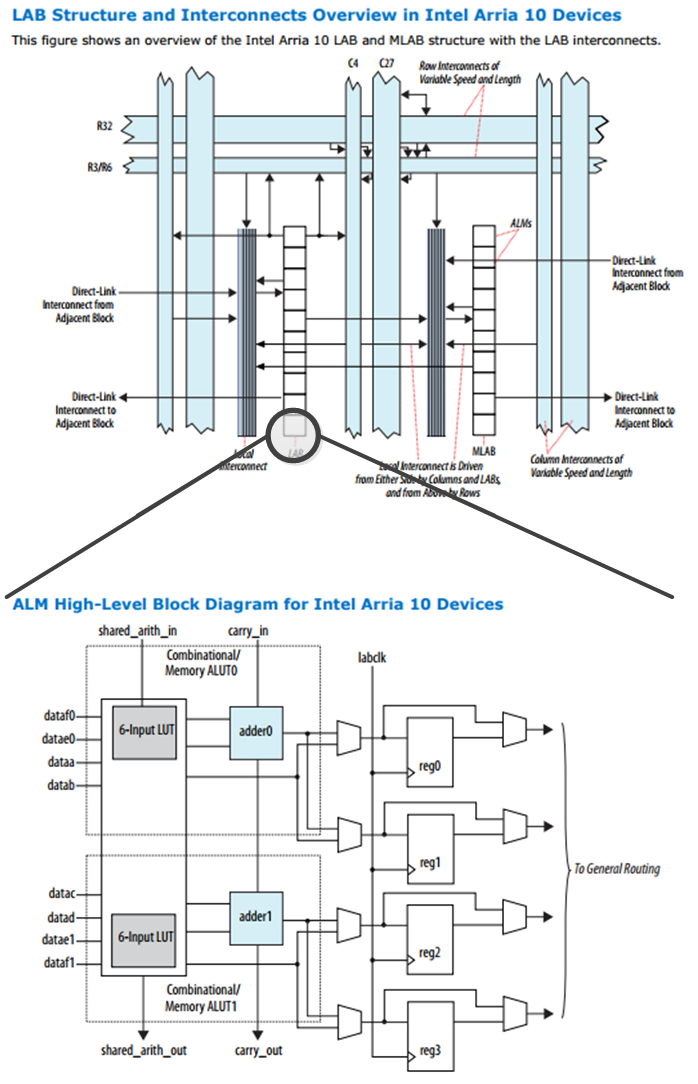

Altera ALM架构(以Arria10系列为参考)

基本逻辑单元LAB包含10xALM,ALM全程为Adaptive Logic Module,具有8输入和2输出,一个ALM可以配置成不同的LUT组合,比如2个单独LUT4、单独LUT5+LUT3、共享一个输入的LUT5+LUT4等等。ALM相比单独的LUT4架构显然具有更大的灵活性。

(a10_handbook.pdf)

Xilinx(以7系列为例)

赛灵思基本逻辑单元叫做CLB,CLB内有具有两片Slice,每个Slice由4片LUT6及8个触发器组成。可见每个CLB约等于8 x LUT6。

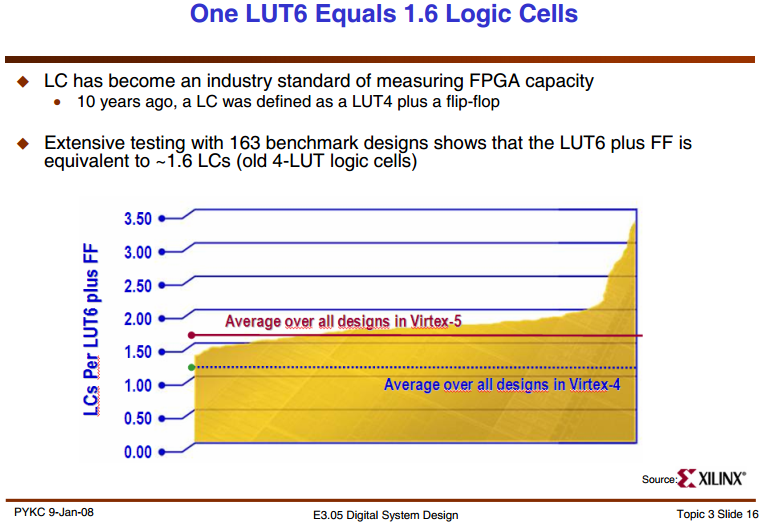

由于最早的FPGA多为基于LUT4组成,惯用的做法是用LUT4的数量近似表示逻辑量。现在FPGA不一定是基于LUT4,但可以转换成等效LUT4数量。XIlinx的叫做LC,ALTERA叫做LE,都可以理解成一个LUT4加触发器的单元的数量。

对MAX10来说,LE的数量就等于LUT4的数量,而xilinx 7系列基于LUT6,LUT与LC有如下换算关系:

A/X家FPGA架构及资源评估的更多相关文章

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- Serverless 的资源评估与成本探索

Serverless 布道师在讲解 Serverless 架构和云主机等区别的时候,总会有类似的描述: 传统业务开发完成想要上线,需要评估资源使用.根据评估结果,购买云主机,并且需要根据业务的发展不断 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- 浅谈FPGA资源评估

在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源. FF和LUT的数目: 这个在写出具体代码之前,初学者通常没法估算,但资深FPGA工程师会估算出一个数量级.通常的做法 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- Kubernetes(二)架构及资源关系简单总结

Kubernetes架构 先引用一下官方的架构图: 对于本文来说,我觉得这张图有点复杂了,但是我又懒得自己画了,就用这张吧.Kubernetes是一个集群,和传统的集群相似,它也是有一个主节点和若干个 ...

- 3、flink架构,资源和资源组

一.flink架构 1.1.集群模型和角色 如上图所示:当 Flink 集群启动后,首先会启动一个 JobManger 和一个或多个的 TaskManager.由 Client 提交任务给 JobMa ...

- 对FPGA的时钟资源理解(更新中)

7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟.内部时钟进行处理,生成需要的低抖动时钟.PLL是MMCM的功能子集, ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

随机推荐

- MYSQL:alter语句中change和modify的区别

您可以使用CHANGE old_col_namecolumn_definition子句对列进行重命名.重命名时,需给定旧的和新的列名称和列当前的类型.例如:要把一个INTEGER列的名称从a变更到b, ...

- 深透清晰理解Java高并发概述

1.多线程安全性 多线程安全性的定义可能众说纷纭,但是其最核心的一点就是正确性,也就是程序的行为结果和预期一致. 当多个线程访问某个类时,不管运行环境采用何种线程调度算法或者这些线程如何交替执行,且不 ...

- SQLAlchemy框架用法详解

介绍 SQLAlchemy是一个基于Python实现的ORM框架.该框架建立在 DBAPI之上,使用关系对象映射进行数据库操作,简言之便是:将类和对象转换成SQL,然后使用数据API执行SQL并获取执 ...

- 【CSS3 transform属性和过渡属性详解】

CSS3transform属性详解 transform字面上就是变形,改变的意思. 在CSS3中transform主要包括以下几种:旋转rotate.扭曲skew.缩放scale和移动translat ...

- XML(一)XML大揭秘

前言 每天都要学习很多新的知识,比你厉害的程序员比你还努力,那你混的下这口饭吗?所以不抱怨,坚持!接下来给大家分享的是xml.可能很多做开发的都遇到过xml, 比如maven,各种框架的配置文件都有, ...

- [bzoj1819] [JSOI]Word Query电子字典

正解是trie树...在树上跳来跳去什么的 然而在企鹅qq那题的影响下我写了hash... 添加一个字母到一个串,就相当于另一个串删对应位置上的字母. 改变某个位置上的字母,就相当于两个字符串删掉同一 ...

- 2017ecjtu-summer training # 9 HDU 4544

湫湫系列故事--消灭兔子 Time Limit: 3000/1000 MS (Java/Others) Memory Limit: 65535/32768 K (Java/Others)Tota ...

- linux管理面板

小编在这儿给大家介绍几款linux管理面板,希望感兴趣的童鞋可以去尝试下.个人觉得宝塔和appnode这两个面板不仅从功能和样式都还是做的比较好的,但是部分功能是收费的,但是webmin绝对是一款免费 ...

- 解决JSONObject.fromObject数字为null时被转换为0

在使用JSONObject.fromObject的时候会遇到一种情况就是当对象的某一个Double型或Integer型的属性为空的时候,转JSON的时候会变成0.当一个布尔型的属性为空的时候,转JSO ...

- linux下删除.svn的方法

find ./ -type d -name ".svn" | xargs rm -rf