07模块化设计之top_down

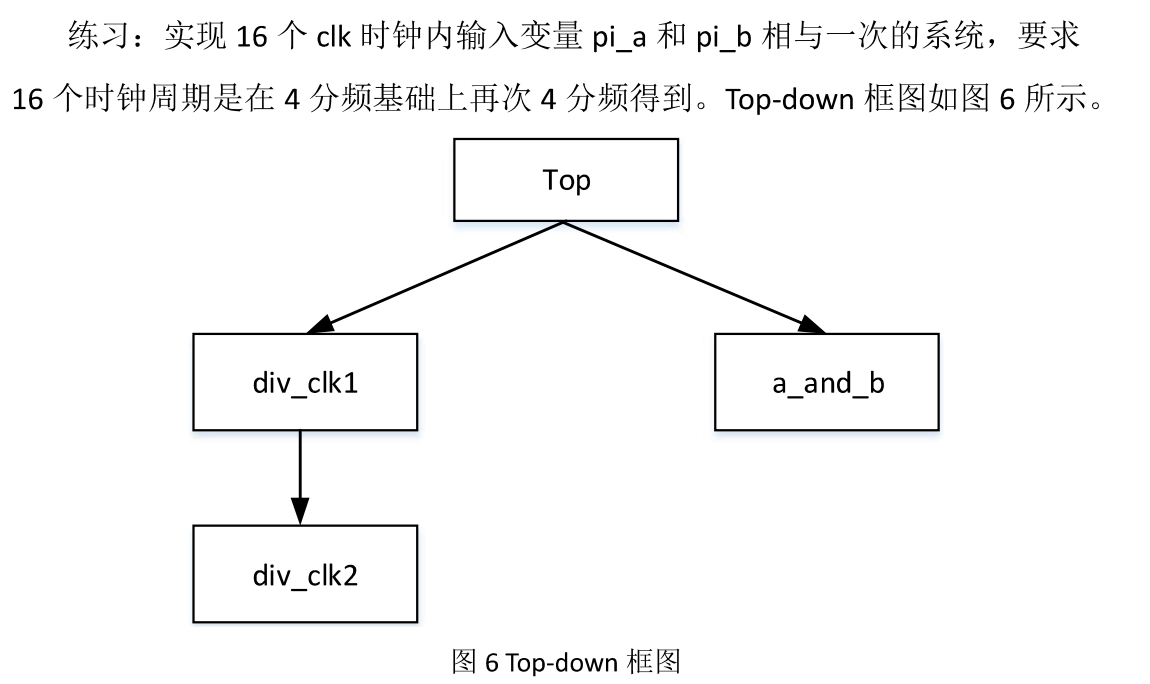

一设计功能:(一)用两个分频模块,实现16分频,且让输入a 和b在16个系统时钟内,相与一次。

|

|

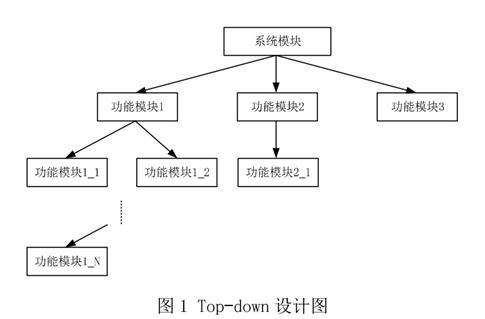

(二)模块化设计思想(结构化思维)

拆分,即把一个系统划分成多个功能模块,控制模块,组合模块。然后从功能模块开始,循序渐进一个个设计好,再把所有的模块连接起来,实现系统功能。

|

二设计输入

(一)顶层模块:定义输入输出端口,实现各个模块的连接通过例化

|

//顶层模块 module top( input wire Clk, input wire Rst_n, input wire a, input wire b, output wire c ); wire p_flag;//connect po_flag0 to pi_flag0 wire flag;//connect po_flag to pi_flag //例化 div_clk2 div_clk2m0( .clk(Clk), .rst_n(Rst_n), .po_flag0(p_flag) ); div_clk1 div_clk1m0( .clk(Clk), .rst_n(Rst_n), .pi_flag0(p_flag), .po_flag(flag) ); a_and_b a_and_bm0( . clk(Clk), . rst_n(Rst_n), . pi_flag(flag), . pi_a(a), . pi_b(b), . po_c(c) ); endmodule |

(二)分频模块:两个分频模块实现16分频

|

//分频模块2实现四分频并输出一个分频标志信号 module div_clk2( input wire clk, input wire rst_n, output reg po_flag0 ); wire rst; reg [1:0] div_cnt; assign rst = ~rst_n; //div cnt always @(posedge clk)begin if(rst == 1'b1 )begin div_cnt <= 'd0; end else if (div_cnt == 'd3) begin div_cnt <= 'd0; end else div_cnt <= div_cnt + 1'b1; end //po_flag0 always @(posedge clk) begin if (rst == 1'b1 ) begin po_flag0<= 1'b0; end else if(div_cnt== 'd2)begin po_flag0 <= 1'b1; end else begin po_flag0 <= 1'b0; end end endmodule //分频模块1在分频模块2的基础上,实现16分频并输出对应的分频标志信号 module div_clk1( input wire clk, input wire rst_n, input wire pi_flag0, output reg po_flag ); wire rst; assign rst = ~rst_n; //div_cnt under the pi_flag0 reg [1:0]div_cnt; always@(posedge clk) if(rst) div_cnt<=0; else if(div_cnt==2'd3) div_cnt<=0; else if(pi_flag0) div_cnt<=div_cnt+1'b1; else div_cnt<=div_cnt; //po_flag always@(posedge clk) if(rst) po_flag<=0; else if(div_cnt==2'd3 & pi_flag0)//lack & pi_flag0 is error po_flag<=1'b1; else po_flag<=0; endmodule |

(三)相与模块

|

//相与模块,在16分频的标志信号下,相与 module a_and_b( input wire clk, input wire rst_n, input wire pi_flag, input wire pi_a, input wire pi_b, output reg po_c ); wire rst; assign rst = ~rst_n; always@(posedge clk) if(rst==1'b1) po_c<=1'b0; else if(pi_flag==1'b1) po_c<=pi_a & pi_b; else po_c<=0; endmodule |

三总结

(一)常见疑问及答案

1.在不同模块的信号,通过传输线连在一起,那这些信号会有延时嘛(即变化实际不一样)?

实际上,在不同模块的同一信号如po_flag, pi_flag,flag,他们通过flag信号连在一起,是同时变化的。

2.在什么情况下存在延时?

存在延时一个时钟的会是在时序逻辑的always里,如下面的赋值语句中

|

else if(div_cnt== 'd2)begin po_flag <= 1'b1; po_flag在仿真中,实际为高电平在分频计数值为3. else if (pi_flag == 1'b1) begin po_c <= pi_a & pi_b; end 而在相与模块里,发生相与操作是在po_flag为高后,再延迟一个时钟,故相与在分频计数值为2后,延迟了两个时钟周期, |

3.注意下面这句易出错

else if(div_cnt==2'd3 & pi_flag0)//lack & pi_flag0 is error

po_flag<=1'b1;

若缺少后面的与条件,会持续四个时钟周期,由于div_cnt每四个时钟更新。

(二)设计注意点

1.sublime列编辑:shift+鼠标右键。

2.赛灵思要求为同步复位,故开发板是异步复位,则程序设计为

wire rst;

assign rst = ~rst_n;

3.在例化,模块的接口是输入,可以连接wire或reg型变量。但模块的接口是输出,必须连接wire型。

4.基本语法准则:即always赋值的输出信号,只能为reg型。而assign赋值的输出信号,只能为wire型。

(三)仿真

|

`timescale 1ns/1ns `define clk_period 20 module top_tb(); reg clk; reg rst_n; reg a; reg b; wire c; top top_m0( .Clk(clk), .Rst_n(rst_n), .a(a), .b(b), .c(c) ); initial clk =1; always#(`clk_period/2) clk = ~clk; initial begin rst_n =0; a=0; b=0; #(`clk_period*2); rst_n =1; #(`clk_period*40); rst_n = 0; #(`clk_period*12); $stop; end always#(`clk_period*2) a = {$random}; always#(`clk_period*2) b= {$random}; endmodule //波形:

|

07模块化设计之top_down的更多相关文章

- iOS程序模块化设计

一.模块化设计的概述: 模块化设计(Block-based design):对一定范围内的不同功能或相同功能的不同性能.不同规格的产品进行功能分析的基础上,划分并设计出一系列功能模块,通过模块的选择和 ...

- PHP--进行模块化设计

PHP--进行模块化设计 [来源] 达内 [编辑] 达内 [时间]2012-10-30 导航模块可以简单列为一个关于三级页面链接的HTML文件.通常你可以通过用另一种颜色来标明对当前区域的链 ...

- 深入浅出百度地图API开发系列(3):模块化设计

在前面两张简单介绍了百度地图API的基础知识和使用之后,我们来分析一下百度地图API的基本架构,了解一下基本架构可以帮助我们更清晰的了解API的功能和调用过程,也就可以帮助我们在实际开发中可以更方便的 ...

- AngularJs学习笔记7——四大特性之模块化设计

模块化设计 1.引用自定义模块并调用 自定义模块中,如果有一些服务.封装好笑模块,在另外一个模块中(声明的时候,在依赖列表中加入要引入的模块) var app02 = angular.module(' ...

- C51的模块化设计方法

一个大的单片机程序往往包含很多模块,我是这样组织的: 1.每一个C源文件都要建立一个与之名字一样的H文件(头文件),里面仅仅包括该C文件的函数的声明,其他的什么也不会有,比如变量的定义啊等等不应该有. ...

- thinkphp学习笔记5—模块化设计

原文:thinkphp学习笔记5-模块化设计 1.模块结构 完整的ThinkPHP用用围绕模块/控制器/操作设计,并支持多个入口文件盒多级控制.ThinkPHP默认PATHINFO模式,如下: htt ...

- App 组件化/模块化之路——使用SDK的思路进行模块化设计接口

在不久之前分享一篇<App 组件化/模块化之路——如何封装网络请求框架>文章介绍了我在项目中封装网络请求框架的思路.开发一个 App 会涉及到很多网络请求 API ,例如登录注册接口.用户 ...

- 基于layui的框架模版,采用模块化设计,接口分离,组件化思想

代码地址如下:http://www.demodashi.com/demo/13362.html 1. 准备工作 编辑器vscode,需要安装liveServer插件在前端开启静态服务器 或者使用hbu ...

- Swift之xib模块化设计

一.解决问题 Xib/Storybarod可以方便.可视化的设置约束,在开发中也越来越重要.由于Xib不能组件化,使得封装.重用都变得不可行.本文将介绍一种解决方案,来实现Xib组件化. 二.模型块原 ...

随机推荐

- Solution -「ARC 124E」Pass to Next

\(\mathcal{Description}\) Link. 有 \(n\) 个人站成一个环,初始时第 \(i\) 个人手里有 \(a_i\) 个球.第 \(i\) 个人可以将自己手中任意数 ...

- Solution -「多校联训」取石子游戏

\(\mathcal{Description}\) Link. 有 \(n\) 堆石子,第 \(i\) 堆有 \(x_i\) 个,Alice 每次只能从这堆中拿走 \(a_i\) 个石子,Bo ...

- Linux海王 之 pdsh (并行管理工具)

文章目录 安装 使用 示例 -w 指定主机 -l 指定用户 -g指定用户组 主机列表 交互式界面 pdsh是一个多线程远程shell客户机,它在多个远程主机上并行执行命令 pdsh可以使用几种不同的远 ...

- [LeetCode]1464. 数组中两元素的最大乘积

给你一个整数数组 nums,请你选择数组的两个不同下标 i 和 j,使 (nums[i]-1)*(nums[j]-1) 取得最大值. 请你计算并返回该式的最大值. 示例 1: 输入:nums = [3 ...

- [LeetCode]1480. 一维数组的动态和

给你一个数组 nums .数组「动态和」的计算公式为:runningSum[i] = sum(nums[0]-nums[i]) . 请返回 nums 的动态和. 示例 1: 输入:nums = [1, ...

- Spring5基础

基于Spring 5.2.6 版本. Spring概念 IOC容器 IOC底层原理的演进过程--本质就是为了高内聚,低耦合 在原始方式中,我们通过new创建对象来实现创建对象的逻辑,但是这样做当对象路 ...

- 实践GoF的23种设计模式:SOLID原则(上)

摘要:本文以我们日常开发中经常碰到的一些技术/问题/场景作为切入点,示范如何运用设计模式来完成相关的实现. 本文分享自华为云社区<实践GoF的23种设计模式:SOLID原则(上)>,作者: ...

- [Python]小白入门时遇到的各种问题

Q:关于Python2.X和Python3.X各种版本有什么区别,小白应该选哪个? A: 1.背景及简要介绍 Python 2 发布于 2000 年年底. 随着 Python 2 的不断发展,更多的功 ...

- 企业bi解决方案,商业智能BI作用

随着越来越多的公司将商业智能BI引入到日常运营和商业决策中,BI的热点逐渐起来了.商业智能系统兴起,那BI对企业有什么好处呢? 简单的说,就是可以帮助企业管理者直观清晰的看到自己想要关注的数据,帮助 ...

- C# Task和异步方法

本文主要参考: https://www.cnblogs.com/qtiger/p/13497807.html ThreadPool中有若干数量的线程.当有任务需要处理时,会从线程池中获取一个空闲的线程 ...