FPGA多时钟处理应用

FPGA项目设计中,通常会遇到多时钟处理。即一个PLL输出多个时钟,根据条件选择合适的时钟用作系统时钟。

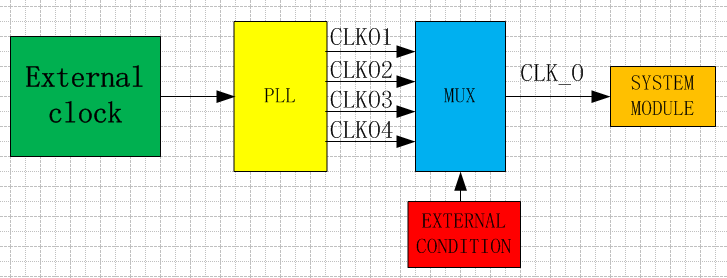

方案一:

外部晶振时钟进入PLL,由PLL输出多个时钟,MUX根据外部条件选择时钟输出做为系统使用。

方案在时钟频率比较低的情况下是可行的。设计时注意MUX使用组合逻辑实现的,注意case语句中default选项必须有输出,否则会出现锁存器。

当输出时钟频率较高时,这种方案的时序约束就比较麻烦。除了使用creat_clock命令约束PLL输入时钟,使用creat_generate_clock约束PLL输出时钟外,还要根据PLL输出的多个时钟之间的关系,使用set_clock_groups约束。set_clock_groups:

- asynchronous表示时钟同时有效,但没有相位关系。

- exclusive 表示时钟是互斥的

- group,group之内的时钟相关,group之间的时钟互不相关。

这种设计使得时钟约束变得繁琐,时序变得紧张。

同时PLL输出时钟后使用MUX进行选择输出,会增加时钟布线延时,高速情况下并不可靠。

时序是设计出来的,不是约束出来的。

设计出好的时序一般不需要约束。

方案二:

在高速情况下,应该更改设计,提高电路速度。ALTERA FPGA提供PLL重配功能。可根据条件对PLL进行重配。

调用ALTERA提供的PLL重配模块,根据官方资料,可以动态的对PLL重新配置。这样PLL输出时钟直接驱动系统模块,将多时钟域转换到单时钟域上。不需要添加附加约束电路都可以正常工作。

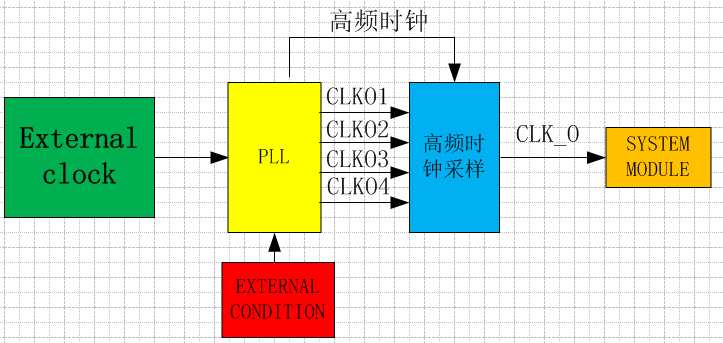

方案三:

第三种方案,这里稍微介绍一下。

PLL输出一个高频时钟HCLK,其他时钟作为HCLK的使能端,用HCLK采样其他时钟,这也是一个可以考虑的方案,这个方案也不会造成多时钟处理及约束。但此方案也有限制,要求HCLK时钟频率至少是PLL输出其他时钟最高频率的两倍以上,这样才能满足采样定理,即奈奎斯特定理。在时钟频率比较低时,亦可以考虑此方案。

文章来源:FPGA极客空间微信公众号

版权所有权归卿萃科技,转载请注明出处。

作者:卿萃科技ALIFPGA

原文地址:bbs.alifpga.com

扫描二维码关注FPGA极客空间。

FPGA多时钟处理应用的更多相关文章

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- FPGA跨时钟域握手信号的结构

FPGA跨时钟数据传输,是我们经常遇到的问题的,下面给出一种跨时钟握手操作的电路结构.先上图 先对与其他人的结构,这个结构最大的特点是使用 req 从低到高或者高到低的变化 来表示DIN数据有效并开始 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- FPGA 异步时钟处理方

1 假设FPGA设计,包括不同的频率的时钟,它会发出涉及异步时钟. 我们需要一些方法来使时钟同步,从而保证FPGA可靠性设计. 2 在建立和保持时间所构成的有效时间窗体内,数据输入到触发器进行转换. ...

- FPGA跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- 对FPGA的时钟资源理解(更新中)

7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟.内部时钟进行处理,生成需要的低抖动时钟.PLL是MMCM的功能子集, ...

随机推荐

- ios和android的发展前景比较

详见:http://blog.yemou.net/article/query/info/tytfjhfascvhzxcyt164 一直都有很多人在讨论未来的IOS和android市场哪个前景更好,现在 ...

- (一)Builder(建造者)模式

我们一般在构建javabean的对象的时候通常有三种写法: 1.直接通过构造函数传参的方式设置属性,这种方法如果属性过多的话会让构造函数十分臃肿,而且不能灵活的选择只设置某些参数. 2.采用重叠构造区 ...

- html5中的video标签和audio标签

不管是否承认,flash早已不像过往那样如日中天了.亚马逊全面放弃flash.苹果放弃flash.安卓也放弃了移动端的flash支持.事实上flash已经不太适合web开发了,因为HTML5中的vid ...

- Beta冲刺前准备

一.介绍小组新成员,Ta担任的角色. 201421123121 栗海辉 来自Sugar Free 风格:低调中的高调,给你不一样的视觉 擅长的技术:C语言/JAVA 在曾经的团队里面担任主要编程人员, ...

- 201521123055 《Java程序设计》第7周学习总结

1. 本章学习总结 2. 书面作业 1.ArrayList代码分析 1.1 解释ArrayList的contains源代码 1.2 解释E remove(int index)源代码 1.3 结合1.1 ...

- 201521123029《Java程序设计》第四周学习总结

1. 本周学习总结 1.1 尝试使用思维导图总结有关继承的知识点. 1.2 使用常规方法总结其他上课内容. 答:1. 多态性,多态性是相同的形态,不同的行为(定义),其中父类类型变量可以引用子类对象. ...

- 201521123077 《Java程序设计》第3周学习总结

1. 本周学习总结 2. 书面作业 Q1.代码阅读 public class Test1 { private int i = 1;//这行不能修改 private static int j = 2; ...

- 201521123030《Java程序设计》 第2周学习总结

本周学习总结 String常量,创建之后不能再进行修改 使用+连接字符串会产生新字符串,要大量使用重复性连接应用StringBuilder,检测字符串相等应用equal方法. 枚举类型变量的取值在一个 ...

- 201521123047《Java程序设计》第1周学习总结

1. 本章学习总结 学习到了jdk,jvm,jre之间的关系,下载并安装了jdk,学会设置path变量,初步学会建立简单的java程序,并执行成功.初步学会notepad++,eclipse的操作.学 ...

- 201521123064 《Java程序设计》第12周学习总结

本次作业参考文件 正则表达式参考资料 1. 本章学习总结 1.1 以你喜欢的方式(思维导图或其他)归纳总结多流与文件相关内容. ① 标准输入输出流(字节流):标准输入流 System.in,标准输出流 ...