SDRAM

环境:STM32F769discovery板

SDRAM芯片:用的MT48LC4M32B2B5-6A 16Mbyte (sdram和flash一般标的容量都是bit)

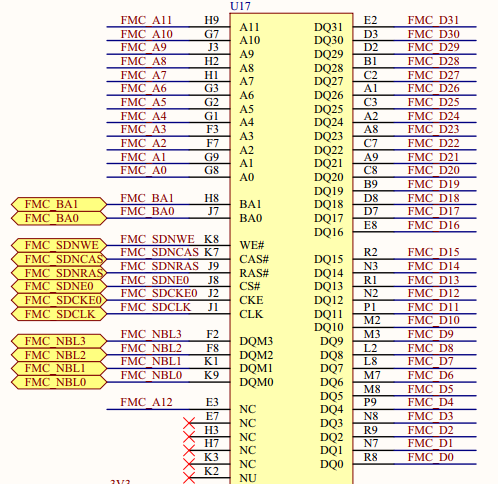

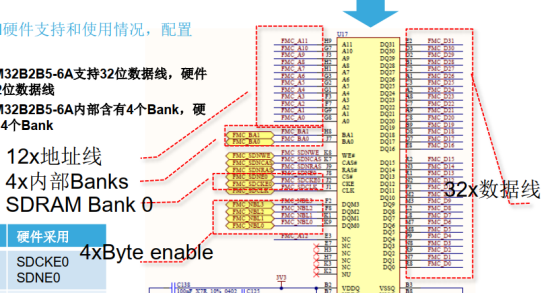

硬件图:

第一步 配置FMC控制器:

由硬件图可以看出 时钟芯片使能SDRAM BANK0 且MT48LC4M32B2B5-6A有4块BANK(一般的SDRAM都有4块),地址线和数据线可由硬件图确定。

sdram有两种刷新操作:自动刷新( Auto Refresh)和自我刷新( Self Refresh),在发送 Refresh命令时,如果 CKE 有效(高电平),则使用自动刷新模式,否则使用自我刷新模式。

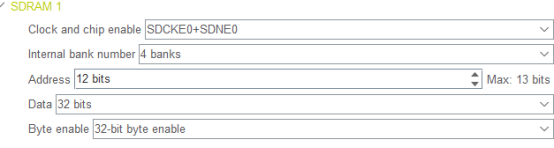

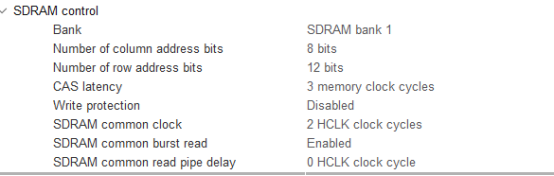

第二步 配置FMC参数

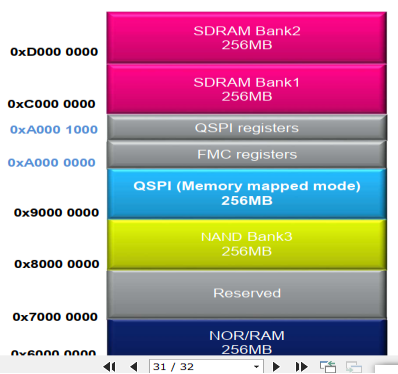

@Param1: FMC可以同时控制两个SDRAM ,如下图所示,本次实验用的SDRAM 1,地址为0xc0000000

@Param2:列地址线 column 28 = 256 此处为8

@Param3:行地址线 row 可由datasheet中的参数确认:212 = 4k 此处为12

@Param4:column address select latency 列地址选择延时 即在发送激活命令后,会将行地址一起发送过去,当发送read命令后,会将列地址一起发送过去,CL就是发送过列地址后,QD数据线上的数据在延时多少周期后有效:SDRAM时钟可由SDRAM common clock二分频或者三分频,为保证速度,我们HCLK/2 = 108MHZ 即一个时钟周期9.26ns

由上图可知:CL为18ns等于2个时钟周期,但是考虑冗余设计,此处选择3个时钟周期

@Param5:默认关闭写保护

@Param6:对HCLK分频,支持2分频或者三分频

@Param7:突发读使能:如果要连续读/写就还要对当前存储单元的下一个单元进行寻址,也就是要不断的发送列地址与读/写命令(行地址不变,所以不用再对行寻址)只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。 这样,除了第一个数据的传输需要若干个周期外,其后每个数据只需一个周期的即可获得。在SDRAM的初始化队列函数中设置

@Param8:这两个位可定义在 CAS 延迟后延后多少个 HCLK 时钟周期读取数据( 00~10,表示 0~2 )。 这里,我们设置为 00 即可。

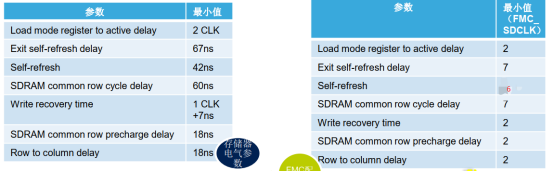

第三步 SDRAM时序参数

以下所有时序参数均可在datasheet中计算可得

@Param1:加载模式寄存器到激活状态延时

@Param2:退出自我刷新模式延时:

由第二步可知,一个时钟周期为9.26ns,此处为70ns一共7个时钟周期

@Param3:自我刷新周期

第一个为商业工业级64ms(6个时钟周期)刷新一次 第二个为汽车级16ms;我们使用64ms

@Param4:行循环延时

注意,发送行地址的时候为激活命令,此处的名称为激活命令到激活命令7个时钟周期

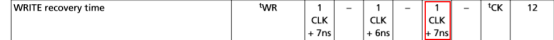

@Param5:写恢复时间

如图为两个时钟周期

@Param6:SDRAM行预充电延时

如图为两个时钟周期

@Param7:行到列延时

第四步 SDRAM初始化序列

第一步:上电并且时钟使能

/* Step 1: Configure a clock configuration enable command */

Command.CommandMode = FMC_SDRAM_CMD_CLK_ENABLE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK1;

Command.AutoRefreshNumber = ; //发送一次

Command.ModeRegisterDefinition = ;

/* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

第二步:上电后至少等待200us才能发送其他命令,Hal库提供的最小延时为1ms所以

/* Step 2: Insert 100 us minimum delay */

/* Inserted delay is equal to 1 ms due to systick time base unit (ms) */

HAL_Delay();

第三步:发送预充电命令

/* Step 3: Configure a PALL (precharge all) command */

Command.CommandMode = FMC_SDRAM_CMD_PALL;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK1;

Command.AutoRefreshNumber = ; //发送一次

Command.ModeRegisterDefinition = ; /* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

第四步:发送自动刷新命令 /* Step 4: Configure an Auto Refresh command */

Command.CommandMode = FMC_SDRAM_CMD_AUTOREFRESH_MODE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK1;

Command.AutoRefreshNumber = ; //至少发送8次自刷新命令

Command.ModeRegisterDefinition = ; /* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT); 第五步:发送SDRAM模式寄存器参数

/* Step 5: Program the external memory mode register */

tmpmrd = (uint32_t)SDRAM_MODEREG_BURST_LENGTH_1 |\

SDRAM_MODEREG_BURST_TYPE_SEQUENTIAL |\

SDRAM_MODEREG_CAS_LATENCY_3 |\

SDRAM_MODEREG_OPERATING_MODE_STANDARD |\

SDRAM_MODEREG_WRITEBURST_MODE_SINGLE; Command.CommandMode = FMC_SDRAM_CMD_LOAD_MODE;

Command.CommandTarget = FMC_SDRAM_CMD_TARGET_BANK1;

Command.AutoRefreshNumber =;

Command.ModeRegisterDefinition = tmpmrd; //SDRAM寄存器内容 /* Send the command */

HAL_SDRAM_SendCommand(&hsdram1, &Command, SDRAM_TIMEOUT);

第六步:设置自刷新率值

/* Step 6: Set the refresh rate counter */

/* Set the device refresh rate */

HAL_SDRAM_ProgramRefreshRate(&hsdram1, RefreshCount);

RefreshCount计算:

COUNT = (SDRAM刷新周期/行数)/SDRAM时钟周期

64ms / / .26ns +(考虑冗余) .26ns为(HCLK/)

SDRAM的更多相关文章

- 【iCore3 双核心板_FPGA】实验二十八:基于SDRAM 的VGA 驱动器的设计

本实验设计的VGA显示驱动完全基于FPGA实现,用SDRAM做缓存设备,通过ARM控制VGA显示的内容.ARM 通过FSMC总线向FPGA发送数据,由于总线的速度和VGA的显示速度与SDRAM的读写速 ...

- (三)内存 SDRAM 驱动实验 (杨铸 130 页)(勉强能懂个大概)

SDRAM 芯片讲解: 地址: 行地址 (A0-A12) 列地址 (A0-A8) 片选信号(BA0 BA1)(L-BANK)(因为SDRAM有 4片) 两片SDRAM 连线唯一区别在 UDQM ...

- SDRAM控制器的Verilog建模之一

前言:作为经典存储器的三剑客中的flash和sram已经建模测试过了,虽然现在都已经ddr2,ddr3,667MHZ.1333MHZ的天下了,但是接下这周来准备写一下sdram的controller. ...

- SDRAM的主要参数

(1) 容量.SDRAM的容量经常用XX存储单元×X体×每个存储单元的位数来表示.例如某SDRAM芯片的容量为4M×4×8bit,表明该存储器芯片的容量为16 M字节.或128 M bit. (2) ...

- SDRAM,DRAM,SRAM,DDR的概念

一:SDRAM SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输 ...

- RAM,SRAM,DRAM,SDRAM,DDR RAM,ROM,PROM,EPROM,EEPROM,NAND FLASH,NOR FLASH的区别

RAM:由字面意思就可以理解,SDRAM SRAM DRAM(下面蓝色字体的这几种)都可以统称RAM,random access memory(随机存取存储器)的缩写,下面是51hei.com为大家整 ...

- 调试2440 RAM拷贝至SDRAM遇到的问题

汇编代码主要是初始化一些寄存器,关狗,初始化时钟,初始化存储管理器以便访问内存,然后将SoC上4k RAM数据拷贝至SDRAM,然后在SRAM里面运行,由于代码未正常跑起来,于是使用JLinkExe来 ...

- ARM学习篇 SDRAM理解

1.SDRAM单管存储单元 SDRAM单管电路图 C记忆单元 T控制门管 Z字线 W位线 注:图示为N沟道耗尽型MOS管 写入:Z加高电平,MOS导通,W状态决定了电容C的状态 读出:Z加高电平,MO ...

- SDRAM和dcfifo的联合

SDRAM和dcfifo的联合 设计原理 在"SDRAM突发读写页"实验中,留下了一个问题,就是从SDRAM读取数据的速度要与SDRAM的驱动时钟同步,这就造成了读出的数据的速率过 ...

- SDRAM读写一字(下)

SDRAM读写一字 SDRAM控制模块 上电后进行初始化状态,初始化完成后进入空闲状态,在此进行判断如下判断: 如果自刷新时间到,则进行自刷新操作,操作完成后重新进入空闲状态: 如果读使能有效则进行读 ...

随机推荐

- Spring 7大模块的解说

先看以下Spring的组成图: 7大模块包括:core.AOP.ORM.DAO.WEB.Context.WebMvc. 1:core:spring的容器,主要组成是BeanFactury.也是Spri ...

- Linux下Eclipse以及Java环境安装教程[小白化](2019-9)

Linux下安装Eclipse以及Java 一.前言 许久未用Eclipse, Ubuntu上也没装Eclipse, 今天安装发现, 好多东西都忘了. 不过经过一番查找(百度, csdn) 终于还是安 ...

- Mybatis值ResultMap的使用详解

Mybatis的定义 MyBatis 是一款优秀的持久层框架,它支持定制化 SQL.存储过程以及高级映射.MyBatis 避免了几乎所有的 JDBC 代码和手动设置参数以及获取结果集.MyBatis ...

- CentOS7 自定义登录前后欢迎信息

博客地址:http://www.moonxy.com 一.摘要 本人当前使用的是阿里云 ECS 服务器,操作系统为 linux,发行版为 CentOS 7.4.1708.系统默认都已经提供了欢迎信息, ...

- Java连载35-类总结、空指针异常

一.总结 1.栈内存中主要存储的是方法体中的局部变量 2.对象内部有实例变量,实例变量存储在堆内存中 3.变量分类:局部变量(方法体中声明):成员变量(方法体外声明) 实例变量(前边修饰符没有stat ...

- Dungeon Master POJ-2251 三维BFS

题目链接:http://poj.org/problem?id=2251 题目大意 你被困在了一个三维的迷宫,找出能通往出口的最短时间.如果走不到出口,输出被困. 思路 由于要找最短路径,其实就是BFS ...

- GStreamer基础教程08 - 多线程

摘要 GStreamer框架会自动处理多线程的逻辑,但在某些情况下,我们仍然需要根据实际的情况自己将部分Pipeline在单独的线程中执行,本文将介绍如何处理这种情况. GStreamer多线程 GS ...

- 博客的第一天:回顾半年前的基础:SQL--基础查询+年月日格式+拼接

----------------------2019/6月份 <<必知必会>>书本练习-实践练习--------------------------- ---order by没 ...

- [Abp vNext 源码分析] - 9. 接口参数的验证

一.简要说明 ABP vNext 当中的审计模块早在 依赖注入与拦截器一文中有所提及,但没有详细的对其进行分析. 审计模块是 ABP vNext 框架的一个基本组件,它能够提供一些实用日志记录.不过这 ...

- WebGL简易教程(八):三维场景交互

目录 1. 概述 2. 实例 2.1. 重绘刷新 2.2. 鼠标事件调整参数 3. 结果 4. 参考 1. 概述 在上一篇教程<WebGL简易教程(七):绘制一个矩形体>中,通过一个绘制矩 ...