FPGA学习笔记. DDS

DDS原理

直接数字式频率合成器(Direct Digital Synthesizer)

频率计算公式

Fout = FW * Fclk / 2^N

Fout 输出频率, Fw 频率控制字, N 位数 精度 Fclk / 2^N

设计思路

设置一个计数cnt作累加,Fw频率控制字,作为计数步长。

时钟clk下,cnt <= cnt + Fw.

设输入时钟是100mHz,目标Fo为115200Hz,计数器为32位,据上面的公式可以得出

Fw = Fo * 2^32 / Fc = 115200 * 2^32 / (100*10^6) = 4947802.3249992

取整 Fw = 4947802,

占空比为50%,cnt <= 2^N ,Fo = 0 ; cnt > 2^N ,Fo = 1。

添加一个block menery IP,存放 正弦波相位-幅度 表,由相位累加来查询地址。

生成COE文件

位宽32bit 深度2^12,code

clear;

close all;

%%

width = ; %data width

N = ; %addr witdh

depth = ^N;%memery depth

x = linspace(,*pi,depth);

y_sin = sin(x)+;

y_sin_q=round(y_sin*(^(width-)));

fid = fopen('CosWaveWid32Def2e12.coe','w');

%write header

fprintf(fid,'MEMORY_INITIALIZATION_RADIX=16;\n');

fprintf(fid,'MEMORY_INITIALIZATION_VECTOR=\n');

%write data

if(fid>)

fprintf(fid,'%x,\n',y_sin_q);

end

fclose(fid);

verilog 程序

累加与查询地址

/*

fc = 100MHz

fo = 1kHz

N = 32 (width)

fw = (fo * 2^N) / fc = 42949.67296 => 42950 */

module DdsTopV

#(

parameter COUNTWIDTH = ,

parameter FW = 'd429497

)

(

input wire clk,

input wire rst_n,

output reg clk_out,

// output wire [11:0] addr,

output wire [:] phase,

output wire [:] sin_o

); //wire [31:0] phase;

wire [:] addr;

reg [COUNTWIDTH-:] cnt; //相位累加

always @(posedge clk or posedge rst_n)

begin

if(!rst_n)

cnt <= ;

else

cnt <= cnt + FW; //计数器步长FW

end

//clk_out

always @(posedge clk or posedge rst_n)

begin

if(!rst_n)

clk_out <= 'b0;

else if(cnt < 'h7FFF_FFFF)

clk_out <= 'b0;

else

clk_out <= 'b1;

end assign phase = cnt;

assign addr = {phase[:]}; blk_mem_gen_0 blk_mem_gen_0(

.clka(clk),

.addra(addr),

.douta(sin_o)

); endmodule

TestBench

module testbench(); reg clk;

reg rst_n;

wire clk_out;

//wire [11:0] addr;

wire [:] phase;

wire [:] sin_o; /*

Fo = 115200Hz

Fw = 4947802.3

*/

DdsTopV

#(

// .COUNTWIDTH(32'd32),

.FW('d4947802)

)

uut

(

.clk(clk),

.rst_n(rst_n),

.phase (phase),

// .addr(addr),

.clk_out(clk_out),

.sin_o(sin_o)

); initial begin

clk = ;

rst_n = ;

# rst_n=;

end always # clk=~clk; endmodule

设置Block Memery

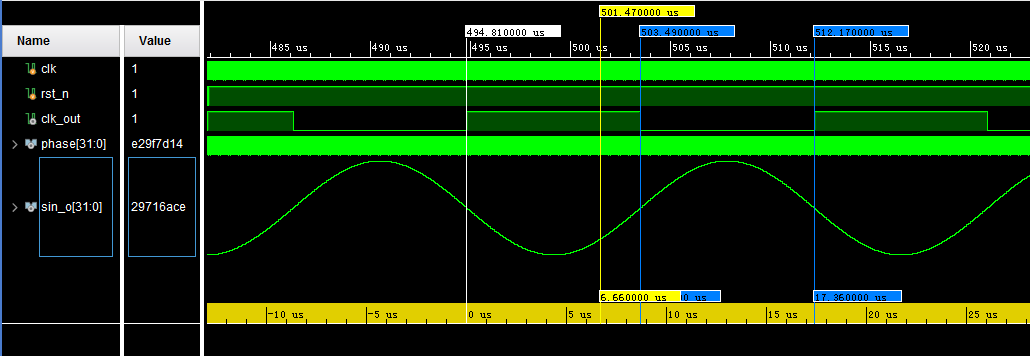

仿真结果

via

https://www.cnblogs.com/christsong/p/5536995.html

FPGA学习笔记. DDS的更多相关文章

- FPGA学习笔记(二)——FPGA学习路线及开发流程

###### [该随笔部分内容转载自小梅哥] ######### 一.FPGA学习路线 工具使用 -> 语法学习 -> 逻辑设计 -> IP使用 ->接口设计 -& ...

- FPGA学习笔记(三)—— 数字逻辑设计基础(抽象的艺术)

FPGA设计的是数字逻辑,在开始用HDL设计之前,需要先了解一下基本的数字逻辑设计-- 一门抽象的艺术. 现实世界是一个模拟的世界,有很多模拟量,比如温度,声音······都是模拟信号,通过对模拟信号 ...

- FPGA学习笔记(一)——初识FPGA

###### [该随笔部分内容转载自小梅哥] ######### FPGA(Field-Programmable Gate Array,现场可编程门阵列),正如其名,FPGA内部有大量的可 ...

- FPGA学习笔记(七)——FSM(Finite State Machine,有限状态机)设计

FPGA设计中,最重要的设计思想就是状态机的设计思想!状态机的本质就是对具有逻辑顺序和时序规律的事件的一种描述方法,它有三个要素:状态.输入.输出:状态也叫做状态变量(比如可以用电机的不同转速作为状态 ...

- Xilinx FPGA 学习笔记

一.时序设计 方法1.通过状态机来实现,通过verilog控制FPGA,让它该快的时候快,该慢的时候慢. 方法2.FPGA中运行CPU 把逻辑控制顺序复杂的事情用C代码来实现,而实时处理部分用veri ...

- FPGA学习笔记之Altera FPGA使用JIC文件配置固化教程(转)

很多做过单片机的朋友都知 道,我们在对MCU烧写完程序固件后,那么该程序固件就存储在了该MCU内部.即使MCU断电了再重新上电,程序也能继续运行.这是因为对MCU烧写固件 的实质就是将程序固件写入到M ...

- FPGA学习笔记(八)—— 状态机设计实例之独立按键消抖

###### [该随笔中部分内容转载自小梅哥] ######### 独立按键消抖自古以来在单片机和FPGA中都是个不可避免的问题,首先,解释一下什么叫做按键抖动,如图,按键在按下和松开的那个瞬间存在大 ...

- FPGA学习笔记(六)—— 时序逻辑电路设计

用always@(posedge clk)描述 时序逻辑电路的基础——计数器(在每个时钟的上升沿递增1) 例1.四位计数器(同步使能.异步复位) // Module Name: coun ...

- FPGA学习笔记之按键控制

参考: [黑金原创教程][FPGA那些事儿-驱动篇I ]实验二:按键模块① - 消抖 源码如下: key_funcmod.v module key_funcmod(clk, rst, key, led ...

随机推荐

- beta4

吴晓晖(组长) 过去两天完成了哪些任务 昨天FloatingActionButton和权限获取调整 今天复习,没写东西,晚点有空了写 展示GitHub当日代码/文档签入记录 接下来的计划 推荐算法 还 ...

- C#简述(二)

详情请参考:http://www.runoob.com/csharp/csharp-operators.html 1.C# 运算符 算术运算符 关系运算符 逻辑运算符 位运算符 赋值运算符 其他运算符 ...

- 软件工程作业 - Week 1

构建之法读后疑问: 初步的完成构建程序设计思路之后实现过程中发现了问题或者可以优化的地方是立马就改进还是完成之后按照步骤统一进行优化. 覆盖性测试,针对一些永远用不到只是用来预防极为极端的情况下,例如 ...

- Semantic Versioning Specification & 语义化版本

Semantic Versioning Specification & 语义化版本 Semantic Versioning Specification http://semver.org 16 ...

- Vue---从后台获取数据vue-resource的使用方法

作为前端人员,在开发过程中,我们大多数情况都需要从后台请求数据,那么在vue中怎样从后台获取数据呢?接下来,我简单介绍一下vue-resource的使用方法,希望对大家有帮助. 一.下载vue-res ...

- CF1025D Recovering BST

题意:给定序列,问能否将其构成一颗BST,使得所有gcd(x, fa[x]) > 1 解:看起来是区间DP但是普通的f[l][r]表示不了根,f[l][r][root]又是n4的会超时,怎么办? ...

- 洛谷P2480 古代猪文

这道题把我坑了好久...... 原因竟是CRT忘了取正数! 题意:求 指数太大了,首先用欧拉定理取模. 由于模数是质数所以不用加上phi(p) 然后发现phi(p)过大,不能lucas,但是它是个sq ...

- springboot配置文件的配置

转:https://www.cnblogs.com/zheting/p/6707036.html Spring Boot使用了一个全局的配置文件application.properties,放在src ...

- python中的无参装饰器和有参装饰器

python中的无参装饰器和有参装饰器 作者:尹正杰 版权声明:原创作品,谢绝转载!否则将追究法律责任. 装饰器特点: 1>.开放封闭原则,即对扩展是开放的,对修改时封闭的: 2>.装饰器 ...

- PAM认证机制详情

PAM(Pluggable Authentication Modules)认证机制详情 作者:尹正杰 版权声明:原创作品,谢绝转载!否则将追究法律责任. 一.介绍PAM PAM(Plugga ...