STM32F4 Timer Internal Trigger Connection

The Timers can be cascaded to make more complex timing relationships, or longer periods.

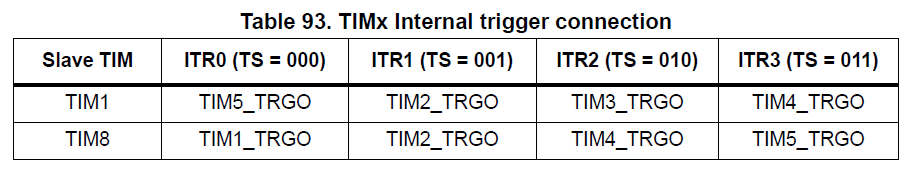

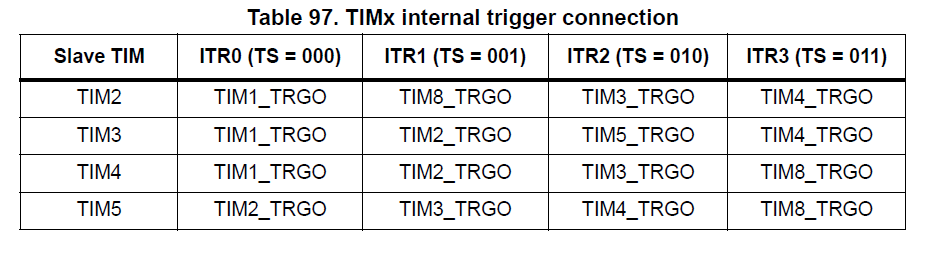

Internally only some timers can trigger others.

This is a Master/Slave relationship and is handled by the SMS register.

For example, you can see below that TIM8 can be triggerd by TIM1.

- Uses TRGI to map.

- One Timer can be used as the prescaler for another.

- The first timer update_event, or output_compare signal is used as clock for the second.

- The counter mode sets whether the update_event occurs on overflow and/or underflow of the Timer

- Counter mode is set using the TIMx_CR1 reg and CMS bits as indicated in the example below.

Example for internal trigger

Internal trigger clock mode 1 (ITRx)

TIM_CLK is replaced by ITRx_CLK which is the internal trigger freq mapped to timer Trigger input TRGI.

The counter mode indicates if the update_event is generated:

- on overflow - if mode = up counting, the DIR bit is reset in TIMx_CR1

- on underlfow - if mode = down counting, the DIR bit is set in TIMx_CR1

- both - if mode is center aligned, the CMS bits are non zero

The update_event is also generated by:

- software if the UG bit (Update Generation) is set in TIM_EGR reg.

- update generation through the slave mode controller

refer to Timer app note: DM00042534.pdf

Timer synchronisation

A Master can control a slave Timer using a Trigger TRGO.

A Timer is slaved if its ITRx is connected to a Slave and the Master is set to use TRGO

Trigger outputs from the Master can be selected from:

- Reset:

- UG bit from EGR reg is used as TRGO

- Enable:

- Counter enable is used as TRGO.

- Used to start several timers at the same time or control window for Slave start

- Update:

- the update_event is TRGO.

- e.g. a master timer can act as a prescaler for a slave timer.

- Compare pulse:

- as soon as a capure or match occurs TRGO goes high when CC1IF flag is to be set

- OC1REF: use OC1REF as TRGO

- OC2REF: use OC2REF as TRGO

- OC3REF: use OC3REF as TRGO

- OC4REF: use OC4REF as TRGO

Master mode:

- Configure the Timer

- Select Trigger output to be used

- in CR2 reg - set MSM bits

- Enable Master/slave mode

- in SMCR reg - enable MSM bit

/*

* Trigger select mapping for slave timer from master timer. This is

* unfortunately not very straightforward; there's no tidy way to do this

* algorithmically. To avoid burning memory for a lookup table, use macros to

* compute the offset. This also has the benefit that compilation will fail if

* an unsupported master/slave pairing is used.

*

* Slave Master

* 1 15 2 3 4 (STM32F100 only)

* 2 9 10 3 4

* 3 9 2 11 4

* 4 10 2 3 9

* 9 2 3 10 11 (STM32L15x only)

* --------------------

* ts = 0 1 2 3

*/

#define STM32_TIM_TS_SLAVE_1_MASTER_15 0

#define STM32_TIM_TS_SLAVE_1_MASTER_2 1

#define STM32_TIM_TS_SLAVE_1_MASTER_3 2

#define STM32_TIM_TS_SLAVE_1_MASTER_4 3

#define STM32_TIM_TS_SLAVE_2_MASTER_9 0

#define STM32_TIM_TS_SLAVE_2_MASTER_10 1

#define STM32_TIM_TS_SLAVE_2_MASTER_3 2

#define STM32_TIM_TS_SLAVE_2_MASTER_4 3

#define STM32_TIM_TS_SLAVE_3_MASTER_9 0

#define STM32_TIM_TS_SLAVE_3_MASTER_2 1

#define STM32_TIM_TS_SLAVE_3_MASTER_11 2

#define STM32_TIM_TS_SLAVE_3_MASTER_4 3

#define STM32_TIM_TS_SLAVE_4_MASTER_10 0

#define STM32_TIM_TS_SLAVE_4_MASTER_2 1

#define STM32_TIM_TS_SLAVE_4_MASTER_3 2

#define STM32_TIM_TS_SLAVE_4_MASTER_9 3

#define STM32_TIM_TS_SLAVE_9_MASTER_2 0

#define STM32_TIM_TS_SLAVE_9_MASTER_3 1

#define STM32_TIM_TS_SLAVE_9_MASTER_10 2

#define STM32_TIM_TS_SLAVE_9_MASTER_11 3

STM32F4 Timer Internal Trigger Connection的更多相关文章

- Stop logging "internal dummy connection" in Apache

Apache 2.x keeps child processes alive by creating internal connections which appear in the log file ...

- 解决Apache日志"internal dummy connection"方法

最近查看服务器中apache日志,发现有大量的 OPTIONS * HTTP/1.0" 200 - "-" "Apache (internal dummy co ...

- STM32F4 Timer simplified block diagram

Timers TIM1 and TIM8 use 16-bit counters and are the most complex timers of all timers included in t ...

- (STM32F4) Timer Compare mode 操作

Timer 比較模式(compare) 具體會用在哪種狀況目前還沒有這種經驗,但Compare有配置功能pin想必有應用會用到這個模式 從Function Block來看比較模式比基本Timer多了比 ...

- (STM32F4) Timer 基本操作

Timer (計時器) 就是慢慢數時間,在timer內部有一個計數器. 而計數器會數到Register的value當數值數到設定值Timer就會發起IRQ 而程式就會轉跳到中斷向量裡頭去執行想要做的事 ...

- STM32F4 Timer External Clock TI2 Both Edges Demo

#define CLK_FREQ ( 10000 ) #define CORE_FREQ ( 168000000 ) static void TIM_GPIO_Config( void ) { GPI ...

- STM32 System and Timer Clock Configurations

STM32 System and Timer Clock Configurations I've started writing some software to drive a series of ...

- STM32 Timer Clock sources -- External Clock Both Edge

Timers get their clock source from External pins or Internal timer sources. External External = pins ...

- Advanced Replication同步复制实验(基于Trigger&基于Materialized View)

1. 高级复制和流复制介绍 1.1 高级复制(Advanced Replication) 高级复制也称为对称复制,分为多主体站点复制(Multiple Master Rplication).物化视图站 ...

随机推荐

- not compiled to use: SSE4.1 SSE4.2 AVX AVX2 FMA

Your CPU supports instructions that this TensorFlow binary was not compiled to use: SSE4.1 SSE4.2 AV ...

- 【转载】chmod命令详解

查看linux文件的权限:ls -l 文件名称 查看linux文件夹的权限:ls -ld 文件夹名称(所在目录) 修改文件及文件夹权限: sudo chmod -(代表类型)×××(所有者)×××(组 ...

- 记录自己对EventLoop和性能问题处理的一点心得【转】

转自:http://www.cnblogs.com/lanyuliuyun/p/4483384.html 1.EventLoop 这里说的EventLoop不是指某一个具体的库或是框架,而是指一种程序 ...

- arm GIC介绍之四【转】

转自:https://blog.csdn.net/sunsissy/article/details/73882718 GIC是ARM体系中重要的组件,在认识到GIC的组成和功能之后,了解到IRQ的大致 ...

- APP的CPU,内存,耗电,流量测试工具

APP的CPU,内存,耗电,流量测试工具下载地址,后续文章会介绍如何使用Emmagee.itest.gt APP应用的CPU,内存,耗电,流量调查 可和同类产品比较,使用GT等工具:CPU靠syste ...

- php毫秒时间戳

2014年5月23日 17:46:04 凡事还是得靠自己呀,网上太多坑 如果你的机器是 32位 的可以看这个: list($usec, $sec) = explode(' ', microtime() ...

- 字符串格式化格式 -- Numeric Format Strings

- 洛谷P3379倍增LCA

传送门 #include <iostream> #include <cstdio> #include <cstring> #include <cmath> ...

- java 异常历史 和观点

异常起源于PL/1和Mesa之类的系统中. 1.) 不在于编译器是否会强制程序员去处理错误,而是要由一致的,使用异常来报告错误 2.) 不在于什么时候进行检查,而是一定要有检查.

- ruby on rails在fedora18上install

ruby on rails 在fedora18下的安装 天朝的网络原因,安装不是很顺畅,所以把过程记录下备用 前面下载rubygem什么的都比较快,新建一个project的时候会出问题 gem new ...