JTAG TAP Controller

The TAP controller is a synchronous finite state machine that responds

to changes at the TMS and TCK signals of the TAP and controls the sequence of operations of the circuitry.

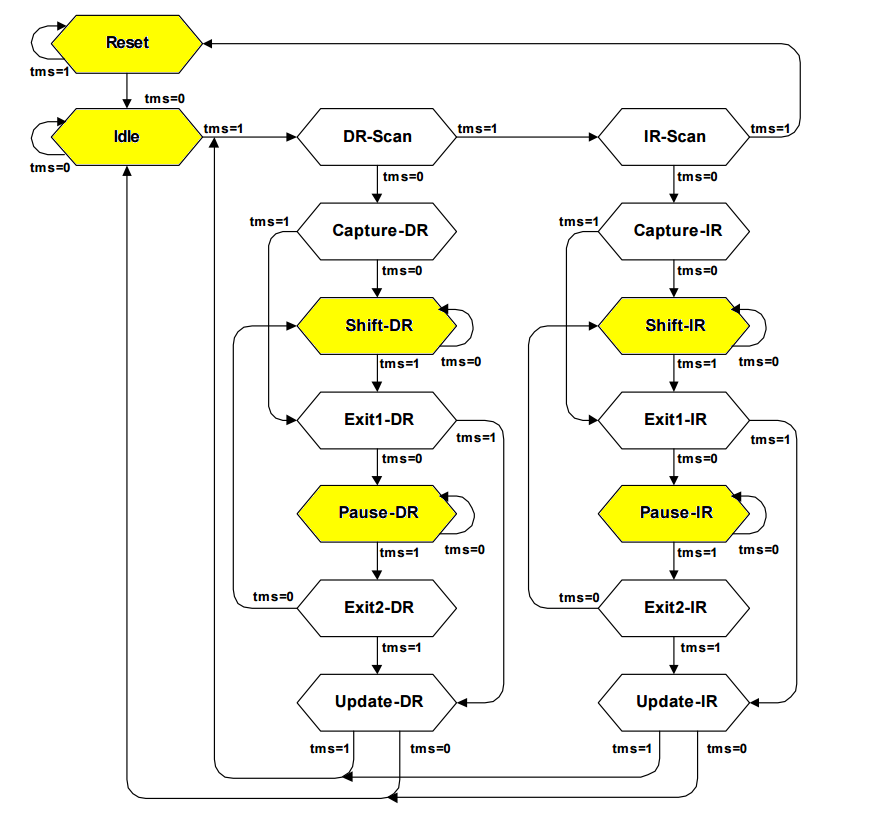

TAP controller state diagram

*黄*色*状态可以重复,其他状态只能出现一次,下个TCK上升沿会切换到下一个状态。

State descriptions

Reset

The test logic is disabled so that normal operation of the chip logic can continue unhindered.

No matter in which state the TAP controller currently is, it can change into Reset state if TMS is high for at least 5 clock cycles.

As long as TMS is high, the TAP controller remains in Reset state.

Idle

Idle is a TAP controller state between scan (DR or IR) operations.

Once entered, this state remains active as long as TMS is low.

DR-Scan

Temporary controller state. If TMS remains low, a scan sequence for the selected data registers is initiated.

IR-Scan

Temporary controller state. If TMS remains low, a scan sequence for the instruction register is initiated.

Capture-DR

Data may be loaded in parallel to the selected test data registers.

Shift-DR

The test data register connected between TDI and TDO shifts data one stage towards the serial output with each clock.

Exit1-DR

Temporary controller state.

Pause-DR

The shifting of the test data register between TDI and TDO is temporarily halted.

Exit2-DR

Temporary controller state.

Allows to either go back into Shift-DR state or go on to Update-DR.

Update-DR

Data contained in the currently selected data register is loaded into a latched parallel output (for registers that have such a latch).

The parallel latch prevents changes at the parallel output of these registers from occurring during the shifting process.

Capture-IR

Instructions may be loaded in parallel into the instruction register.

Shift-IR

The instruction register shifts the values in the instruction register towards TDO with each clock.

Exit1-IR

Temporary controller state.

Pause-IR

Wait state that temporarily halts the instruction shifting.

Exit2-IR

Temporary controller state. Allows to either go back into Shift-IR state or go on to Update-IR.

Update-IR

The values contained in the instruction register are loaded into a latched parallel output from the shift-register path.

Once latched, this new instruction becomes the current one.

The parallel latch prevents changes at the parallel output of the instruction register from occurring during the shifting process.

JTAG TAP Controller的更多相关文章

- JTAG - General description of the TAP Controller states

A transition between the states only occurs on the rising edge of TCK, and each state has a differen ...

- JTAG Simplified

JTAG Simplified So the other day, I explored the JTAG bus interface which is frequently found in CPL ...

- JTAG

JTAG是JOINT TEST ACTION GROUP的简称,JTAG的两个标准IEEE 1149.1(2001)和IEEE 1149.7(2009). JTAG中主要包含两部分内容:TAP(TES ...

- JTAG 引脚自动识别 JTAG Finder, JTAG Pinout Tool, JTAG Pin Finder, JTAG pinout detector, JTAGULATOR, Easy-JTAG, JTAG Enumeration

JTAG Finder Figuring out the JTAG Pinouts on a Device is usually the most time-consuming and frustra ...

- ARM JTAG 调试原理

ARM JTAG 调试原理 JTAG的接口是一种特殊的4/5个接脚接口连到芯片上 ,所以在电路版上的很多芯片可以将他们的JTAG接脚 通过Daisy Chain的方式连在一起,并且Probe只需连接到 ...

- JTAG Communications model

https://en.wikipedia.org/wiki/Joint_Test_Action_Group In JTAG, devices expose one or more test acces ...

- ARM JTAG 信号 RTCK 应该如何处理?

用户在调试内嵌可综合内核的 CPU 如 ARM7TDMI-S 时,需要通过打开仿真器的自适应时钟功能. 此时,ARM仿真器根据 RTCK 时钟信号的频率,产生可用于 CPU 内核当前时钟主频的最快的 ...

- Training JTAG Interface

For most embedded CPU architecture implementations, the JTAG port is used by the debugger to interfa ...

- JTAG – A technical overview and Timing

This document provides you with interesting background information about the technology that underpi ...

随机推荐

- [HNOI2013]比赛 (用Hash实现记忆化搜索)

[HNOI2013]比赛 题目描述 沫沫非常喜欢看足球赛,但因为沉迷于射箭游戏,错过了最近的一次足球联赛.此次联 赛共N支球队参加,比赛规则如下: (1) 每两支球队之间踢一场比赛. (2) 若平局, ...

- MySQL删除数据后磁盘空间的释放情况【转】

OPTIMIZE TABLE 当您的库中删除了大量的数据后,您可能会发现数据文件尺寸并没有减小.这是因为删除操作后在数据文件中留下碎片所致.OPTIMIZE TABLE 是指对表进行优化.如果已经删除 ...

- MVC layout 命名空间引用问题

虽然用MVC做了很多项目,但是都是在别人搭好的框架上实现 今天碰到一个很简单的命名空间引用问题 如图所示,Scripts和Styles 都没有引用命名空间 解决方法一: 直接使用 System.Web ...

- Petrozavodsk WinterTraining 2015

PetrozavodskWinterTraining2015 A - Three Servers 题目描述:有\(n\)个数,将这\(n\)个数分成\(3\)堆,使得\(3\)堆中和的最大值减最小值最 ...

- 数组用console.log输出

输出的时候,如果前面有字符串,那么输出的就是整个字符串

- java collection和Iterator

Collection是描述所有 序列容器的共性的根接口,它可以被认为是一个"附属接口",即因为要表示其他若干个接口的共性而出现的接口,另外,java.uitl.AbstaractC ...

- 浅谈SpringMVC

M--模型(实体vo[视图对象]与页面对面) V--视图(JSP,,velocity,FreeMarker,html,thymeleaf) C--控制器(servlet,if语句控制M数据跳转到V进行 ...

- Smashing The Browser:From Vulnerability Discovery To Exploit学习记录

浏览器Fuzz技术 漏洞挖掘 白盒挖掘 代码审计 自动化代码分析 黑盒挖掘 Fuzzing 两种Fuzzing技术 静态Fuzzing 基于变异的 文件.文档 多媒体 bf3 基于生成的 浏览器 重点 ...

- 使用GIT管理UE4代码

在OSCHINA的GIT上创建远程项目 cd existing_git_repo git init git add Onepass/ Source/ notes.txt git commit -m & ...

- 【BZOJ】2120: 数颜色

题解 练习一下带修改莫队 先按照左端点的块排序,再按照右端点的块排序,然后按照时间排序 每个修改操作存一下修改前这个位置的值就可以逆序操作了 代码 #include <bits/stdc++.h ...