调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下

编译

在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是编译所有文件,这里选择 Compile->Compile All,如下图所示;

在脚本窗口中将出现一行绿色字体

# Compile of altera_mf.v was successful.

# Compile of counter.v was successful.

# Compile of rom.v was successful.

# Compile of rom_top.v was successful.

# Compile of rom_tst.v was successful.,说明文件编译成功,在该文件的状态栏后有一绿色的对号,表示编译成功;

同时,状态那一栏出现两个问号变成了√,表明编译成功,没有语法错误。

添加仿真信号

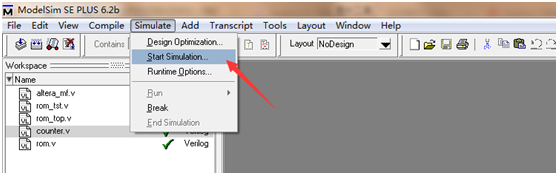

下面我们开始仿真,点击菜单 Simulate->start Simulate。

出现如下图所示的界面,展开 Design 选项卡下的 work 库,并选中其中的 rom_tst,这是在 Simulate 中出现了 work. rom_tst表示要仿真的对象,在优化那一栏不选择优化,如果选择优化的话,有些信号在仿真的时候会被优化掉,观察不了。点击 OK;

点击OK后,选中的仿真模块将会被加载到工程里面进行仿真,这里可能会出现错误,一般的问题是在testbench例化的模块名,模块信号有错误或者是信号参数有错误,如果出现错误则需要修改然后重新编译将待测试的模块加载到工程。

加载成功后,工程工作窗口会跳到sim窗口,会出现如下界面:

在sim窗口可以看到testbench设计的3个部分,初始化、always、例化的模块。这里需要观察的信号就是例化模块输出的信号,由此右击rom_top_1,选择add->add to wave,将待测试模块的信号添加到波形观察窗口中进行仿真观察。

添加后的wave窗口如下图所示

仿真开始

仿真可以采用窗口上的工具栏进行设置,如下图所示

同时也可以通过再脚本窗口输入运行时间后按下回车键进行运行:run 1ms,这里运行1ms。

仿真信号查看

仿真运行后,波形窗口会出现如下所示的信号。

这里选中信号counter_out、rom_data,右击如下图所示,设置信号显示的数制,这里选择无符号整形进行显示。

可以看到counter_out信号由0在每个时钟上升沿进行加一操作,在计数到255后重新再从0计数。rom_data则在每个时钟信号上升沿下将sin信号输出。

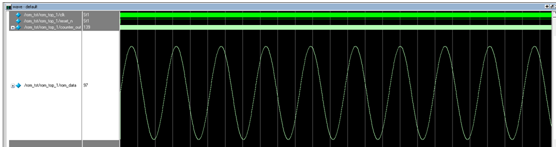

在信号显示中,有时为了观察信号更直接,需要将信号采用模拟的方式进行显示,modelsim软件可以满足这一要求,这里选中rom_data信号,右击如下图所示

将信号设置为模拟显示,接着弹出如下窗口,可以设置调整信号显示的幅值,这里默认原始值,点击ok。

最后还要设置下波形窗口中模拟信号显示所占有的宽度,以满足信号采用模拟显示后不会和其他信号显示重叠在一起。选择rom_data信号,右击如下图所示。

进行设置信号显示的格式,如下图所示,这里设置显示的高度为300,可以满足信号最大值255。

最后可以看到将rom_data显示为模拟信号会得到如下的结果。

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

调用altera IP核的仿真流程—下的更多相关文章

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- 基于modelsim-SE的简单仿真流程—下

基于modelsim-SE的简单仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile A ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- altera DDR2 IP核之仿真

在生成的IP核文件夹下,有一个testbench文件夹,里面包含了一个example测试激励和DDR2仿真模型. 如下 20 -rw-r--r-- 1 Administrator 197121 171 ...

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- altera ip 核小究

用quartus的MegaWizard工具生成一个乘法器multiplier,会在工程目录下产生 multiplier.qip (可选) multiplier_bb.v (可选) multip ...

- 基于modelsim-SE的专业进阶仿真流程

基于modelsim-SE的专业进阶仿真流程 通过<基于modelsim-SE的简单仿真流程>和<调用altera IP核的仿真流程>是否感受到仿真流程中的繁琐步骤,特别是在m ...

随机推荐

- .net请求URL过长,解决方案

<system.web> 节点下加上 <httpRuntime requestValidationMode="2.0" maxQueryStringLength= ...

- Windows下Memcached安装与配置实例

环境声明: 服务器: Windows Server 2008r2: Memcached: Memcached 64-bit for Windows(64位) From: http://www.urie ...

- 深入理解JavaScript——闭包

跟很多新手一样我也是初入前端,对闭包的理解花费的时间和精力相当的多.效果也还行,今天我就来根据自己的理解细致的讲一讲闭包,由于是初入学习的时候不免有一些弯路和困惑,我想信这也是很多跟我一样的人会同样遇 ...

- 解决微信授权回调页面域名只能设置一个的问题 [php]

最终的解决方案是:https://github.com/liuyunzhuge/php_weixin_proxy,详细的介绍请往下阅读. 在做项目集成微信登录以及微信支付的时候,都需要进行用户授权.这 ...

- [上架] iOS "app-specific password" 上架问题

当你的 Apple ID 改用双重认证密码时,上架 iOS App 需要去建立一个专用密码来登入 Apple ID 才能上架. 如果使用 Application Loader 上传时,得到这个讯息: ...

- 关闭firefox的plugincheck

每次打开firefox都弹出这个SB页面: https://www.mozilla.org/en-US/plugincheck/ 关不掉, 很是烦人. 经过地番google,找到了答案: about: ...

- IIS服务器和xampp中的appche服务器端口冲突解决办法

今天在启动xampp中的appche的时候,发现以前能起来的现在起不来了.想到可能是最近配置的系统自带的IIS服务器把appche的端口给占用了. (appche和iis的默认端口号都是:80:) 问 ...

- [deviceone开发]-动态添加组件add方法的示例

一.简介 这个示例详细介绍ALayout的add方法的使用(原理也适用于Linearlayout),以及add上去的新ui和已有的ui如何数据交换,初学者推荐.二.效果图 三.相关下载 https:/ ...

- 正确制作一个iframe,认识iframe

iframe作为一个网站之间交互的桥梁,受到很多站长的喜爱,但是又有不安全的因素存在,所以正确填写属性是很重要的. <iframe name="my_iframe" heig ...

- CSS3_01之选择器、Hack

1.兄弟选择器:①相邻兄弟选择器:元素的后一个兄弟元素,选择器1+选择器2:②通用兄弟选择器:元素后的所有兄弟元素,选择器1~选择器2: 2.属性选择器:attr表示属性名称,elem表示元素名:①[ ...