基于FPGA的视频时序生成

之前用FPGA做过视频时序方面的设计,现将视频时序的设计方法分享给大家,希望对大家有所帮助。

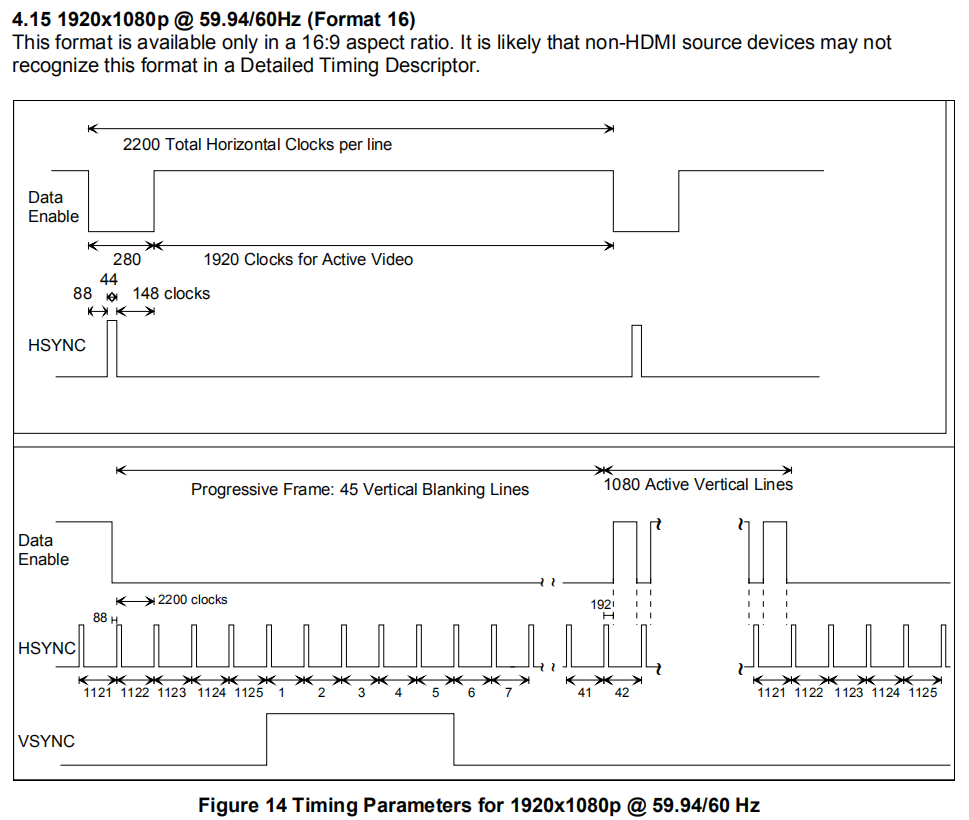

时序部分可以参考CEA-861D,VESA时序标准。

1080P一帧视频中,一行有2200个像素,其中280个像素为消影区像素,1920个像素为有效像素。 一场有1125行,其中45行为消影区,1080个有效行。

1080P@60的时钟计算方法: 2200x1125x60=148500000, 即148.5MHz。

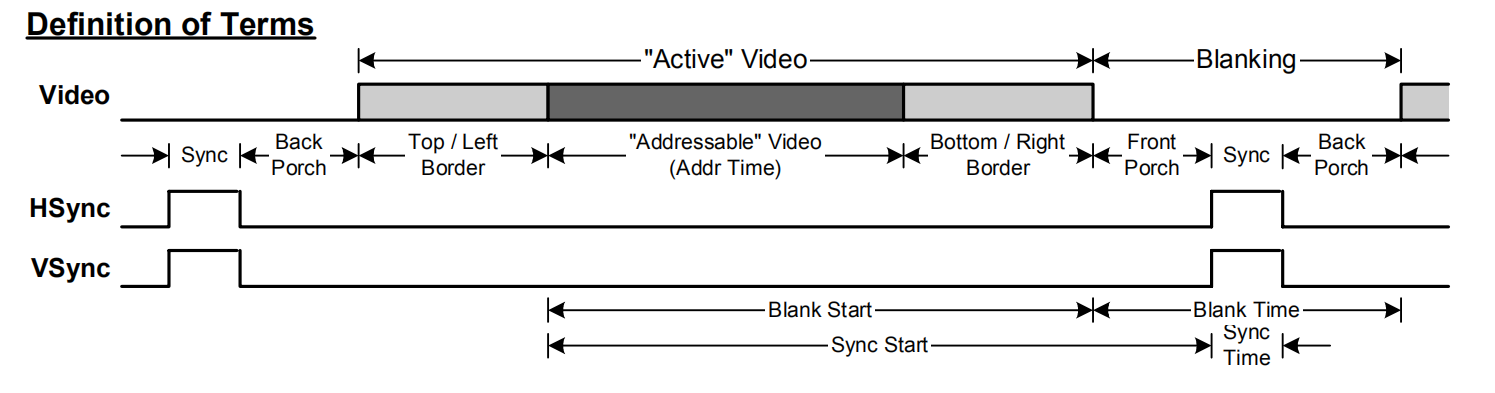

1080P的时序图请参考如下图所示:

通过以上两幅图,我们可以很好地理解视频时序,在每一行的开始前和结束后,都是Blank。

我们可以通过设计计数器的方法来实现 代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: Ricky

//

// Create Date: 16:38:46 04/17/2019

// Design Name: Video timming generator

// Module Name: Video_timming

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module Video_timming(

input wire clk,

input wire reset_n,

output reg hsync_out,

output reg hblank_out,

output reg vsync_out,

output reg vblank_out,

output reg DE_out ); ////////////////////hsblnk means the biggest active pixels from 0~1919, and it's the begining of hblank.

////////////////////hssync means the active pixels + Front Proch, and it's the begining of hsync signal.

////////////////////hesync means the active pixels + Front Proch + hsync, it's the end of hsync signal.

////////////////////heblnk means the biggest line pixels from 0~2199,it's the end of a line. ////////////////////vsblnk means the biggest active lines from 0~1079, and it's the begining of vblank.

////////////////////vssync means the active lines + V Front Proch, and it's the begining of vsync signal.

////////////////////vesync means the active lines + V Front Proch + vsync, it's the end of vsync signal.

////////////////////veblnk means the biggest lines from 0~1124, it's the end of a frame. parameter [:] tc_hsblnk = 'b0111_0111_1111; //hsblnk_1080P = 1920-1 = 1919

parameter [:] tc_hssync = 'b0111_1101_0111; //hssync_1080P = 1919 + 88 = 2007

parameter [:] tc_hesync = 'b1000_0000_0011; //hesync_1080P = 1919 + 88 + 44 = 2051

parameter [:] tc_heblnk = 'b1000_1001_0111; //heblnk_1080P = 1919 + 88 + 44 + 148 = 2199

parameter [:] tc_vsblnk = 'b0100_0011_0111; //vsblnk_1080P = 1080 -1 =1079

parameter [:] tc_vssync = 'b0100_0011_1011; //vssync_1080P = 1079 + 4 = 1083

parameter [:] tc_vesync = 'b0100_0100_0000; //vesync_1080P = 1079 + 4 + 5 = 1088

parameter [:] tc_veblnk = 'b0100_0110_0100; //veblnk_1080P = 1079 + 4 + 5 + 36 = 1124 reg reg0;

reg reg1;

wire rst_n;

reg hsync,vsync,hblank,vblank;

reg [:] pixel_cnt,h_cnt,h_cntb; always @ (posedge clk or negedge reset_n) //这里使用同步复位异步释放的方法设计复位

begin

if ( reset_n == 'b0)begin

reg0 <= ;

reg1 <= ;

end

else begin

reg0 <= ;

reg1 <= reg0;

end

end assign rst_n = reg1; always @ (posedge clk or negedge rst_n) begin // Pixel clock count

if(!rst_n)

pixel_cnt <= 'd0;

else

if(pixel_cnt >= tc_heblnk) //

pixel_cnt <= 'd0;

else

pixel_cnt <= pixel_cnt + ;

end always @ (posedge clk or negedge rst_n) begin// generate hsync

if(!rst_n)

hsync <= 'b0;

else

if((pixel_cnt >= tc_hssync) && (pixel_cnt < tc_hesync))//2007 //

hsync <= 'b1;

else

hsync <= 'b0;

end always @ (posedge clk or negedge rst_n) begin // generate hblank

if(!rst_n)

hblank <= 'b1;

else

if((pixel_cnt >= tc_hsblnk) && (pixel_cnt < tc_heblnk)) //1919 //

hblank <= 'b1;

else

hblank <= 'b0;

end always @ (posedge clk or negedge rst_n) begin //Line count

if(!rst_n)

h_cnt <= 'd0;

else

if(h_cnt > tc_veblnk) //

h_cnt <= 'd0;

else

if(pixel_cnt == tc_hssync-) //

h_cnt <= h_cnt + ;

else

h_cnt <= h_cnt;

end always @ (posedge clk or negedge rst_n) begin // Generate vsync

if(!rst_n)

vsync <= 'b0;

else

if ((h_cnt > tc_vssync) && (h_cnt <= tc_vesync)) //1083 //

vsync <= 'b1;

else

vsync <= 'b0;

end always @ (posedge clk or negedge rst_n) begin //Line Countb

if(!rst_n)

h_cntb <= 'd0;

else

if(h_cntb > tc_veblnk) //

h_cntb <= 'd0;

else

if(pixel_cnt == tc_hsblnk - ) //

h_cntb <= h_cntb + ;

else

h_cntb <= h_cntb;

end always @ (posedge clk or negedge rst_n) begin // Generate vblank

if(!rst_n)

vblank <= 'b1;

else

if((h_cntb > tc_vsblnk) && (h_cntb <= tc_veblnk)) //1079 //

vblank <= 'b1;

else

vblank <= 'b0;

end always @ (posedge clk or negedge rst_n) begin // Generate output singles

if(!rst_n) begin

hsync_out <= 'b0;

vsync_out <= 'b0;

hblank_out <= 'b0;

vblank_out <= 'b0;

DE_out <= 'b0;

end

else

begin

hsync_out <= hsync;

vsync_out <= vsync;

hblank_out <= hblank;

vblank_out <= vblank;

DE_out <= (~ hblank) & (~ vblank);

end

end endmodule

TB如下:

`timescale 1ns/1ns module TB_Timing_gen; reg clk, reset_n;

wire hsync,vsync,de,hblank,vblank; initial begin

clk = ;

reset_n = ;

#

reset_n = ;

end always # clk = ~clk; Video_timming timing_inst(

.clk (clk),

.reset_n (reset_n),

.hsync_out (hsync),

.hblank_out (hblank),

.vsync_out (vsync),

.vblank_out (vblank),

.DE_out (de) ); endmodule

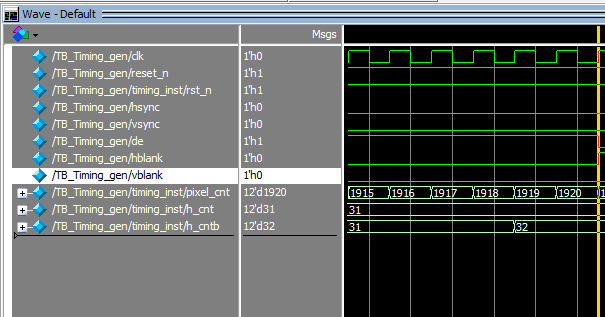

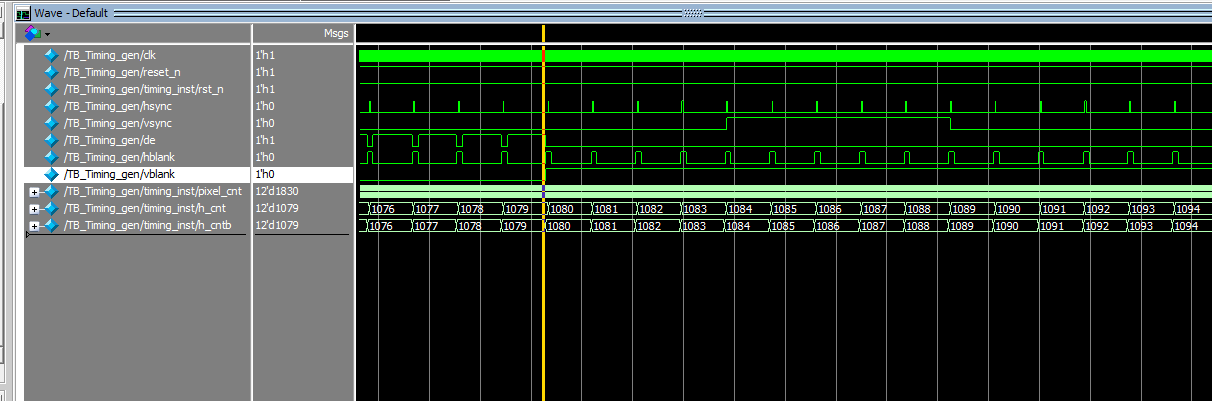

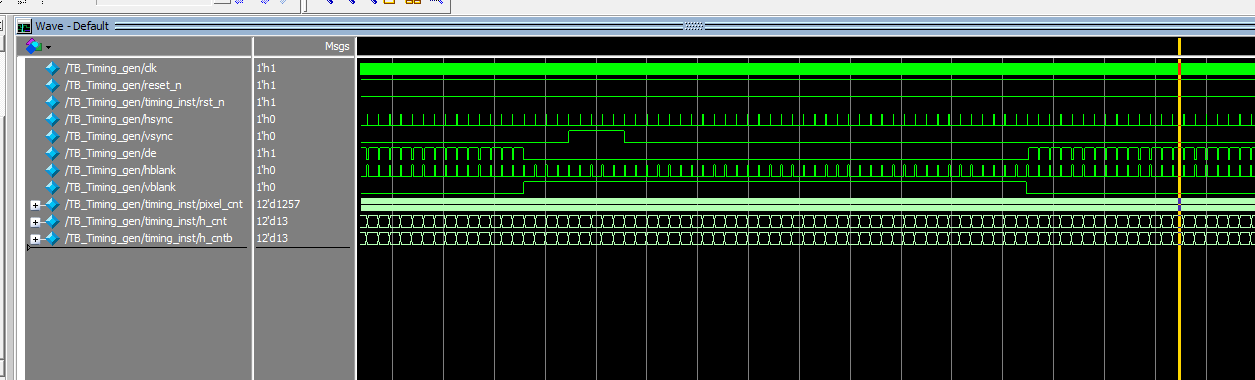

波形如下:

每行有1920个像素。

每行有1920个像素。

hsync, DE,hblank的关系。

hsync, DE,hblank的关系。

Vblan, Vsync和DE的关系,和hsync的关系。

原创代码,转载请注明出处,该部分已经申请发明专利,只是这里是用verilog写的,之前专利是用VHDL写的。

基于FPGA的视频时序生成的更多相关文章

- 基于FPGA视频时序生成中的库文件

上一篇分享了一个视频时序生成代码,下面我根据之前项目中用到的时序,对各个参数做了库文件,方便调用. -- -- Package File Template -- -- Purpose: This pa ...

- 基于FPGA的DDR3多端口读写存储管理系统设计

基于FPGA的DDR3多端口读写存储管理系统设计 文章出处:电子技术设计 发布时间: 2015/03/12 | 1747 次阅读 每天新产品 时刻新体验专业薄膜开关打样工厂,12小时加急出货 机载 ...

- 基于FPGA的图像去噪

目录 结构图 其中FPGA 控制模块为核心,通过它实现视频图像数据的获取.缓存.处理和控制各模块间通讯[1].由CCD 相机对目标成像,高速图像数据由camera link 实时传输[2],经信号转换 ...

- 基于Xilinx FPGA的视频图像采集系统

本篇要分享的是基于Xilinx FPGA的视频图像采集系统,使用摄像头采集图像数据,并没有用到SDRAM/DDR.这个工程使用的是OV7670 30w像素摄像头,用双口RAM做存储,显示窗口为320x ...

- 基于FPGA的LCD+CMOS视频采集显示使用小结

基于FPGA的LCD+CMOS视频采集显示 液晶显示器采用扫描模式,RGB888 电源采用:+5V供电 usb供电有时候会出现供电不足的问题 显示器接口有两种选择:16bit或24bit 分别对应 ...

- 优化基于FPGA的深度卷积神经网络的加速器设计

英文论文链接:http://cadlab.cs.ucla.edu/~cong/slides/fpga2015_chen.pdf 翻译:卜居 转载请注明出处:http://blog.csdn.net/k ...

- 基于FPGA的VGA可移植模块终极设计【转】

本文转载自:http://www.cnblogs.com/lueguo/p/3373643.html 略过天涯 基于FPGA的VGA可移植模块终极设计 一.VGA的诱惑 首先,VGA的驱动,这事, ...

- FPGA经典:Verilog传奇与基于FPGA的数字图像处理原理及应用

一 简述 最近恶补基础知识,借了<<Verilog传奇>>,<基于FPGA的嵌入式图像处理系统设计>和<<基千FPGA的数字图像处理原理及应用>& ...

- 基于FPGA的线阵CCD图像测量系统研究——笔记

本文是对基于FPGA的线阵CCD图像测量系统研究(作者:高尚)的阅读笔记 第一章绪论 1. 读读看 读了前面的摘要依然没有看懂作者要做什么.接着往下读....终于看到了一个字眼“基于机器视觉的图像测量 ...

随机推荐

- php隐藏手机号指定位数

function mobileReplace($mobile,$start,$end,$str="*"){ $countStr = abs($end-$start); $repla ...

- kth min_max容斥

题解: 普通的$min-max$容斥是用来求最后出现元素的期望之类的 $kth min-max$容斥进一步解决倒数第k个出现的元素的期望 给出公式: $kthmax(S)=\sum\limits_{T ...

- python---日常练习

##输入a,b,c,d4个整数,计算a+b-c*d的结果 #numa=input('请输入整数:'); #numb=input('请输入整数:'); #numc=input('请输入整数:'); #n ...

- 网络编程-Mysql-1、数据库的启动关闭,创建数据库,表等基本操作

启动服务端:sudo service mysql start 关闭服务端:suodo service mysql stop 重启服务端:suodo service mysql restart 连接数据 ...

- js为什么是单线程的?10分钟了解js引擎的执行机制

深入理解JS引擎的执行机制 1.JS为什么是单线程的? 为什么需要异步? 单线程又是如何实现异步的呢? 2.JS中的event loop(1) 3.JS中的event loop(2) 4.说说setT ...

- Leetcode 记录(201~300)

实习面试前再完成100题,争取能匀速解释清楚题 204. Count Primes 素数筛 class Solution { public: int countPrimes(int n) { ) ; ...

- c++11 线程池

也可参考: https://www.cnblogs.com/ailumiyana/p/10016965.html *** https://blog.csdn.net/jlusuoya/article/ ...

- MongoDB_简介_安装_基本使用_js_mongoose 操作 MongoDB 编程

数据库 按照数据结构来组织.存储和管理数据的仓库 程序运行时,数据存储于内存中,一旦程序结束或者断电,就会数据丢失 为了将有些数据持久化存储到硬盘中,并确保可操作性和安全性,就需要数据库 分类: 关系 ...

- 10_常见的get和post请求_路由器_ejs服务器渲染模板引擎

1. 常见的 get 和 post 请求有哪些? 常见的发送 get 请求方式: 在浏览器地址栏输入 url 地址访问 所有的标签默认发送的是 get 请求:如 script link img a f ...

- [LeetCode] Design Circular Deque 设计环形双向队列

Design your implementation of the circular double-ended queue (deque). Your implementation should su ...