Verilog学习笔记简单功能实现(五)...............序列检测设计

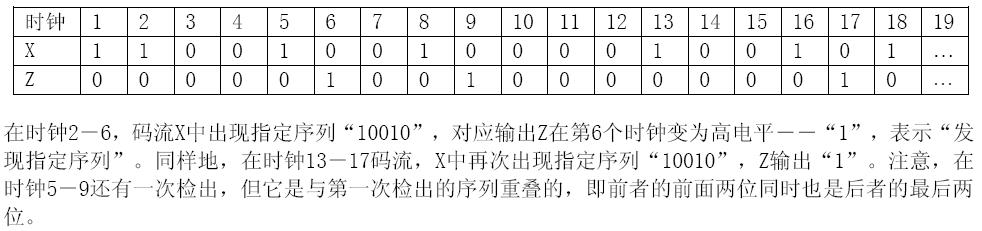

这里采用夏宇闻教授第十五章的序列检测为例来学习;

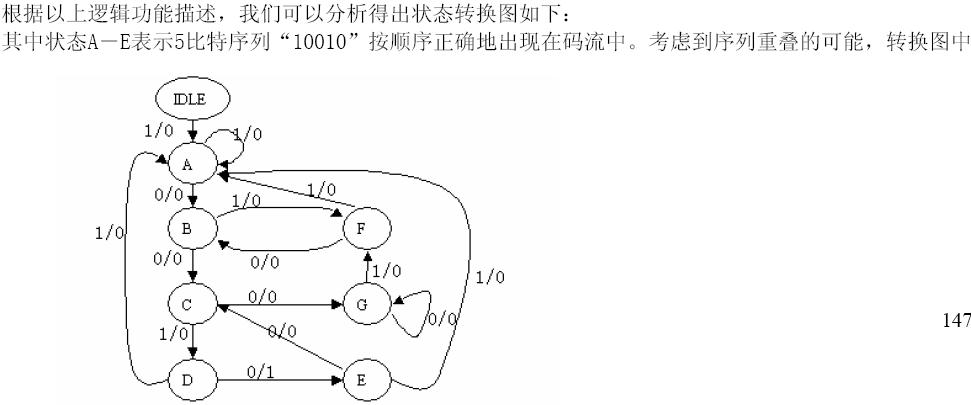

从以上的状态转换图可以写出状态机的程序:

module seqdet(x,out,clk,rst);

input x,clk,rst;

output out;

reg [:]state;

wire out;

parameter IDLE='b0,

A='d1,

B='d2,

C='d3,

D='d4,

E='d5,

F='d6,

G='d7;

assign out=(state==D&&x==)?:;

always @(posedge clk or negedge rst)

begin

if(!rst)

state=IDLE;

else

case(state)

IDLE:if(x==) state<=A;

else state<=IDLE;

A:if(x==) state<=B;

else state<=A;

B:if(x==) state<=C;

else state<=F;

C:if(x==) state<=D;

else state<=G;

D:if(x==) state<=E;

else state<=A;

E:if(x==) state<=C;

else state<=A;

F:if(x==) state<=B;

else state<=A;

G:if(x==) state<=F;

else state<=G;

default: state<=IDLE;

endcase end

endmodule

以下是测试模块:

`timescale 1ns/1ns

`define halfperiod module testseqdet;

reg clk,rst;

reg [:]data;

wire out,x;

assign x=data[];

initial begin

clk=;

rst=;

# rst=;

# rst=;

data='b1100_1001_0000_1001_0100;

end

always #(`halfperiod) clk=~clk;

always @(posedge clk)

begin

# data={data[:],data[]};

end

seqdet m(.x(x),.out(out),.clk(clk),.rst(rst));

endmodule

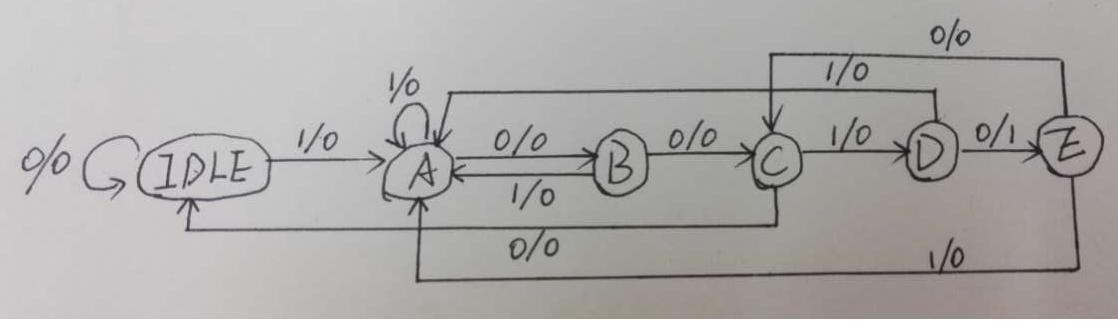

其实这里也可以采用六个状态来实现功能:

1 module seqdet(x,out,clk,rst,state);

2 input x,clk,rst;

3 output out;

4 output [2:0]state;

5 reg [2:0]state;

6 wire out;

7 parameter IDLE=3'd0,

8 A=3'd1,

9 B=3'd2,

10 C=3'd3,

11 D=3'd4,

12 E=3'd5;

13 assign out=(state==D&&x==0)?1:0;

14 always @(posedge clk)

15 begin

16 if(!rst) state<=IDLE;

17 else

18 case(state)

19 IDLE:if(x==1) state<=A;

20 else state<=IDLE;

21 A:if(x==0) state<=B;

22 else state<=A;

23 B:if(x==0) state<=C;

24 else state<=A;

25 C:if(x==1) state<=D;

26 else state<=IDLE;

27 D:if(x==0) state<=E;

28 else state<=A;

29 E:if(x==0) state<=C;

30 else state<=A;

31 default: state<=IDLE;

32 endcase

33 end

34 endmodule

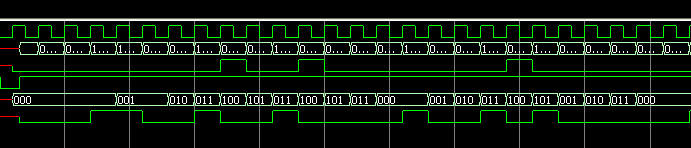

以下是测试模块:

`timescale 1ns/1ns

module test_seqdet;

reg clk,rst;

reg [:]data;

wire [:]state;

wire x,out;

assign x=data[];

initial

begin

clk=;

rst=;

# rst=;

# rst=;

data='b1100_1001_0000_1001_0100;

end always # clk=~clk;

always @(posedge clk)

begin

data={data[:],data[]};

end

seqdet m(.x(x),.clk(clk),.rst(rst),.out(out),.state(state));

endmodule

module seqdet

(

input wire x,

input wire clk,

input wire rst,

output wire z,

output reg [:] q

); wire [:] q_next; assign q_next ={q[:],x};

assign z = (q_next== 'b10010) ? 1'b1:'b0; always @ (posedge clk,negedge rst)

if(!rst)

q <= 'd0;

else

q <= q_next; endmodule

寄存器的实现参照http://www.cnblogs.com/qiweiwang/archive/2011/04/18/2019952.html ,在这里感谢齐威王!

Verilog学习笔记简单功能实现(五)...............序列检测设计的更多相关文章

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- Verilog学习笔记简单功能实现(八)...............同步FIFO

Part 1,功能定义: 用16*8 RAM实现一个同步先进先出(FIFO)队列设计.由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出.写入和读出的操作(高电平有效)由时钟的上 ...

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- Verilog学习笔记简单功能实现(一)...............D触发器

module D_flop(data,clk,clr,q,qb); input data,clk,clr; output q,qb; wire a,b,c,d,e,f,ndata,nclk; nand ...

- Verilog学习笔记简单功能实现(八)...............异步FIFO

基本原理: 1.读写指针的工作原理 写指针:总是指向下一个将要被写入的单元,复位时,指向第1个单元(编号为0). 读指针:总是指向当前要被读出的数据,复位时,指向第1个单元(编号为0). ...

- Verilog学习笔记简单功能实现(七)...............接口设计(并行输入串行输出)

利用状态机实现比较复杂的接口设计: 这是一个将并行数据转换为串行输出的变换器,利用双向总线输出.这是由EEPROM读写器的缩减得到的,首先对I2C总线特征介绍: I2C总线(inter integra ...

- Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第十五章:第一人称摄像机和动态索引

原文:Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第十五章:第一人称摄像机和动态索引 代码工程地址: https://g ...

随机推荐

- Atitit 作用域的理解attilax总结

Atitit 作用域的理解attilax总结 1.1. 作用域是指对某一变量和方法具有访问权限的代码空间, 1 1.2. 作用域的使用提高了程序逻辑的局部性,增强程序的可靠性,减少名字冲突.1 1.3 ...

- Atitti css transition Animation differ区别

Atitti css transition Animation differ区别 1.1. transition的优点在于简单易用,但是它有几个很大的局限. 1 1.2. Transition ...

- BugHD for JavaScript上线,轻松收集前端 Error

从收集 APP 崩溃信息到全面收集网站出现的 Error,现在的 BugHD 变得更加强大.目前,BugHD JS Error 收集功能 已正式上线,前端 er 们不用再面对一堆 Bug 无处下手. ...

- iOS 8.1.3 “各路助手挺尸”、“封杀一切助手

图片来自 http://www.redmondpie.com 最近苹果发布了8.1.3系统更新.从更新日志看,没有多少变化(错误修复,提高稳定性和性能),但是苹果修复了一个"漏洞" ...

- IO流-文本IO\读写二进制数据

文本IO 一.简述 OutputStreamWriter类使用选定的编码方式吧Unicode字符流转换为字节流,InputStreamReader类将包含字节的输入流转为可以产生Unicode字符的读 ...

- Dijkstra算法(二)之 C++详解

本章是迪杰斯特拉算法的C++实现. 目录 1. 迪杰斯特拉算法介绍 2. 迪杰斯特拉算法图解 3. 迪杰斯特拉算法的代码说明 4. 迪杰斯特拉算法的源码 转载请注明出处:http://www.cnbl ...

- [OpenCV] Samples 07: create_mask

鼠标画线,圈地,构造相关mask图片(黑白). 支持鼠标左键右键中间键点击事件. /* * create_mask.cpp * * Author: * Siddharth Kherada <si ...

- 为什么需要Bundler

对于从Node.js转Ruby的人很可能会有和我一样的疑惑,为什么要有Bundler这个东西?Rubygems不够吗? 从Node.js到Ruby的包管理器 在Node的世界里,依赖管理是由npm来完 ...

- Network - FTP与SFTP

FTP --- FTP File Transfer SFTP --- SSH File Transfer 缩写 名称 协议与端口 安全策略 特征描述 守护进程(linux) 应用场景 SFTP SSH ...

- 初探JavaScript(四)——作用域链和声明提前

前言:最近恰逢毕业季,千千万万的学生党开始步入社会,告别象牙塔似的学校生活.往往在人生的各个拐点的时候,情感丰富,感触颇深,各种对过去的美好的总结,对未来的展望.与此同时,也让诸多的老“园”工看完这些 ...