nios II--实验1——hello_world硬件部分

hello_world

硬件开发

新建原理图

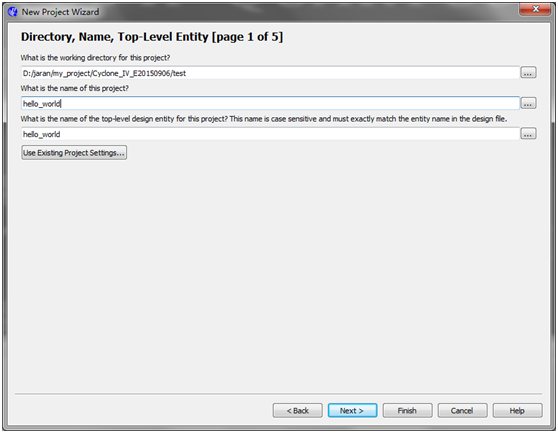

1、打开Quartus II 11.0,新建一个工程,File -> New Project Wizard…,忽略Introduction,之间单击 Next> 进入下一步。分别设置工程工作目录、工程名称。这里需要注意的是工程工作目录中请使用英文,不要含有空格等,否则在后面使用Nios II IDE的时候会出现问题。设置好后如图1所示。然后进行下一步。

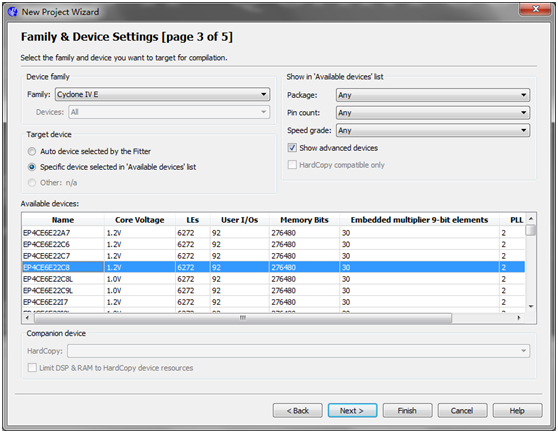

2、添加已经存在的文件,这里没有需要添加的文件,直接单击 Next> 进入下一步。进行器件设置。板子使用的是 Cyclone IV家族的 EP4CE6E22C8芯片,选择好后直接进入下一步。进行EDA工具设置,由于工程中不进行仿真等,故不进行设置,如果需要进行ModelSim仿真,则在Simulation行中,选择Tool Name 为ModelSim-Altera(这里根据所安装的ModelSim版本进行选择),Format(s)选择为Verilog HDL(这里也是根据所掌握的硬件描述语言进行选择)。点击 Next> ,进入了Summary(摘要)页面,然后单击 Finish 完成即可。

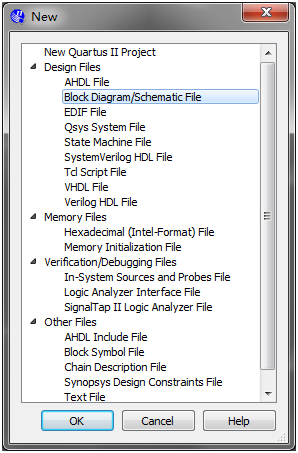

3、新建 Block Diagram/Schematic File (方块图/原理图文件)。单击 File -> New..,选择Design Files中的Block Diagram/Schematic File,单击OK即可。

QSys调用模块

- 启动Qsys 工具,进行IP模块的调用。单击 Tools -> Qsys

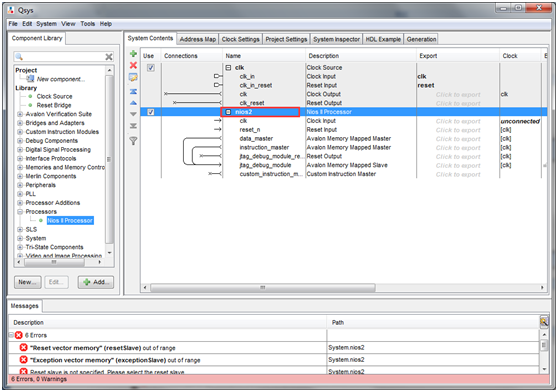

,进入Qsys设置界面。系统已经默认添加了时钟模块,名称为 clk_0 ,这里选中 clk_0,右击,选择Rename,将其名称更改为clk。以下再添加任何模块,都要进行类似的名称更改,更改名称的方法类似,就不在重复叙述了。

,进入Qsys设置界面。系统已经默认添加了时钟模块,名称为 clk_0 ,这里选中 clk_0,右击,选择Rename,将其名称更改为clk。以下再添加任何模块,都要进行类似的名称更改,更改名称的方法类似,就不在重复叙述了。

- 添加软核处理器的各部分模块。总共需要添加

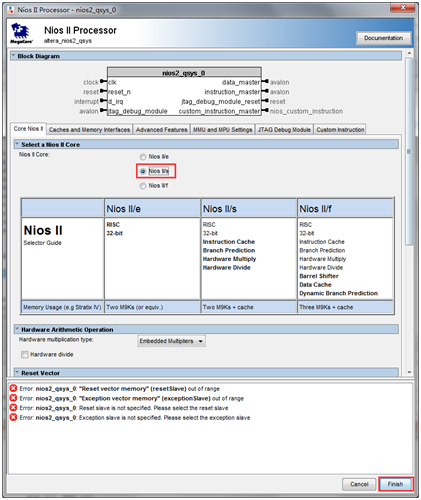

Nios II Processor、

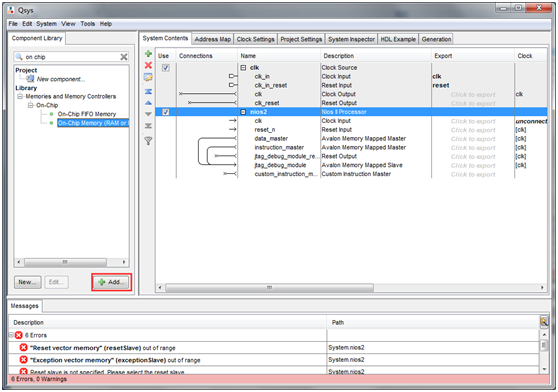

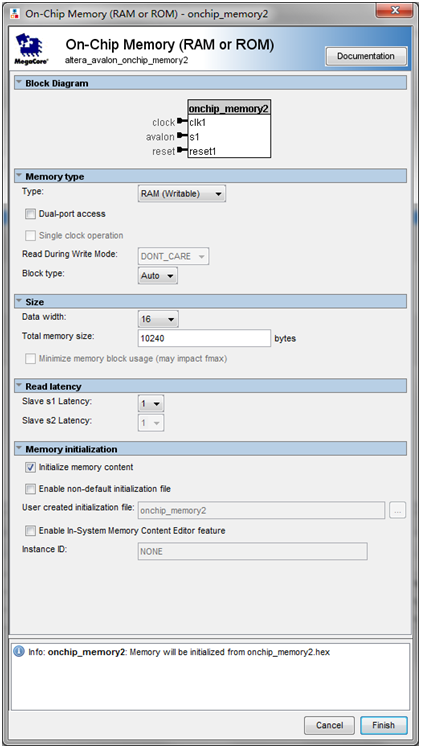

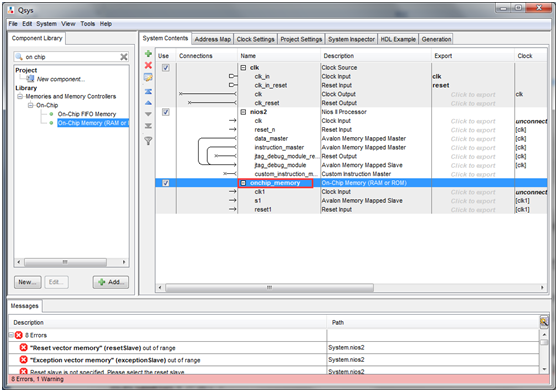

On_ChipMemory(RAM or ROM)、

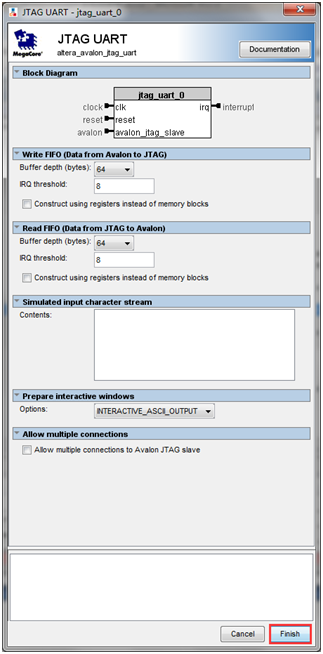

JTAG UART、

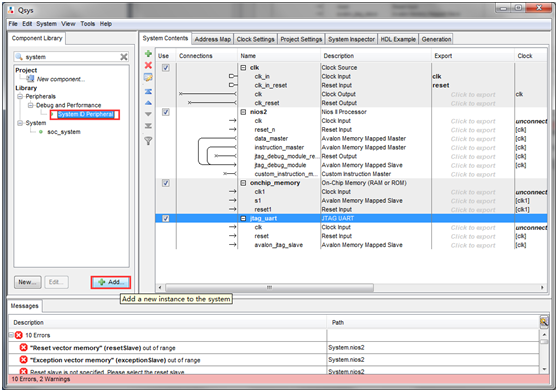

System ID Peripheral这4个模块。首先熟悉一下 Qsys 的界面。左面Component Library,是系统提供的元件库,里面有一些构成处理器的常用模块。右面是已经添加到系统的模块,也就是说,Nios II 软核处理器是可以定制的,根据具体需要来。在Component Library中搜索Nios II Processor,双击即可进行配置。首先需要选择的是Nios II 核心的类型。Nios II 软核的核心共分成三种,为e型、s型以及f型。e型核占用的资源最少,功能也最简单,速度最慢。s型核占用资源其次,功能和速度较前者都有所提升,f型核的功能最多,速度最快,相应的占用资源也最多,选择的时候根据需求和芯片资源来决定,这里选择s核。然后单击 Finish,结束当前配置。

- 下面添加片内存储器,在元件库中搜索 On Chip Memory。双击进行设置。主要设置Size中的Data width和Total memoy size。Data width设置的是数据位宽,这里设置成16位。Total memoy size设置的是片内资源的大小,需要根据芯片资源进行合理设置,这里设置为10240 bytes。单击 Finish,结束当前配置。

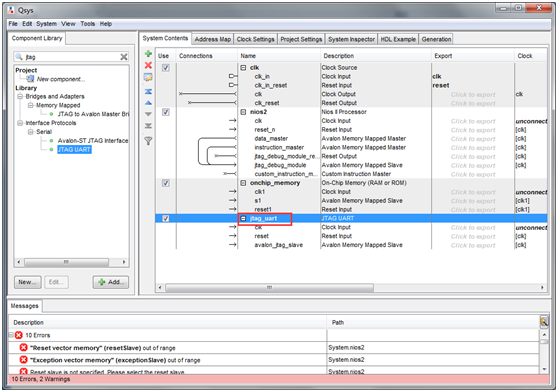

- 添加Jtag下载调试接口。在元件库中搜索 jtag uart。双击进行设置。由于系统没有特殊要求,因此这里选择默认配置即可。单击 Finish 结束当前配置。

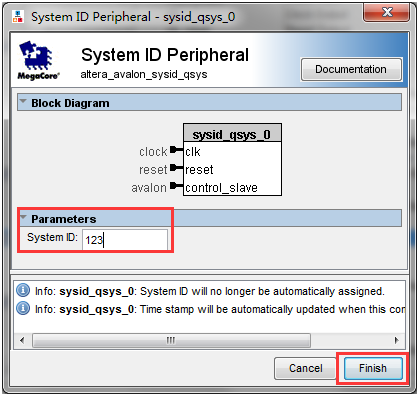

- 添加系统ID模块。系统ID是系统与其他系统区别的唯一标识。在元件库中搜索 system id peripheral,双击进行设置。这里随便进行设置,如设置为123。单击 Finish,结束当前配置。

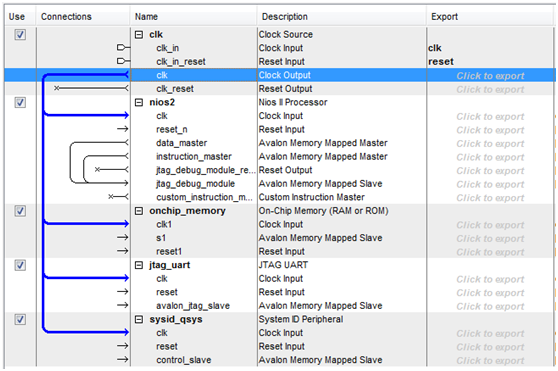

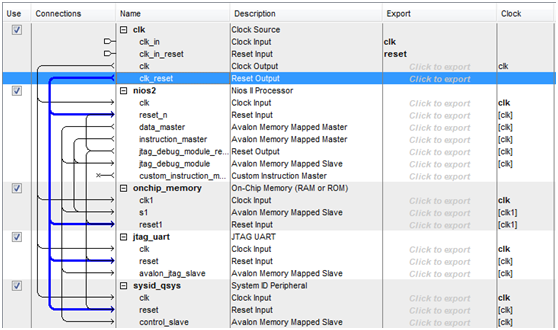

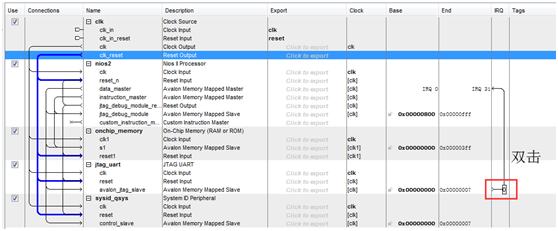

- 连线,即将右面 Connections栏目中的相关线通过设置节点进行连接。首先所有模块的clk连接起来。

然后片内存储器On-Chip Memory的s1和处理器nios2的data_master和instruction_master相连。

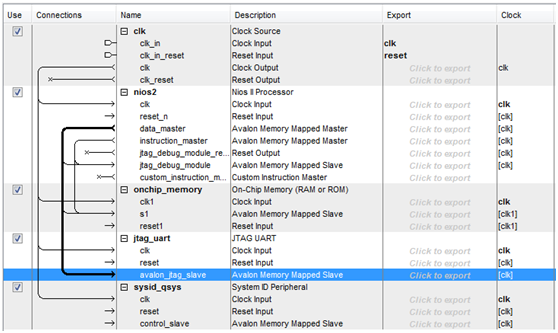

JTAG调试模块jtag_uart的avalon_jtag_slave和处理器nios2的data_master相连。

系统ID模块sysid_qsys的control_slave和处理器nios2的data_master相连。

- 设置复位信号。

- 处理器nios2的中断和jtag_uart的中断相连接。

- 进行软核的相关设置。首先双击nios2,进入处理器设置模块。在Core Nios II栏目下,将Reset vector memory 和 Exception vector memory 设置为onchip_memory.s1。

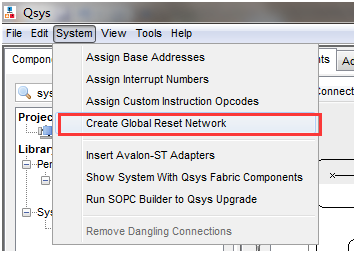

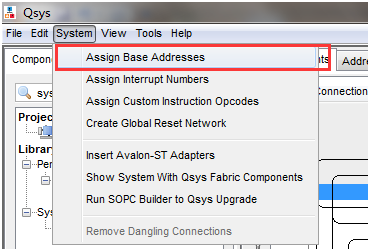

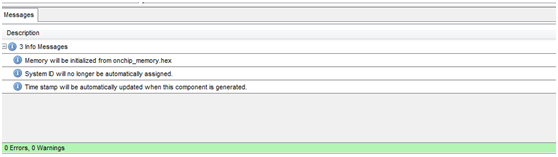

- 单击 System -> Assign Base Addresses,这时候会发现下部Messages窗口中原先的错误全部没有了,变为0 Errors,0 Warnings。如果不是这个结果,返回去按步骤检查。

- 单击 File -> Save,进行保存,这里保存文件名为hello_world。

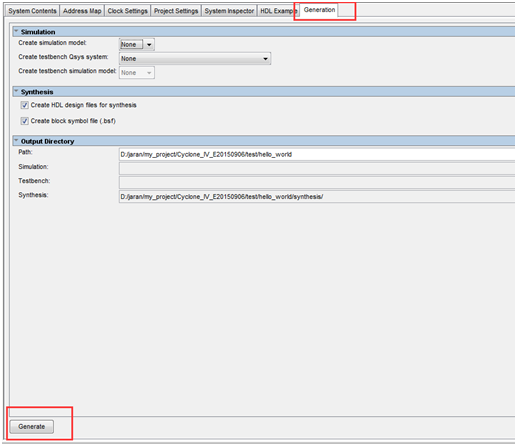

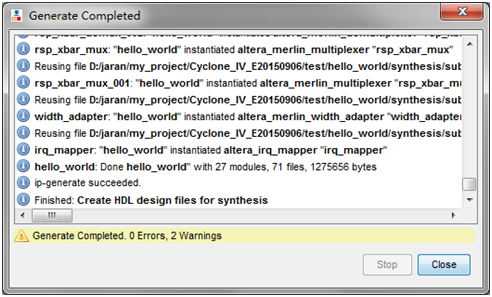

- 最后,选择Generation选项卡,设置Create simulation model为None,然后单击下面的Generate,进行生成。时间较长,大家耐心等待。

- 完成后单击close即可,然后关闭Qsys回到Quartus II界面。

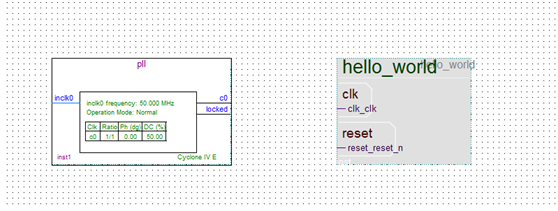

原理图添加IP模块

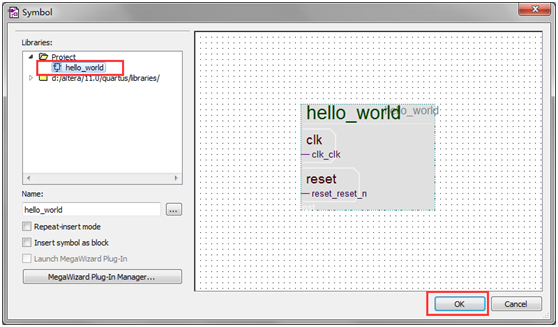

- 添加niosII核

双击Block1.bdf的空白处,打开Symbol对话框。选择project

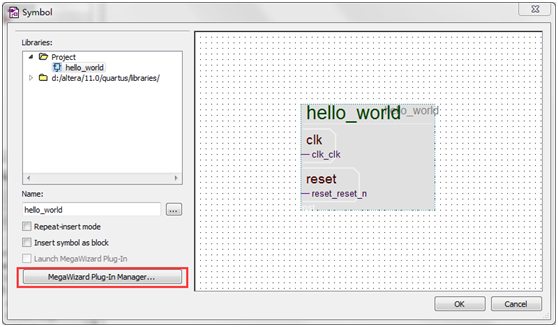

- 添加PLL

单击右下角的MegaWizard Plug-In Manager…,进入宏模块调用界面。

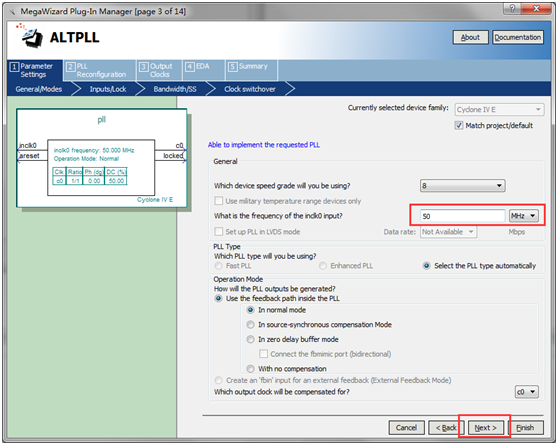

选择Creat a new custom megafunction variation,单击 Next> 进入下一步,在What name do you want for the output file下面的地址后面添加输出文件的名称PLL。然后在右侧搜索框中搜索ALTPLL,选中即可,这一步主要为系统添加时钟模块,然后单击 Next>进入下一步。

弹出ALTPLL设置对话框,这里在 General栏目的What is the frequency of the inclk0 input?地方,将时钟更改为50MHz。

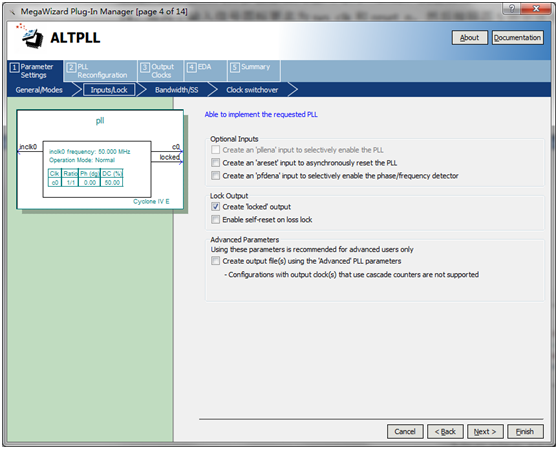

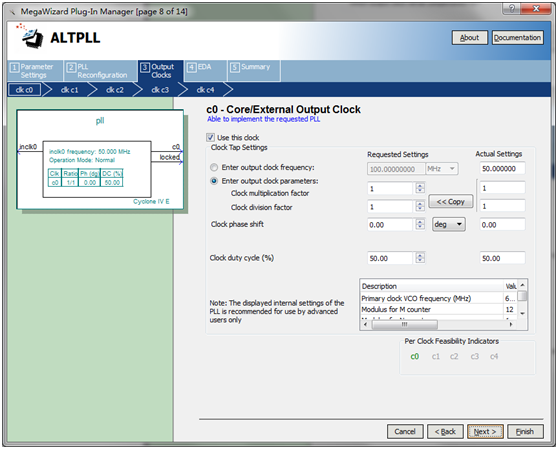

接着按照以下流程进行设置:

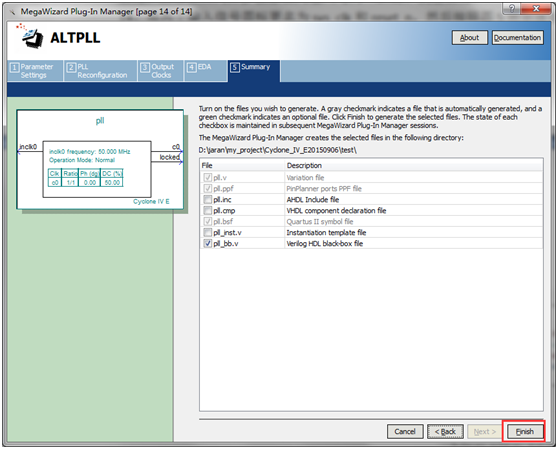

接着一直默认设置,一直next到一下窗口,点击Finish。

这时会弹出一个Quartus II IP Files对话框,单击Yes完成即可,不需要进行任何操作。然后单击Symbol对话框中的OK即可,然后将模块放在Block1.bdf中即可。

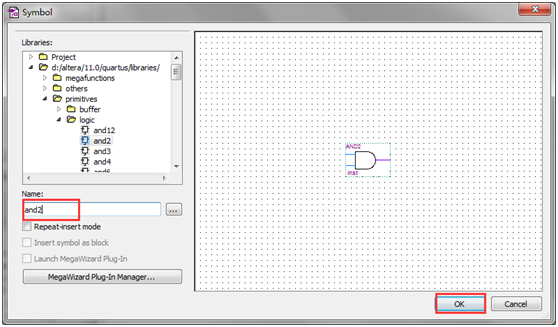

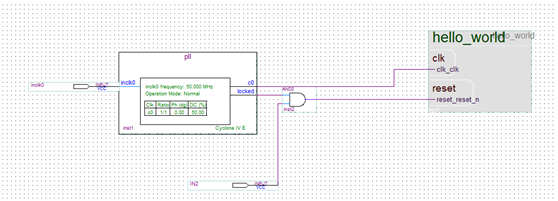

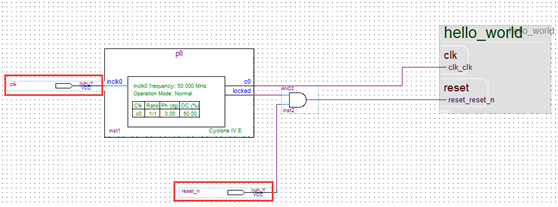

- 连接、添加引脚

双击打开Symbol对话框,在Name中and2,添加与门。

点击选择要添加引脚的模块,右击,选择generate pins for symbol ports。

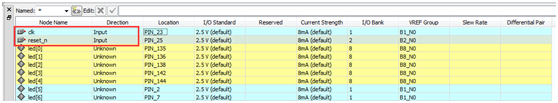

对引脚进行重命名,如下所示:

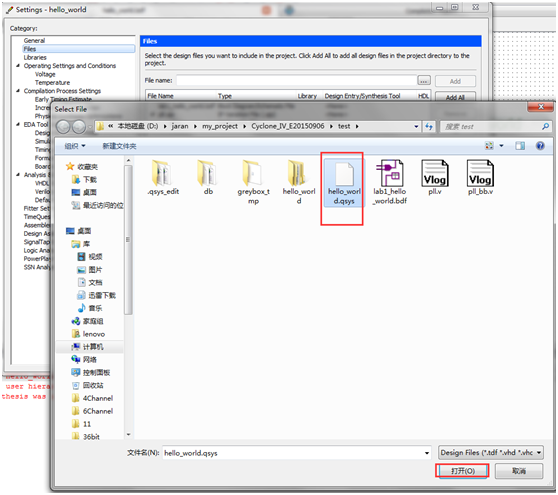

- 单击 Project -> Add/Remove Files in Project…,单击File name后面的浏览按钮,选择.qsys文件,单击Add将其添加进来,然后单击OK。

- 配置引脚

首先,进行编译

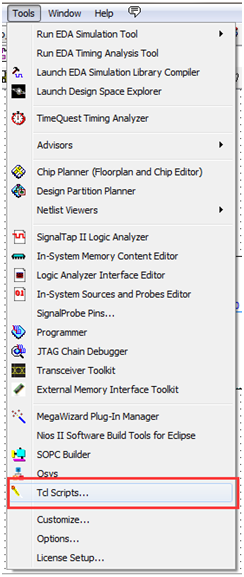

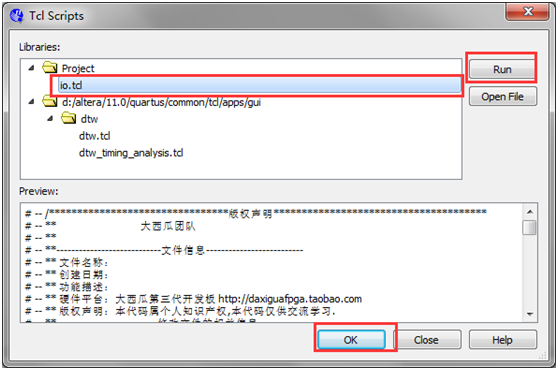

,然后采用脚本文件进行配置,toolsàtcl scripts;

,然后采用脚本文件进行配置,toolsàtcl scripts;

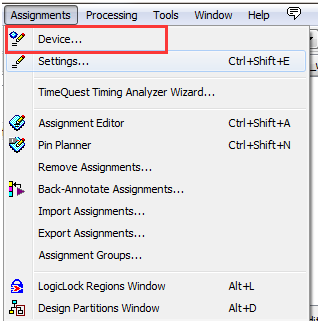

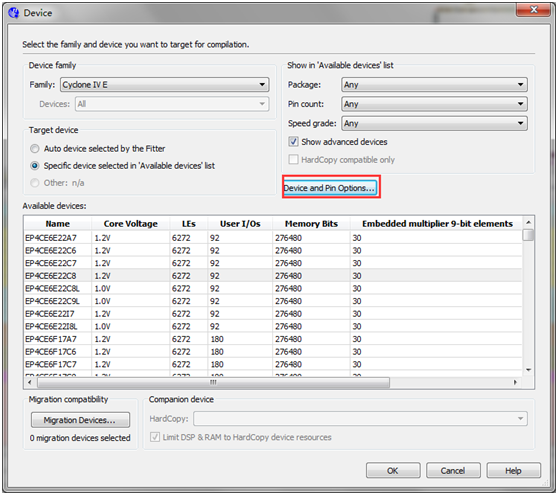

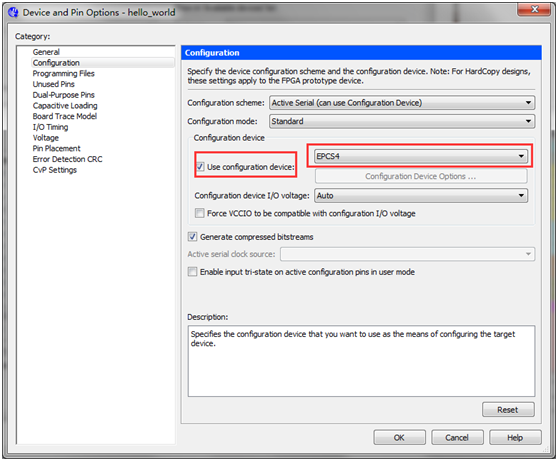

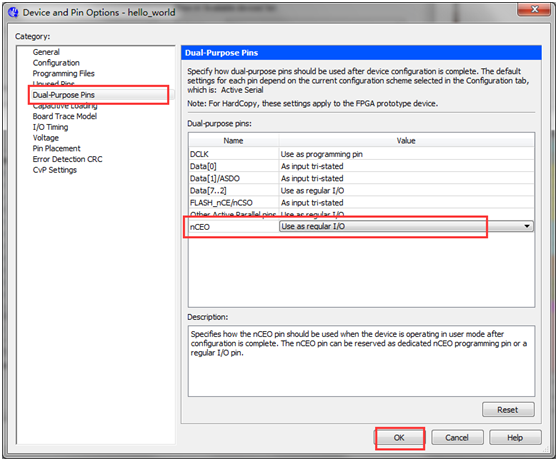

- 设置工程参数

设置AS配置器件EPCS4

设置双用引脚;

- 综合

,由于时间较长,请耐心等待。

,由于时间较长,请耐心等待。

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

nios II--实验1——hello_world硬件部分的更多相关文章

- FPGA回忆记事(一):基于Nios II的LED实验

实验一:基于Nios II的LED实验 一. 创建Quartus II工程 1.打开Quartus II环境.开始->程序->Altera->Quartus II 9.1. 2 ...

- 初探NIOS II之hello_world

平台背景: 操作系统:win7 64bit 开发板:DE2-115 Quartus ii:15.0及配套的NIOS ii开发平台 一.硬件系统的建立 1.在Quartus里新建工程,这是很基本的就不 ...

- nios II--实验1——hello_world软件部分

hello_world 软件开发 首先,在硬件工程文件夹里面新建一个software的文件夹用于放置软件部分:打开toolsàNios II 11.0 Software Build Tools for ...

- 给NIOS II CPU添加一颗澎湃的心——sysclk的使用

给NIOS II CPU添加一颗澎湃的心——系统时钟的使用 本实验介绍如何在Qsys中添加一个定时器作为NIOS II的心跳定时器,并在NIOS II中软件编程使用该定时器. 将上一个实验watchd ...

- nios II--实验6——串口硬件部分

串口 硬件开发 新建原理图 打开Quartus II 11.0,新建一个工程,File -> New Project Wizard…,忽略Introduction,之间单击 Next> 进 ...

- nios II--实验5——定时器硬件部分

定时器 硬件开发 新建原理图 打开Quartus II 11.0,新建一个工程,File -> New Project Wizard…,忽略Introduction,之间单击 Next> ...

- 【推荐图书】+ 基于Nios II的嵌入式SoPC系统设计与Verilog开发实例+C#入门经典等

[推荐图书]+ 基于Nios II的嵌入式SoPC系统设计与Verilog开发实例+C#入门经典等 3赞 发表于 2016/7/4 21:14:12 阅读(1921) 评论(3) 初次接触FPGA,到 ...

- Nios II 系统时钟timestamp的应用

在用Nios II做外设时序驱动的时候,经常会用延时函数.有时会常使用某个FPGA芯片和时钟,比如笔者一直使用的芯片是cyclone系列 EP2C35F484C8N,PLL输入SOPC时钟是50M.因 ...

- nios II--实验2——led硬件部分

Led 硬件开发 新建原理图 1.打开Quartus II 11.0,新建一个工程,File -> New Project Wizard…,忽略Introduction,之间单击 Next> ...

随机推荐

- SSH框架配置释义

创建一个bean, 依赖注入支持的不同注入方式及具体配置方法 属性注入 通过setter()方法注入bean的属性或者依赖对象.属性注入要求bean需要提供一个默认构造函数和对应的setter方法 ...

- Tomcat源码分析之—容器整体结构

Tomcat有多个容器组成,而Container也就是容器与Connecter连接器是Tomcat最核心的两个模块,Connecter连接器接收客户端的请求,并根据客户端的请求传递给Container ...

- 烂泥:学习ssh之ssh密钥随身携带

本文由秀依林枫提供友情赞助,首发于烂泥行天下 在上一篇文章<烂泥:学习ssh之ssh无密码登陆>中,我们讲解了如何使用ssh密钥,免密码登陆服务器. 这篇文章我们再来讲解,如何把已经生成的 ...

- php模拟飞鸽传输协议,代码实现向飞鸽发送消息

飞鸽传书协议:1:23149:riverlet:127.0.0.1:\x20:balabalabalabala版本号:包编号:发送者姓名:发送者主机名:命令字:附加信息(消息内容) <?php ...

- MAC OSX通过Terminal命令行控制蓝牙状态开关

defaults write /Library/Preferences/com.apple.Bluetooth.plist ControllerPowerState 0 #关闭蓝牙服务 default ...

- Ubuntu14.02.2下安装JDK并配置Jetty服务器

首先第一步先取得JDK的安装文件,由于我的系统是64位的,所以安装包是jdk-7u80-linux-x64.gz 上传到unbuntu服务器下 执行tar -xvf jdk-7u80-linux-x6 ...

- ViewPager+Fragment再探:和TAB滑动条一起三者结合

Fragment前篇: <Android Fragment初探:静态Fragment组成Activity> ViewPager前篇: <Android ViewPager初探:让页面 ...

- 阻塞通信之Socket编程

Socket通信,主要是基于TCP协议的通信.本文从Socket通信(代码实现).多线程并发.以及TCP协议相关原理方面 介绍 阻塞Socket通信一些知识. 本文从服务器端的视角,以“Echo Se ...

- 三维网格去噪算法(L0 Minimization)

[He et al. 2013]文章提出了一种基于L0范数最小化的三角网格去噪算法.该思想最初是由[Xu et al. 2011]提出并应用于图像平滑,假设c为图像像素的颜色向量,▽c为颜色向量的梯度 ...

- Codeforces 410C.Team[构造]

C. Team time limit per test 1 second memory limit per test 256 megabytes input standard input output ...