基于AHB_BUS的eFlash控制器设计-软硬件系统设计

eFlash软硬件系统设计

- 软硬件划分

- 划分好软硬件之后,IP暴露给软件的寄存器和时序如何?

- 文档体系:详细介绍eflash控制器的设计文档

- RTL代码编写:详细介绍eflash控制器的RTL代码

1.文档体系

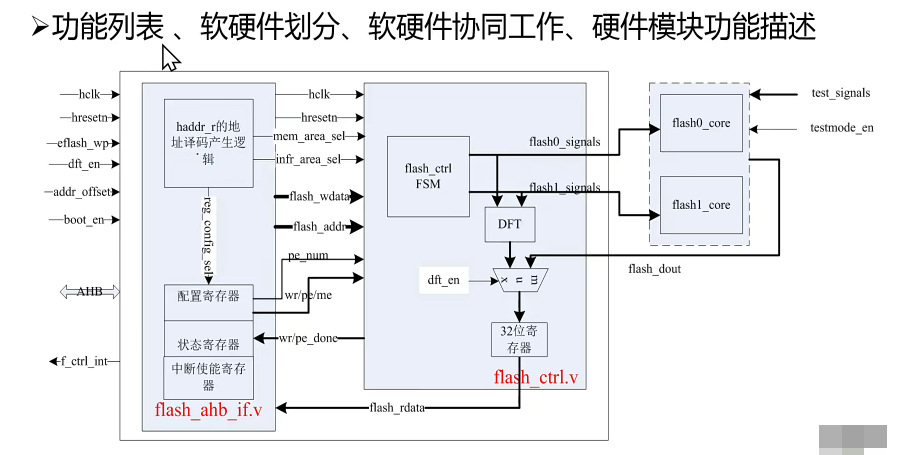

1.1 架构设计文档

- 配置寄存器 -- CPU要写,需要进行读写擦操作,需要配置相应的寄存器,产生wr/pe/me信号

- pe_num -- 擦除哪一页,从配置寄存器中

- 状态寄存器 -- CPU要读,产生中断(interrupt)的时候CPU会读取状态寄存器

- 中断使能寄存器 -- CPU要写,CPU决定是不是能产生中断

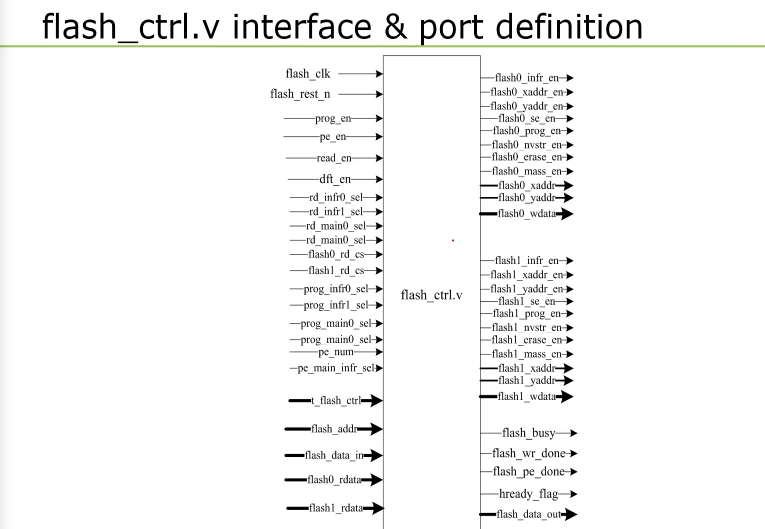

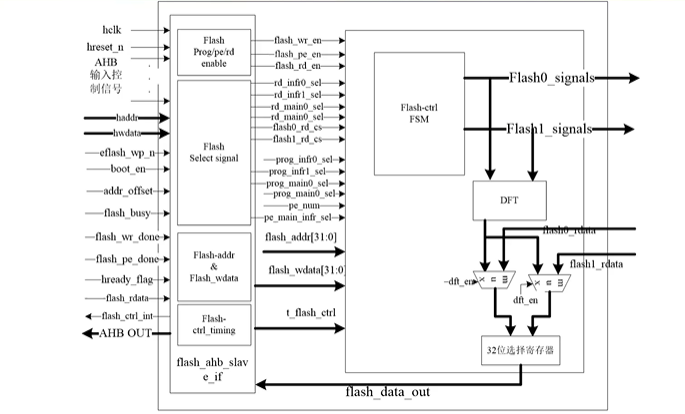

flash_ctrl.v输入 - flash_clk和flash_rest_en

- prog_en/pe_en/read_en/dft_en -- 操作指令

- 选择flash0或者flash1,选择information block或者main block

- 页擦需要知道pe_num -- 9bit

- t_flash_ctrl -- timing控制信号

- flash_addr和flash_data_in -- prog操作用到的的信号

- flash0_rdata/flash1_rdata -- read信号

flash_ctrl.v输出信号 - infr/xe/ye/se/prog/nvstr/erase/mass1/xadr/yadr/wdata -- 信号

- flash_busy -- 返回给状态寄存器

- flash_wr_done/flash_pe_done -- 返回给状态寄存器

- hready_flag -- 读的时候,通过hready_flag拉低延迟周期,达到读时间之后hready_flag拉高

- flash_data_out

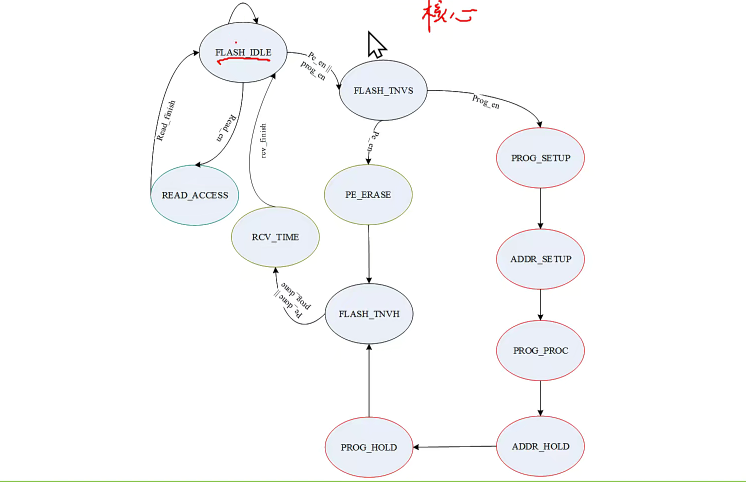

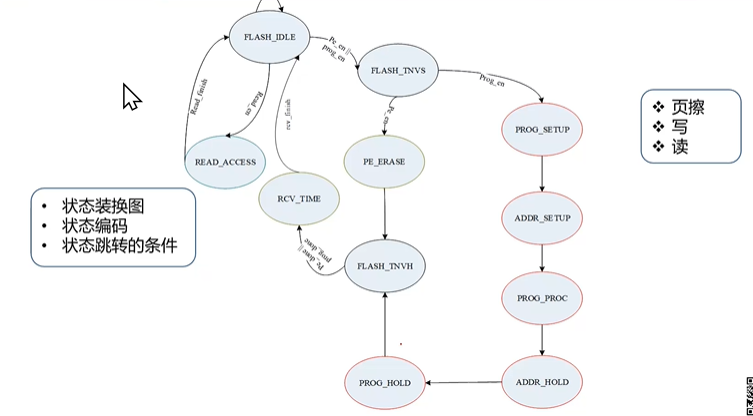

状态机

- 初始状态 -- FLASH_IDLE

- read_en起来之后 -- 进入readg_access,将xadr/yadr/xe/ye/se/infren等待准备好之后,读取数据,保存到寄存器中;在这个状态等待一定的时间,然后来read_finish信号,将上述信号拉低,读取结束;等待的时间一般超过read_access time(24ns)

- pe_en/prog_en都需要nvstr信号,都需要经过flash_nvstr状态,满足nvstr的建立时间之后,进入下一个状态,pe_en进入pe_erase状态;prog_en进入prog_setup状态

- pe_erase状态结束之后,进入flash_tnvh状态,之后进入recover_time状态

- 状态机就是时序图的翻译,其中的时间通过计数器计算时钟周期的个数进行控制

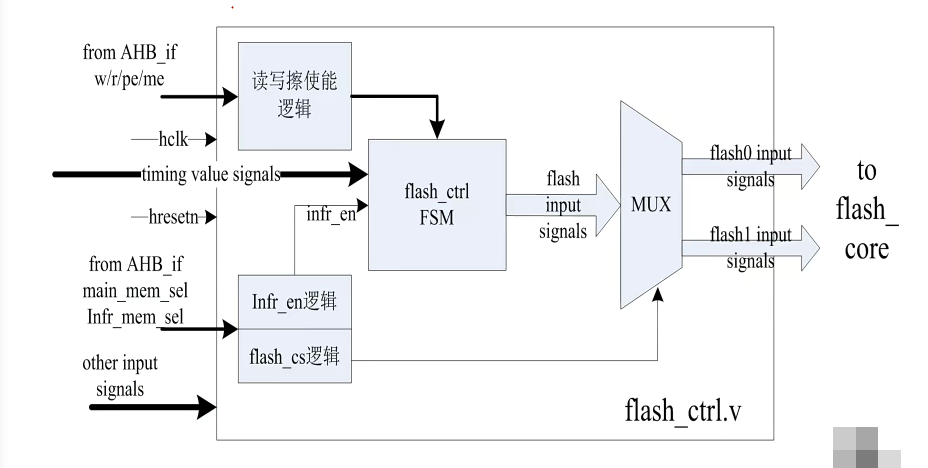

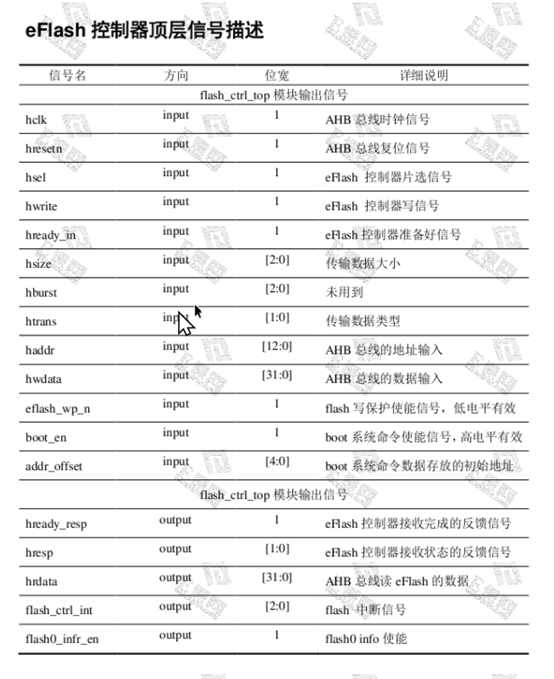

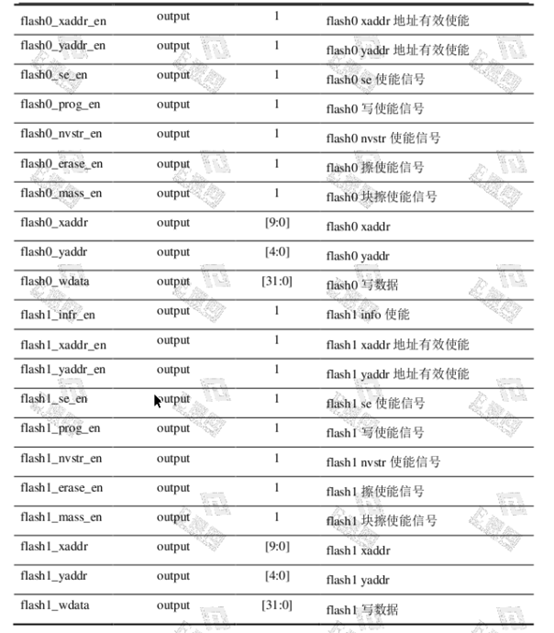

1.2 微架构设计文档

- 功能框图详细

- 各个模块详细描述:模块框图,信号描述,模块功能定义

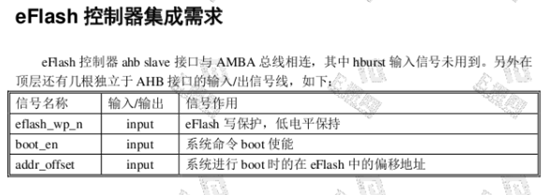

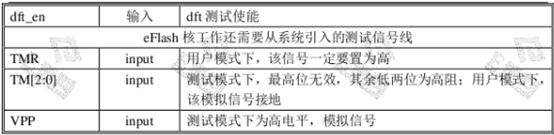

1.3 集成需求文档

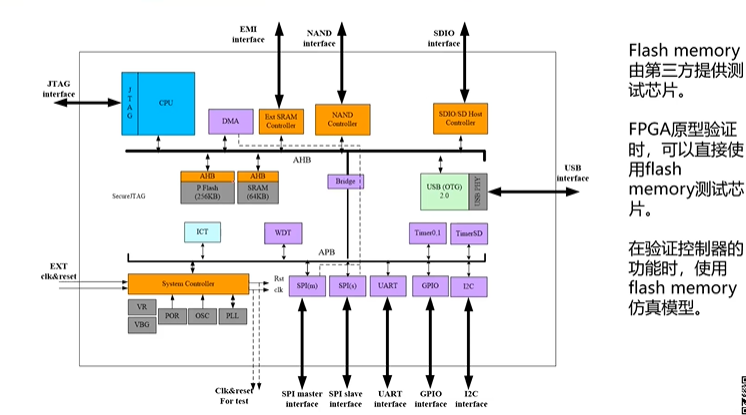

2. Flash在SoC中的作用

- PFlash是由代工厂进行提供的,SoC的GDS(其中预留了PFlash的空间)和Flash在代工厂进行merge

- 在进行Netlist测试或者FPGA测试,PFlash本身不是以软核的方式提供的,是以GDS文件提供的形式,在进行FPGA测试的时候PFlash是没有的,FlashC与真实的Flash颗粒进行交互,可以通过FPGA测试

- PFlash -- program Flash,存储驱动和boot程序,CPU上电之后需要执行的程序

3. 3Flash在SoC系统中的偏移地址

- PFlash在所有IP中排在首位,其首地址是0x0000 0000,因为其中有boot程序所以放在第一IP

- PFlash_reg -- 寄存器空间pe和prog操作,擦除的地址和写的地址和数据存储在寄存器中,需要什么需要配置到寄存器中,就用使能信号进行控制

- CPU在上电之后,会访问0地址,所以要进行地址offset,将访问地址offset到boot区间,进行boot

- flash烧写bootloader时间较长,而且几乎不会变化,所以在出厂的时候就烧录好了

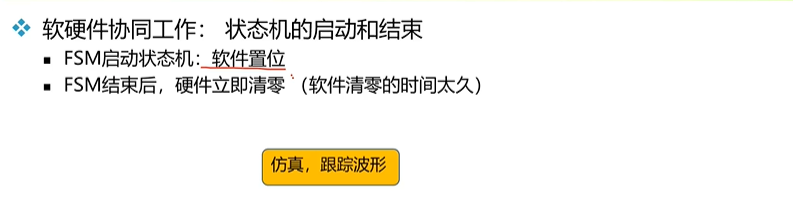

4.FSM:软件置位(置为1),硬件清零(置为0)

- 芯片是硬件执行一些指令,驱动Flash执行读写擦的操作

- 启动状态机的时候需要软件进行一些寄存器配置,然后发出启动状态机的信号启动状态机

- CPU如果要进行写操作,就将写使能寄存器写prog_en_r入1(其他时序寄存器配置完成),然后将这个信号1给Flash_ctrl,进行启动状态机,状态机完成一轮任务之后,如果不清除prog_en_r信号(置为0),则状态机一直识别其为1,就会一直运行状态机,在执行状态机完成一轮之后,需要清除prog_en_r

- 如果使用CPU进行prog_en_r清0,但是CPU不知道状态器什么时候接收到prog_en_r信号;如果想要CPU进行清0操作,需要让CPU等待FSM收到prog_en_r,就增加了一道时序约束

- 硬件清0,状态机启动之后,就任务是接收到了prog_en_r,状态机在接收到操作信号之后,可以进行内部存储操作使能信号,就不需要prog_en_r,可以将其清除;还可以在状态机运行后期,在从Trcv状态向IDLE状态跳转的时候,将prog_en_r清0,当FSM处于IDLE状态之后看到prog_en_r已经置为0了,就不会继续进行工作,知道CPU开启下一轮操作信号来

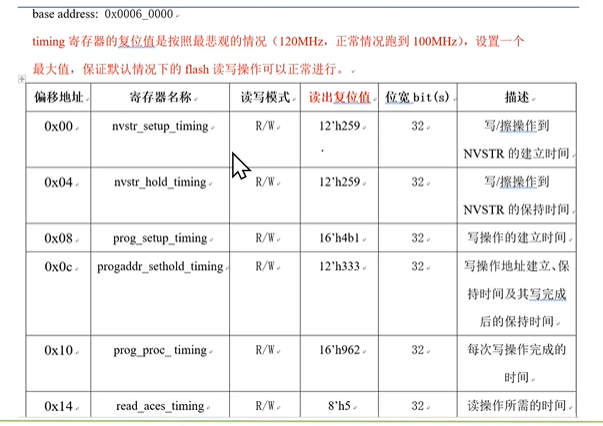

5.时序配置寄存器的默认值

- 按照最悲观的值配置时序寄存器

- 120MHz,一个周期是8.33ns,5000ns/8.33 = 600.2--> 601 -->十六进制259

- 读出复位值就是counter的计数值

6. 状态寄存器(硬件置位,软件清0)

- 任务完成后,IP产生中断给到CPU,CPU通过中断服务程序,处理响应中断

- 任务完成之后,IP返回的中断信号会被拉高,CPU在看到中断信号拉高之后,需要进入中断服务程序响应中断,CPU在处理完中断之后,需要将中断信号拉低,如果不处理中断信号,中断信号一直拉高,CPU一直处于处理中断的状态中,导致CPU死锁,不能处理其他业务,处理中断信号不能通过硬件,因为硬件不知道CPU何时处理完了中断,所以要通过CPU使用软件的方式处理中断信号,当CPU处理完成中断之后,将状态寄存器清0,中断消失

- 写1清0:当CPU向状态寄存器写入1的时候(并不是寄存器的值是1),就将状态寄存器清0

7.寄存器

- 在进行DFT的时候,将Flash颗粒bypass掉

基于AHB_BUS的eFlash控制器设计-软硬件系统设计的更多相关文章

- 基于FPGA的XPT2046触摸控制器设计

基于FPGA的XPT2046触摸控制器设计 小梅哥编写,未经许可,文章内容和所涉及代码不得用于其他商业销售的板卡 本实例所涉及代码均可通过向 xiaomeige_fpga@foxmail.com 发 ...

- 基于FPGA的SPI FLASH控制器设计

1.SPI FLASH的基本特征 本文实现用FPGA来设计SPI FLASH,FLASH型号为W25Q128BV.支持3种通信方式,SPI.Dual SPI和Quad SPI.FLASH的存储单元无法 ...

- 2014.04.28基于CPLD的LCOS场序彩色视频控制器设计

基于CPLD的LCOS场序彩色视频控制器设计 作者:宋丹娜,代永平,刘艳艳,商广辉 发表刊物:液晶与显示,2009 学习时间:2014.04.28 文章讲述了-- (和上一篇论文有些相似之处) 1. ...

- 基于JAVA WEB技术旅游服务网站系统设计与实现网上程序代写

基于JAVA WEB技术旅游服务网站系统设计与实现网上程序代写 专业程序代写服务(QQ:928900200) 随着社会的进步.服务行业的服务水平不断发展与提高,宾馆.酒店.旅游等服务行业的信息量和工作 ...

- 毕业论文系列之基于WiFi的智能农业大棚管控系统设计代码

#include <dht11.h>//dht11库 #include <MsTimer2.h> //定时器库的 头文件 #include < ...

- 基于cocos2d-x的游戏框架设计——李成

视频:http://v.youku.com/v_show/id_XMzc5ODUyMTI4.html?f=17330006 网易科技讯 3月31日,第四届CocoaChina开发者大会暨Cocos2d ...

- 基于PCIe的高速接口设计

基于PCIe的高速接口设计 由 judyzhong 于 星期四, 03/03/2016 - 13:49 发表 作者:李晓宁,姚远程,秦明伟 2016年微型机与应用第1期 摘要:PCIe总线是第三代I/ ...

- 基于SEDA的异步框架设计与实现

基于SEDA的异步框架设计与实现 二.为什么使用SEDA 目前,面对并发环境,主流互联网服务器编程模型有两种:多线程模型以及事件驱动模型.但是这两个模型都不足以解决这个问题.我们来首先看一下这两种编程 ...

- 基于DDD的微服务设计和开发实战

你是否还在为微服务应该拆多小而争论不休?到底如何才能设计出收放自如的微服务?怎样才能保证业务领域模型与代码模型的一致性?或许本文能帮你找到答案. 本文是基于 DDD 的微服务设计和开发实战篇,通过借鉴 ...

- 走进MEasy的世界:基于STM32MP1的IOT参考设计

前言:在万物互联快速发展的趋势下,板卡处理器性能.内存大小.接口外设等都是人们非常关心的硬件参数,但是如何让硬件的作用实现它的功能最大化,一套完善的软件支持尤为重要. 背景:随着HTML5技术的发展, ...

随机推荐

- Halo新年灯笼-halonewyaer

title: Halo新年灯笼 date: 2021-12-29 15:49:34.665 updated: 2022-03-10 16:00:53.189 url: https://www.yby6 ...

- C#新鲜面试题出炉(2024)

总所周知 C#这门语言 没有Java的八股文,所以面试题一般都是问的业务, 那么对于新手来讲,最起码也要会一些基础性问题, 以下就是包含C# 和sqlserver几个常见的面试题 1) Dele ...

- P1990-覆盖墙壁

分情况: \[\left\{ \begin{aligned} & 条形 \left\{ \begin{aligned} 横着\\ 竖着\\ \end{aligned}\right. \\ &a ...

- C++ 学习宝藏网站分享

C++ 学习宝藏网站分享 1. C++ 在线参考手册 Cppreference https://zh.cppreference.com C++ 开发者必备的在线参考手册,是我最常访问的 C++ 网站之 ...

- Spring系列:基于Spring-Jdbc实现事务

目录 一.事务基本概念 二.编程式事务 三.声明式事务 前期准备 四.基于注解的声明式事务 @Transactional注解标识的位置 事务属性:只读 事务属性:超时 事务属性:回滚策略 事务属性:隔 ...

- 实时媒体AI,打破内容创作天花板,加速视频创新

摘要:互联网视频经过几代发展,用户体验快速升级,对创新玩法.互动性要求越来越高.那如何解决这些问题? 媒体AI,是行业共识.华为云提供云原生实时媒体AI能力,联合伙伴打造AI算法开放生态市场,加速视频 ...

- 毕昇 JDK:为啥是ARM 上超好用的 JDK

摘要:毕昇 JDK 是华为基于 OpenJDK 定制的开源版本,是一款高性能.可用于生产环境的 OpenJDK 发行版. 本文分享自华为云社区<[云驻共创]毕昇 JDK:"传奇再现&q ...

- npm install过程中遇到typings deprecated的warning该怎么处理

摘要:在项目里进行npm install操作的时候,发现typings.json文件里的一些定义文件爆出了已经弃用的警告,怎么办? 本文分享自华为云社区<npm install过程中遇到typi ...

- update 没有索引导致业务崩了,老板骂了一个小时

摘要:有天,一朋友在线上执行一条 update 语句修改数据库数据的时候,where 条件没有带上索引,导致业务直接崩了,被老板教训了一波. 本文分享自华为云社区<update 没有索引,会锁全 ...

- Solon:Hello world!

Solon:Hello world! (一)新建一个 maven 空项目 (二)添加 maven 引用 <dependency> <groupId>org.noear</ ...