基于Verilog的简单FIFO读写实验

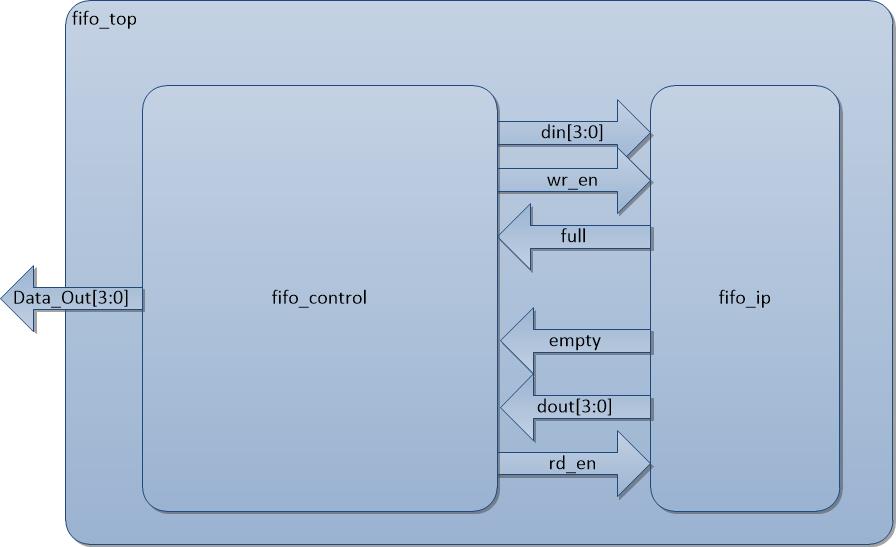

一、模块框图及基本思路

fifo_ip:ISE生成的IP

fifo_control:在fifo未满情况下不断写入递增的四位数,每隔1s读出一个数据驱动Led显示

fifo_top:前两个模块的组合

二、软件部分

fifo_control:

module fifo_control(

clk,rst,

Data_Out,

din,wr_en,full,

dout,rd_en,empty

);

input clk,rst;

output[:] Data_Out;

output [:] din; //相对fifo来说是输入

input [:] dout; //相对fifo来说是输出

output wr_en,rd_en;

input full,empty; /****************定时部分*********************/

localparam T1S=50_000_000-;

reg[:] Count_1s;

always @(posedge clk or posedge rst)

begin

if(rst)

begin

Count_1s<='d0;

end

else if(Count_1s==T1S)

Count_1s<='d0;

else if(!isCount)

Count_1s<='d0;

else Count_1s<=Count_1s+'b1;

end

/*****************FIFO写入部分********************/

reg [:] i;

reg wr_en;

reg [:]din; always @(posedge clk or posedge rst)

if(rst)

begin

din<='d0;

i<='d0;

wr_en<='b0;

end

else if(!full)

case(i)

'd0:begin din<=din+1'b1;i<=i+'b1;wr_en<=1'b1;end

'd1:begin i<=2'd0;wr_en<='b0;end

endcase

/*******************FIFO读出部分***************************/

reg[:] Data_Out_r;

wire [:] dout;

reg isCount;

reg [:]j;

reg rd_en; always @(posedge clk or posedge rst)

if(rst)

begin

Data_Out_r<='d0;

j<='d0;

isCount<='b0;

rd_en<='b0;

end

else if(!empty)

case(j)

'd0:if(Count_1s==T1S) begin j<=j+1'b1;isCount<='b0;rd_en<=1'b1; end

else isCount<='b1;

'd1:begin rd_en<=1'b0;j<=j+'b1;end

'd2:begin Data_Out_r<=dout;j<=3'd0; end

endcase

assign Data_Out=Data_Out_r; /****************************************************/ endmodule

fifo_top:

module fifo_top(

clk,RSTn,

Data_Out

);

input clk,RSTn;

output[:] Data_Out; wire [:]din;

wire [:]dout;

wire wr_en,rd_en,full,empty; /****************************************************/

fifo_ip U0 (

.clk(clk), // input clk

.rst(!RSTn), // input rst

.din(din), // input [3 : 0] din

.wr_en(wr_en), // input wr_en

.rd_en(rd_en), // input rd_en

.dout(dout), // output [3 : 0] dout

.full(full), // output full

.empty(empty) // output empty

);

/*********************************************************/

fifo_control U1 (

.clk(clk),

.rst(!RSTn),

.Data_Out(Data_Out),

.din(din),

.wr_en(wr_en),

.full(full),

.dout(dout),

.rd_en(rd_en),

.empty(empty)

); endmodule

三、硬件部分

黑金SPARTAN开发板

NET "clk" LOC = T8;

NET "RSTn" LOC = L3; NET "Data_Out[0]" LOC = P4;

NET "Data_Out[1]" LOC = N5;

NET "Data_Out[2]" LOC = P5;

NET "Data_Out[3]" LOC = M6;

基于Verilog的简单FIFO读写实验的更多相关文章

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- 基于Verilog的带FIFO输出缓冲的串口接收接口封装

一.模块框图及基本思路 rx_module:串口接收的核心模块,详细介绍请见“基于Verilog的串口接收实验” rx2fifo_module:rx_module与rx_fifo之间的控制模块,其功能 ...

- 基于Verilog HDL 各种实验

菜鸟做的的小实验链接汇总: 1.基于Verilog HDL 的数字时钟设计 2.乘法器 3.触发器(基本的SR触发器.同步触发器.D触发器) 4.基于Verilog HDL的ADC ...

- 基于AHB总线的master读写设计(Verilog)

一.AHB总线学习 1. AHB总线结构 如图所示,AHB总线系统利用中央多路选择机制实现主机与从机的互联问题.从图中可以看出,AHB总线结构主要可分为三部分:主机.从机.控制部分.控制部分由仲裁器. ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

- 基于modelsim-SE的简单仿真流程—上

基于modelsim-SE的简单仿真流程 编写RTL功能代码 要进行功能仿真,首先得用需要仿真的模块,也就是RTL功能代码,简称待测试的模块,该模块也就是在设计下载到FPGA的电路.一个电路模块想要有 ...

- berkerly db 中简单的读写操作(有一些C的 还有一些C++的)

最近在倒腾BDB,才发现自己确实在C++这一块能力很弱,看了一天的api文档,总算是把BDB的一些api之间的关系理清了,希望初学者要理清数据库基本知识中的环境,句柄,游标的基本概念,这样有助于你更好 ...

- 基于SMB协议的共享文件读写 博客分类: Java

基于SMB协议的共享文件读写 博客分类: Java 一.SMB协议 SMB协议是基于TCP-NETBIOS下的,一般端口使用为139,445. 服务器信息块(SMB)协议是一种IBM协议,用于在计 ...

随机推荐

- 51Nod 1085 背包问题 (01背包)

在N件物品取出若干件放在容量为W的背包里,每件物品的体积为W1,W2……Wn(Wi为整数),与之相对应的价值为P1,P2……Pn(Pi为整数).求背包能够容纳的最大价值. 收起 输入 第1行,2个 ...

- Oracle数据库管理----性能优化

https://blog.csdn.net/yzllz001/article/details/54848513 数据库访问优化法则 要正确的优化SQL,我们需要快速定位能性的瓶颈点,也就是说快速找 ...

- idea 报错 :error:java:Compilation failed:internal java compiler error

当使用Tomcat运行项目时报错 翻译一下是 错误:Java:编译失败:内部Java编译器错误 这样看来更不理解了 其实原因是Java的版本不一致 查看项目的jdk版本是否一致: file----pr ...

- Html 标签种类

Html 标签种类 自闭合标签与闭合标签 自闭合标签 <标签 /> 闭合标签 <标签></标签> 块级标签与行内标签 浏览器审查元素使用: (1) f12 查看每个 ...

- hadoop+kerberos常用运维命令

kerberos相关: kadmin.local //以超管身份进入kadmin kadmin //进入kadmin模式,需输入密码 kdb5_util create -r JENKIN.COM -s ...

- kvm键盘使用

在新建导向的时候最后一步之前,选择查看细节那里,在desplay的地方选择VNC server ,再在keyboard地方选择us-en,这下进入安装界面就可以了.

- Bumped!【最短路】(神坑

问题 B: Bumped! 时间限制: 1 Sec 内存限制: 128 MB 提交: 351 解决: 44 [提交] [状态] [命题人:admin] 题目描述 Peter returned fr ...

- Bytom 技术 FAQ

比原项目仓库: Github地址:https://github.com/Bytom/bytom Gitee地址:https://gitee.com/BytomBlockchain/bytom 1.如何 ...

- Bytom信息上链教程

比原项目仓库: Github地址:https://github.com/Bytom/bytom Gitee地址:https://gitee.com/BytomBlockchain/bytom 用比原链 ...

- js同步、异步、回调的执行顺序以及闭包的理解

首先,记住同步第一.异步第二.回调最末的口诀 公式表达:同步=>异步=>回调 看一道经典的面试题: for (var i = 0; i < 5; i++) { setTimeout( ...