基于Vivado调用ROM IP core设计DDS

DDS直接数字式频率合成器(Direct Digital Synthesizer)

下面是使用MATLAB生成正弦波、三角波、方波的代码,直接使用即可。

t=:*pi/^:*pi

y=0.5*sin(t)+0.5;

r=ceil(y*(^-)); %将小数转换为整数,ceil是向上取整。

fid = fopen('sin.coe','w'); %写到sin.coe文件,用来初始化sin_rom

fprintf(fid,'MEMORY_INITIALIZATION_RADIX=10;\n');

fprintf(fid,'MEMORY_INITIALIZATION_VECTOR=\n');

for i = ::^

fprintf(fid,'%d',r(i));

if i==^

fprintf(fid,';');

else

fprintf(fid,',');

end

if i%==

fprintf(fid,'\n');

end

end

fclose(fid);

t=::^;

y=(t<=);

r=ceil(y*(^-));

fid = fopen('square.coe','w'); %写到square.coe,用来初始化rom_square

fprintf(fid,'MEMORY_INITIALIZATION_RADIX=10;\n');

fprintf(fid,'MEMORY_INITIALIZATION_VECTOR=\n');

for i = ::^

fprintf(fid,'%d',r(i));

if i==^

fprintf(fid,';');

else

fprintf(fid,',');

end

if i%==

fprintf(fid,'\n');

end

end

fclose(fid);

t=::^;

y=[0.5:0.5/:-0.5/, -0.5/:-0.5/:, 0.5/:0.5/:0.5];

r=ceil(y*(^-));

fid = fopen('triangular.coe','w'); %写到triangular.coe,初始化三角波rom

fprintf(fid,'MEMORY_INITIALIZATION_RADIX=10;\n');

fprintf(fid,'MEMORY_INITIALIZATION_VECTOR=\n');

for i = ::^

fprintf(fid,'%d',r(i));

if i==^

fprintf(fid,';');

else

fprintf(fid,',');

end

if i%==

fprintf(fid,'\n');

end

end

fclose(fid);

设计DDS的核心就是调用IP ROM,vivado调用ROM的方法和ISE相类似,都是加载.coe文件,我这里特地做笔记,以防忘记。

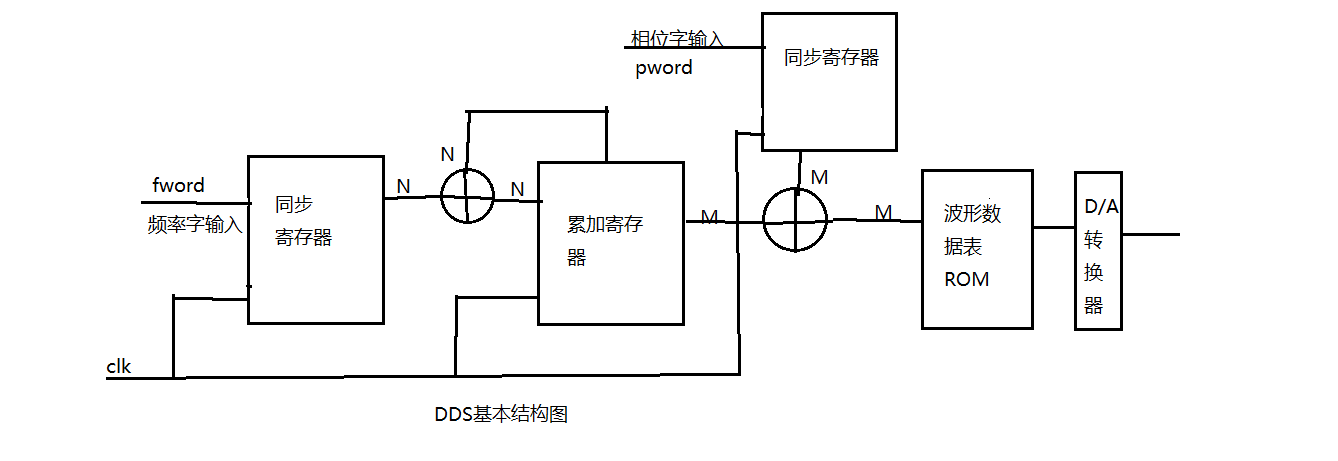

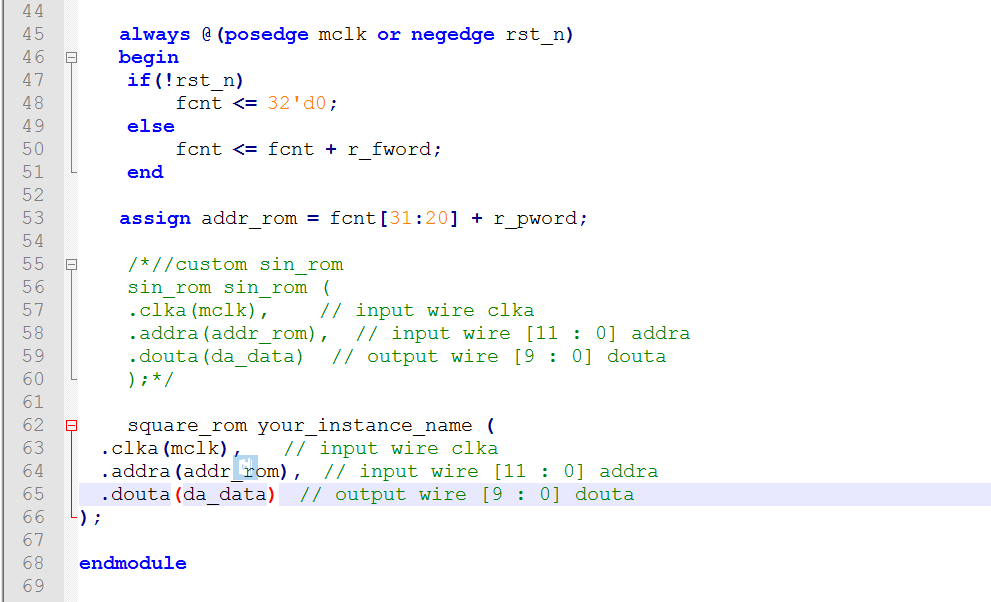

这是DDS的原理图,DDS并没有像它的名字一样说的那么玄乎,它的核心便是控制频率的fword字输入,和相位字pword输入,最后调用IP核查找表即可,代码也十分简单,下面给出DDS design代码。

module DDS(

input mclk,

input rst_n,

input [:]fword,//frequency control

input [:]pword,//phase control output [:]da_data

); reg [:]r_fword;

reg [:]r_pword;

reg [:]fcnt; wire [:]addr_rom; //同步寄存器

always @(posedge mclk)

begin

r_fword <= fword;

r_pword <= pword;

end always @(posedge mclk or negedge rst_n)

begin

if(!rst_n)

fcnt <= 'd0;

else

fcnt <= fcnt + r_fword;

end assign addr_rom = fcnt[:] + r_pword; //custom sin_rom

sin_rom sin_rom (

.clka(mclk), // input wire clka

.addra(addr_rom), // input wire [11 : 0] addra

.douta(da_data) // output wire [9 : 0] douta

); endmodule

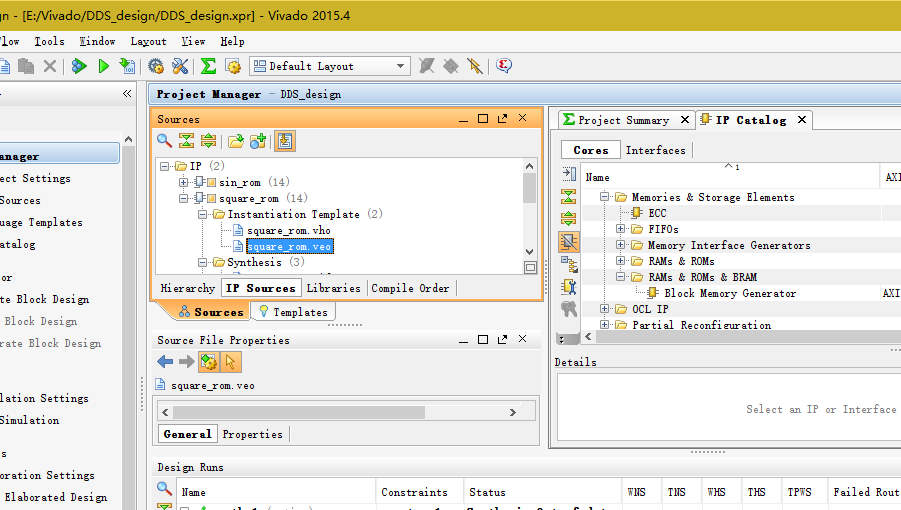

DDS_design

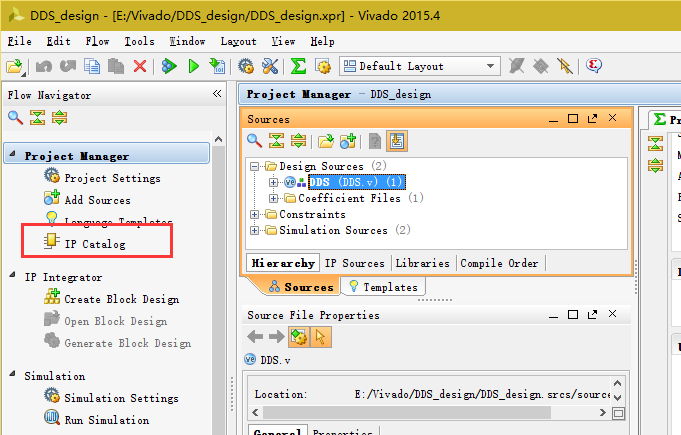

使用vivado调用IP核ROM教程如下

点击IP catalog

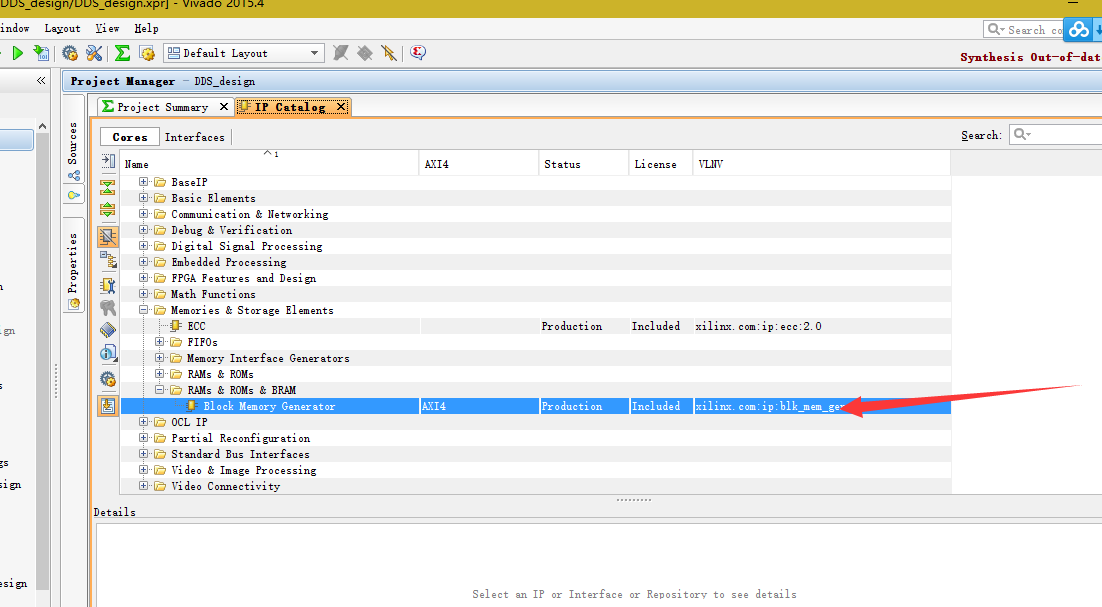

选择block memory,然后双击

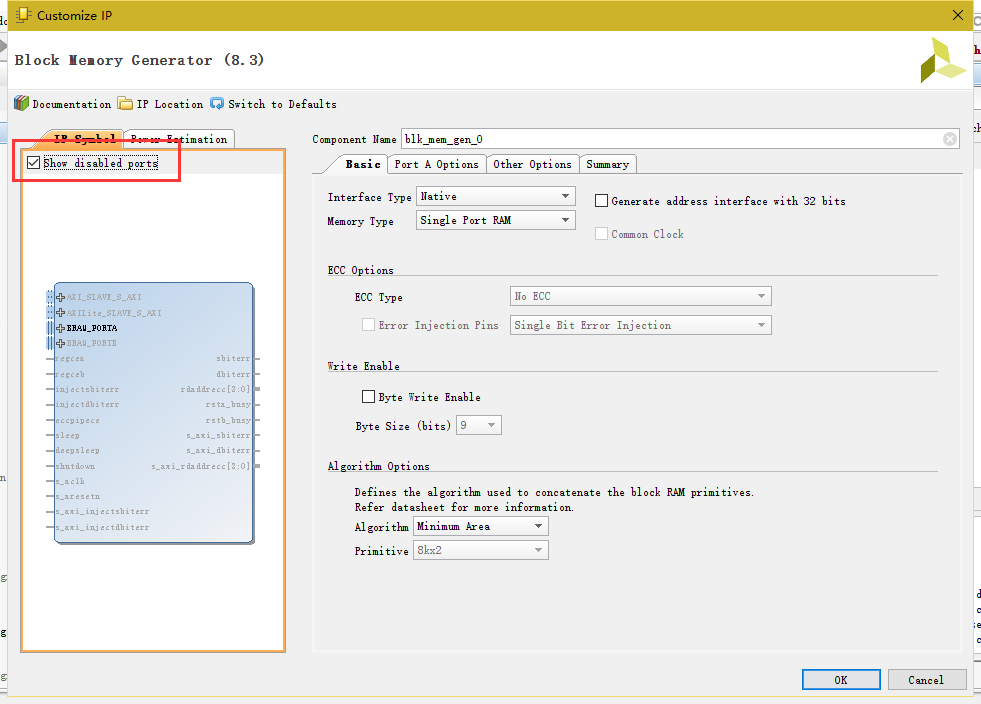

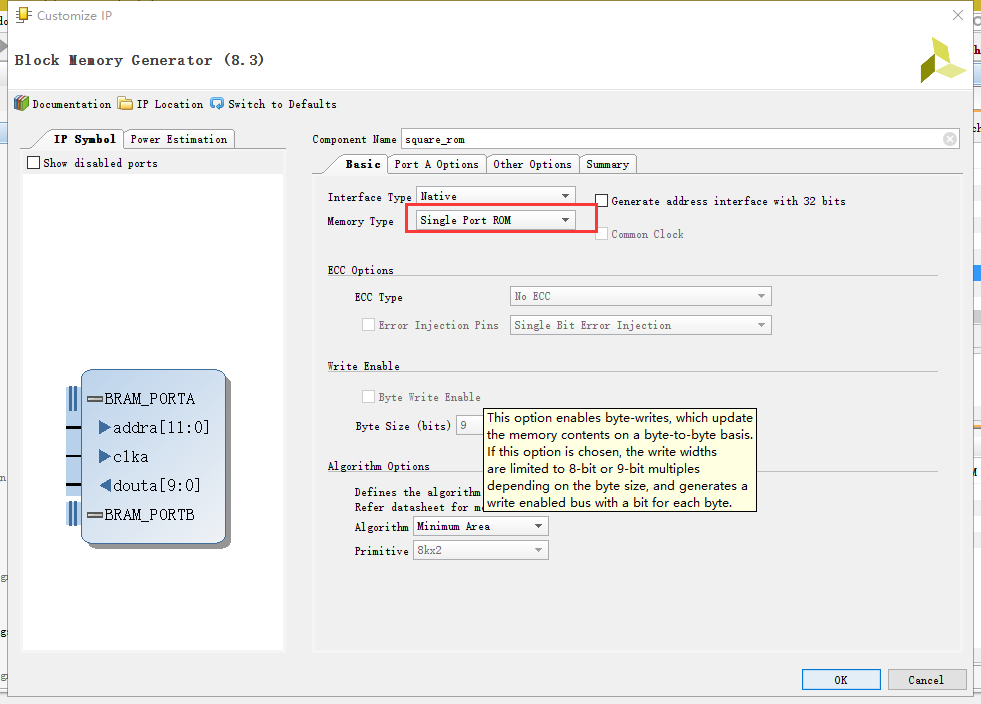

将show disabled ports 选项勾选掉

输入ROM名,我这里为了演示重新配置一个方波ROM,命名为square_rom

这里选择single ports ROM

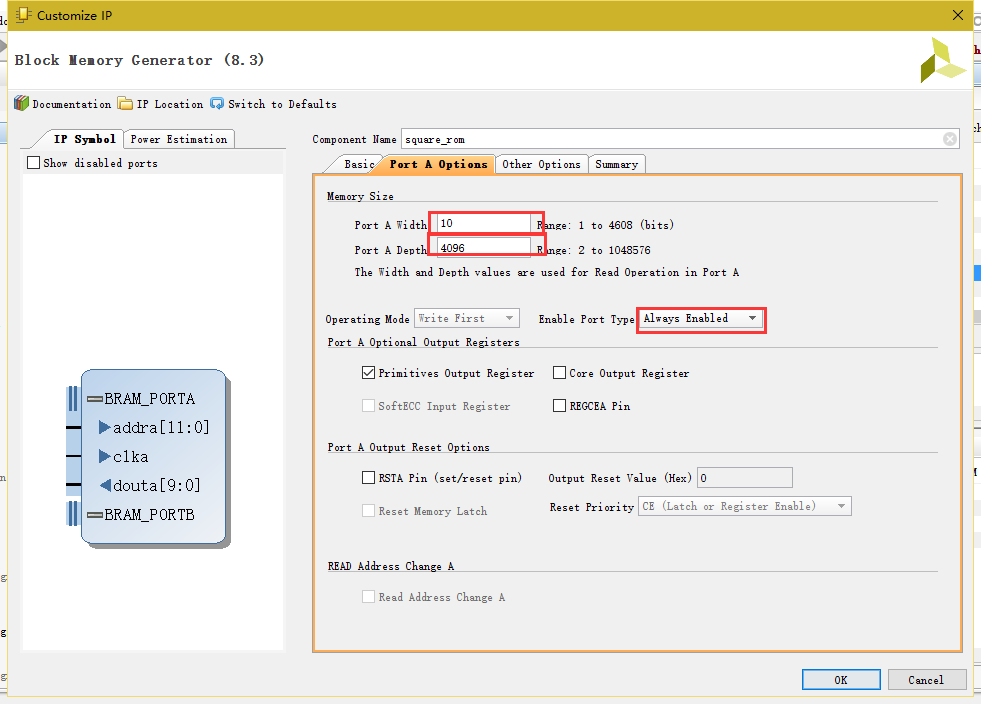

按如上图所示勾选参数,port width是数据宽度,我们根据代码要求设置为10位,

port width是数据深度,即有多少个这样的数据,我打开生成的square.coe文件可以清楚的看到一共有4096这样的数据。

always enable是ROM一直处于工作状态,不需要使能信号。

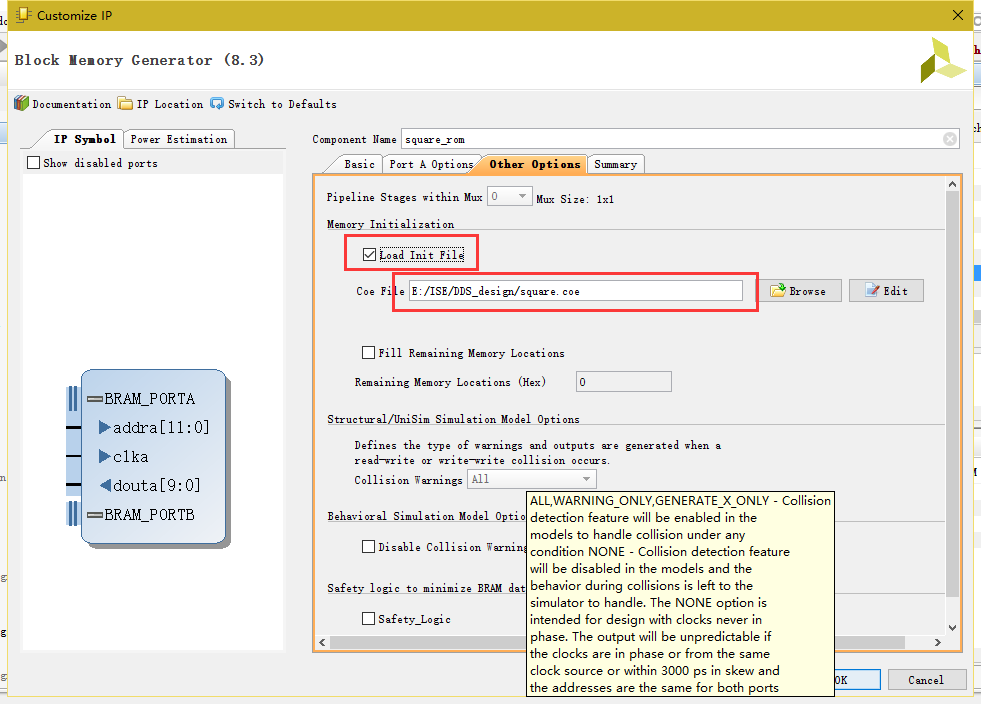

这里是加载.coe文件,勾选load init file 然后点击browse将刚才生成的square.coe文件加载到ROM中,最后点击OK。

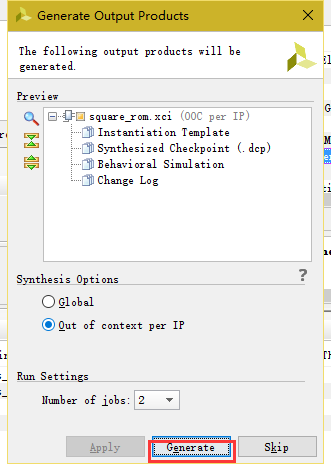

选择generate生成IP核

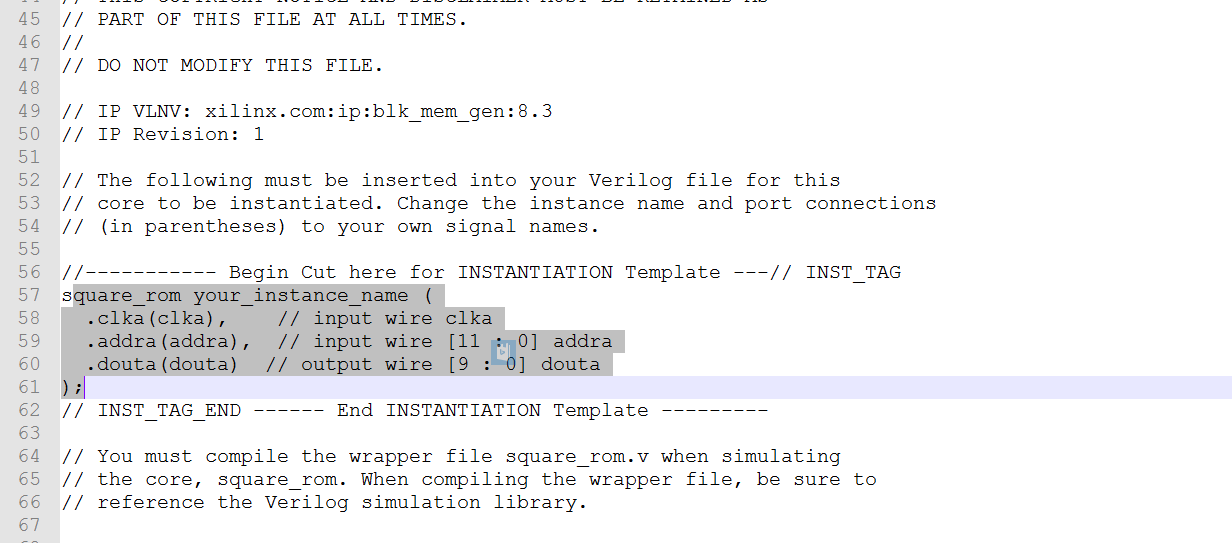

打开如图所示文件,

将生成的IP核实例化,即可

最后编写测试文件进行测试

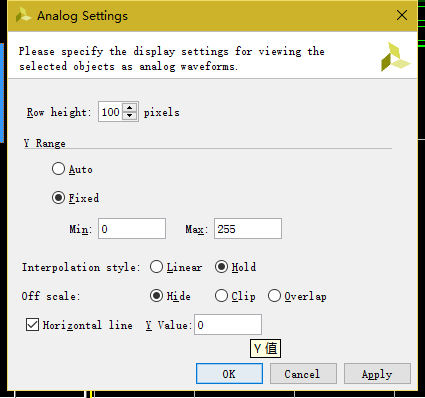

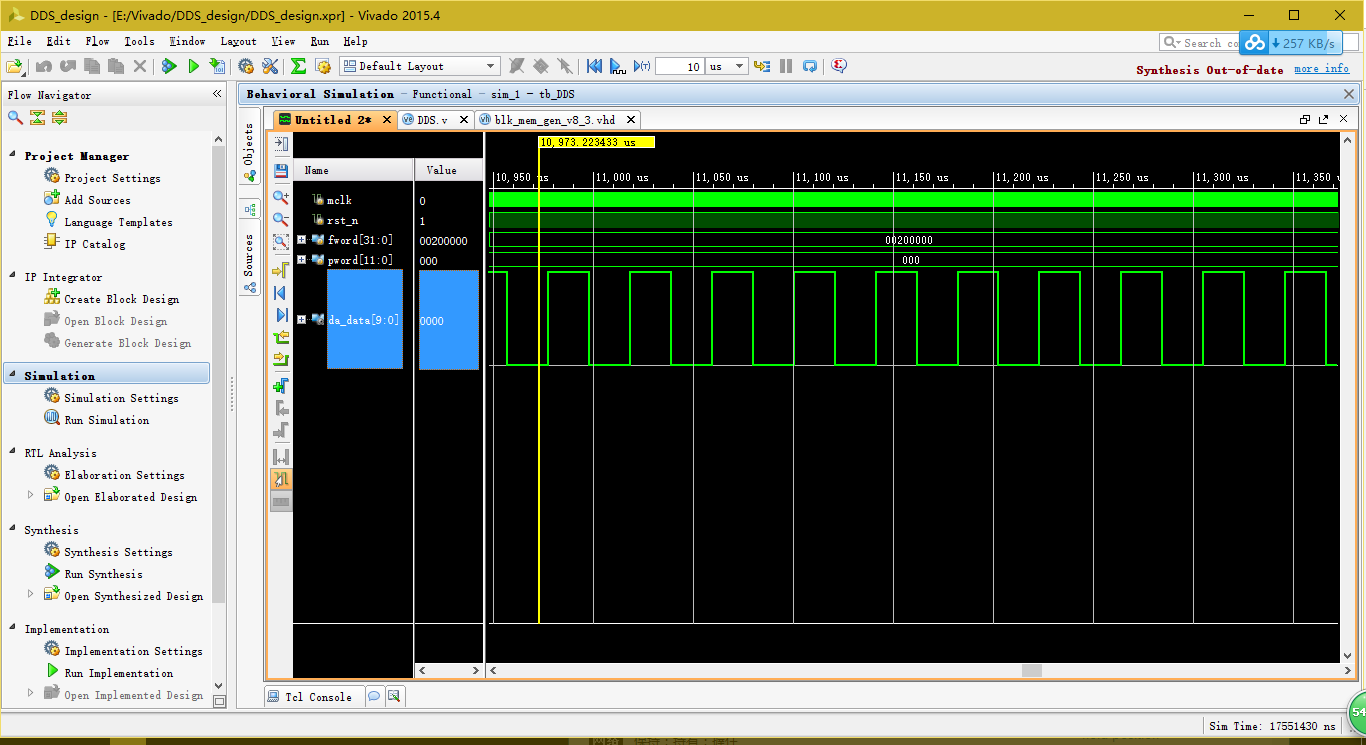

最后右键点击da_data选择wave style选择analog,将会看到模拟波形,但是有时候还是需要设置一下模拟波形的显示,同样右键点击da_data选择wave style选择analog setting,选择如下图所示参数。

最后便大功告成,即可得打方波的波形图

大家还可以按照这种方法将其他两种波形都做出来。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:NingHeChuan

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/6421360.html

基于Vivado调用ROM IP core设计DDS的更多相关文章

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core.通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- 基于ZigBee的家居控制系统的设计与应用

基于ZigBee的家居控制系统的设计与应用 PPT简介:http://pan.baidu.com/s/1i38PC6D 摘 要 智能家居是未来家居的发展方向,其利用先进的网络技术.计算机技术和无线通 ...

- 基于basys2驱动LCDQC12864B的verilog设计图片显示

话不多说先上图 前言 在做这个实验的时候在网上找了许多资料,都是关于使用单片机驱动LCD显示,确实用单片机驱动是要简单不少,记得在FPGA学习交流群里问问题的时候,被前辈指教,说给我最好的指教便是别在 ...

- IP包设计

IP包 IP核(Intellectual Property core)就是知识产权核或知识产权模块的意思,用于配置FPGA或其它硅芯片上的逻辑资源. 引用链接https://blog.csdn.net ...

- 使用matlab和ISE 创建并仿真ROM IP核

前言 本人想使用简单的中值滤波进行verilog相关算法的硬件实现,由于HDL设计软件不能直接处理图像,大部分过程都是可以将图像按照一定的顺序保存到TXT文档中,经过Modelsim仿真后,处理的数据 ...

- 基于Vivado的嵌入式开发 ——PS+PL实践

基于Vivado的嵌入式开发 ——PS走起 硬件平台:ZedBoard 开发工具:Vivado 2014.2 1.规划 废话不多说,依然是流水灯,这次是采用PS+PL实现. 功能依旧简单,目标是为了学 ...

随机推荐

- 平衡树初阶——AVL平衡二叉查找树+三大平衡树(Treap + Splay + SBT)模板【超详解】

平衡树初阶——AVL平衡二叉查找树 一.什么是二叉树 1. 什么是树. 计算机科学里面的树本质是一个树状图.树首先是一个有向无环图,由根节点指向子结点.但是不严格的说,我们也研究无向树.所谓无向树就是 ...

- 实现容器的底层技术 - 每天5分钟玩转 Docker 容器技术(30)

为了更好地理解容器的特性,本节我们将讨论容器的底层实现技术.cgroup 和 namespace 是最重要的两种技术.cgroup 实现资源限额, namespace 实现资源隔离. cgroup c ...

- 浅尝JavaScript document对象

document对象 每个载入浏览器的 HTML 文档都会成为 Document 对象.document 对象是HTML文档的根节点与所有其他节点(元素节点,文本节点,属性节点, 注释节点).Docu ...

- vijos1325 桐桐的糖果计划

Description 桐桐是一个快乐的小朋友,他生活中有许多许多好玩的事,让我们一起来看看吧-- 桐桐很喜欢吃棒棒糖.他家处在一大堆糖果店的附近. 但是,他们家的区域经常出现塞车.塞人等情况,这导致 ...

- Python的初步认识与基本模块的导入

由于公司开发都使用了Python,老大说要每个人都会,前端也要学,所以就看着老大写的博客一步步来了,但是对于小白而言,一门新的语言总得跳许多坑.尤其是Mac安装Python,各种坑. 坑一.由于Mac ...

- android开发中关于继承activity类中方法的调用

android开发中关于继承activity类中的函数,不能在其他类中调用其方法. MainActivity.java package com.example.testmain; import and ...

- chrome谷歌浏览器-DevTool开发者工具-详细总结

目录: 一.概述 1.官方文档 2.打开方法: 3.前言: 二.九个模块: 1.设备模式Device Mode 2.元素面板Elements 3.控制台面板Console 4.源代码面板Sources ...

- grid栅格布局

前面的话 Grid布局方式借鉴了平面装帧设计中的格线系统,将格线运用在屏幕上,而不再是单一的静态页面,可以称之为真正的栅格.本文将详细介绍grid布局 引入 对于Web开发者来说,网页布局一直是个比较 ...

- group by和count联合使用问题

要根据用户发布的产品数量来排序做分页,使用group ) FROM( SELECT uid,COU 工作中要根据用户发布的产品数量来排序做分页,使用group by uid 用count(uid) 来 ...

- 【LeetCode】94. Binary Tree Inorder Traversal

题目: Given a binary tree, return the inorder traversal of its nodes' values. For example:Given binary ...