简单三段式状态机实验3-Sequence Detect(序列检测)

1、序列检测器的逻辑功能描述:序列检测指的就是将一个指定的序列从数字码流中识别出来。本例中,我们将设计一个"10010”序列的检测器。设x_in为数字码流输入,z_out为检出标记输出,高电平表示“发现指定序列”,低电平表示“没有发现指定序列”。

2、本次试验的data stream是 18'b11_0010_0100_0010_0101,通过循环来给x_in进行赋值。其中还要考虑到重叠现象。

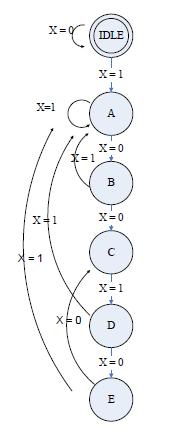

3、重点是状态图的描绘,仅有当状态机跳到E状态时,z_out才置1,说明发现了指定序列。其实这个试验关键是怎么来描绘该状态机。第一次看到夏宇闻书上该例子时,脑子里马上想到头一个问题,就是他是如何画出该状态机的,这个过程没有讲,很纳闷,那会是刚看Verilog,很多不懂,于是就放下这个问题,只阅读了代码。然而此次去看该例子时,我只看了题目和他的状态机,代码就不用看了,觉得书上画的状态机有点啰嗦,就没仔细看,干脆自己画一个 ,画该状态机其实也很简单,先把所有状态全都列出来,先单向的把IDLE->A->B->C->D->E跳变条件写上,比如IDLE到A,是当输入x_in为1时才会调到A,这个很好确认的吧,然后在仔细针对每个状态为其它条件时该如何跳,比如B是在x_in为1时是到C的,那么就得好好考虑x_in为0时,状态该跳到哪儿,就这样一步一步的仔细推敲,完整的状态机很快就完成。

4、代码实现:

sequence_detect.v

module sequence_detect(

//input

clk,

rst_n,

x_in, //ouput

z_out

);

/****************************************/

input clk;

input rst_n;

input x_in;

output z_out;

/****************************************/

parameter IDLE = 'd0;

parameter A = 'd1;

parameter B = 'd2;

parameter C = 'd3;

parameter D = 'd4;

parameter E = 'd5;

/****************************************/

reg [:] crt_state,nxt_state;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

crt_state <= IDLE;

else

crt_state <= nxt_state;

end

/****************************************/

always @(*)

begin

case(crt_state)

IDLE: if(x_in) nxt_state = A;

else nxt_state = IDLE; A : if(!x_in) nxt_state = B;

else nxt_state = A; B : if(!x_in) nxt_state = C;

else nxt_state = A; C : if(x_in) nxt_state = D;

else nxt_state = IDLE; D : if(!x_in) nxt_state = E;

else nxt_state = A; E : if(!x_in) nxt_state = C;

else nxt_state = A; default: nxt_state = IDLE;

endcase

end

/****************************************/

reg z_out_temp;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

z_out_temp <= 'b0;

else case(nxt_state)

IDLE : z_out_temp <= 'b0;

A : z_out_temp <= 'b0;

B : z_out_temp <= 'b0;

C : z_out_temp <= 'b0;

D : z_out_temp <= 'b0;

E : z_out_temp <= 'b1;

default: z_out_temp <= 'b0;

endcase

end

/****************************************/

assign z_out = z_out_temp;

/****************************************/

endmodule

sequence_detect_top.v

`timescale 1ns / 10ps

module sequence_detect_top;

reg clk;

reg rst_n;

reg [:] data;

wire x_in;

wire z_out;

/***********************************************************/

initial

begin

clk = 'b0;

rst_n = 'b0;

#;

rst_n = 'b1;

end

/***********************************************************/

always # clk = ~clk;

/***********************************************************/

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

data <= 'b11_0010_0100_0010_0101;

else

data <= {data[:],data[]};

end

/***********************************************************/

assign x_in = data[];

/***********************************************************/

sequence_detect sequence_detect_inst(

//input

.clk(clk),

.rst_n(rst_n),

.x_in(x_in), //ouput

.z_out(z_out)

);

/***********************************************************/

endmodule

5、仿真波形:

仅当crt_state在E状态(5)时,z_out置1。通过波形可以看到,输出是正确的。

简单三段式状态机实验3-Sequence Detect(序列检测)的更多相关文章

- 简单三段式状态机实验2-LCD12864

此实验是在“基于I2C EPPRPM(AT24C02B) + LCD12864实验”基础上,把LCD模块里的一段式状态机改成三段式,I2C EPPROM模块暂时未改出来,一步一步来吧,改完后代码下载到 ...

- 简单三段式状态机实验1-SOS

一直想从一段式状态机切换到三段式状态机,从书上和网上不断搜寻三段式案例及方法,感觉很简单,就想拿之前做过的实验把一段式改成三段式,可是写起来并非那么简单,很棘手,改完后也没有成功,尤其状态机里面的计数 ...

- Verilog笔记.三段式状态机

之前都是用的一段式状态机,逻辑与输出混在一起,复杂点的就比较吃力了. 所以就开始着手三段式状态机. 组合逻辑与时序逻辑分开,这样就能简单许多了. 但是两者在思考方式上也有着很大的区别. 三段式,分作: ...

- FPGA三段式状态机的思维陷阱

用三段式描述状态机的好处,国内外各位大牛都已经说的很多了,大致可归为以下三点: 1.将组合逻辑和时序逻辑分开,利于综合器分析优化和程序维护; 2.更符合设计的思维习惯; 3.代码少,比一段式状态机更简 ...

- 10010序列检测器的三段式状态机实现(verilog)

序列检测器是时序数字电路设计中经典的教学范例,夏宇闻的<verilog数字系统设计教程>一书中有这个例子,用verilog设计一个“10010”序列的检测器.看完后我觉得F和G两个状态多余 ...

- 基于FPGA的三段式状态机

状态机分类: 通常, 状态机的状态数量有限, 称为有限状态机(FSM) .由于状态机所有触发器的时钟由同一脉冲边沿触发, 故也称之为同步状态机. 根据状态机的输出信号是否与电路的输入有关分为 Meal ...

- (原创)Verilog三段式状态机

下面以上图一个简单的FSM说明三段式Verilog状态机范式: `timescale 1ns / 1ps module FSM( clk,rst_n, in1,in2, out1,out2, CS,N ...

- Verilog三段式状态机描述

时序电路的状态是一个状态变量集合,这些状态变量在任意时刻的值都包含了为确定电路的未来行为而必需考虑的所有历史信息. 状态机采用VerilogHDL语言编码,建议分为三个always段完成. 三段式建模 ...

- verilog 三段式状态机的技巧

三段式代码多,但是有时钟同步,延时少,组合逻辑跟时序逻辑分开并行出错少. (1)同步状态转移 (2)当前状态判断接下来的状态 (3)动作输出 如果程序复杂可以不止三个always .always ...

随机推荐

- redis第一篇--综述

1 redis里边有数据库的概念.可分为1-255这些表.在存储或者查找的时候要指明. redis_sentinel 集群里边封装成了namespace这样的概念.与db是不一样的.

- ios控件 UIImageView

UIImageView的作用是显示图片和多张动态的图片 - (id)initWithImage:(UIImage *)image;//初始化图片视图 - (id)initWithImage:(UI ...

- 近十年one-to-one最短路算法研究整理【转】

前言:针对单源最短路算法,目前最经典的思路即标号算法,以Dijkstra算法和Bellman-Ford算法为根本演进了各种优化技术和算法.针对复杂网络,传统的优化思路是在数据结构和双向搜索上做文章,或 ...

- 我眼中的C#3.0 摘自于网络:http://www.cnblogs.com/joinger/articles/1297237.html

每次有新技术发布时,我们总能感受到两种截然不同的情绪: 一种是恐惧和抵抗,伴随着这种情绪的还有诸如"C# 2.0用的挺好的,为什么要在C# 3.0搞到那么复杂?"或者"我 ...

- curl 测试web站点的响应时间

curl -s -w "\n"::%{time_namelookup}::%{time_connect}::%{time_starttransfer}::%{time_total} ...

- linux命令:find详解

Linux中find命令常见用法示例: find path -option [-print] [ -exec -ok command ] {} \; #-print 将查找到的文件输出到标准输出#-e ...

- ignite客户端找不到服务端的时候如何设置退出

ignite启动客户端时需要有服务端支持: Ignition.setClientMode(true); Ignition.start("ignite.xml"); 这里有个问题,当 ...

- HDU 5455 Fang Fang 水题,但题意描述有问题

题目大意:f[1]=f,f[2]=ff,f[3]=ffc,以后f[n]每增加1,字符串增加一个c.给出一个字符串,求最少有多少个f[]组成.(字符串首尾相连,比如:ffcf可看做cfff) 题目思路: ...

- Swift 与 JSON 数据 浅析

转载自:http://www.cnblogs.com/theswiftworld/p/4660177.html 我们大家平时在开发 App 的时候,相信接触最多的就是 JSON 数据了.只要你的 Ap ...

- robot framework -记录错误

1.注意ie浏览器代理设置,报奇怪的错误 2.注意浏览器的安全设置,保护模式全部不要勾选