FPGA中关于SPI的使用

FPGA中关于SPI的使用

信息来源

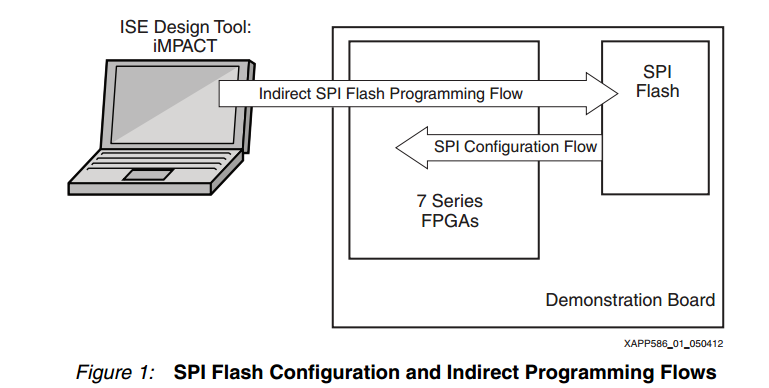

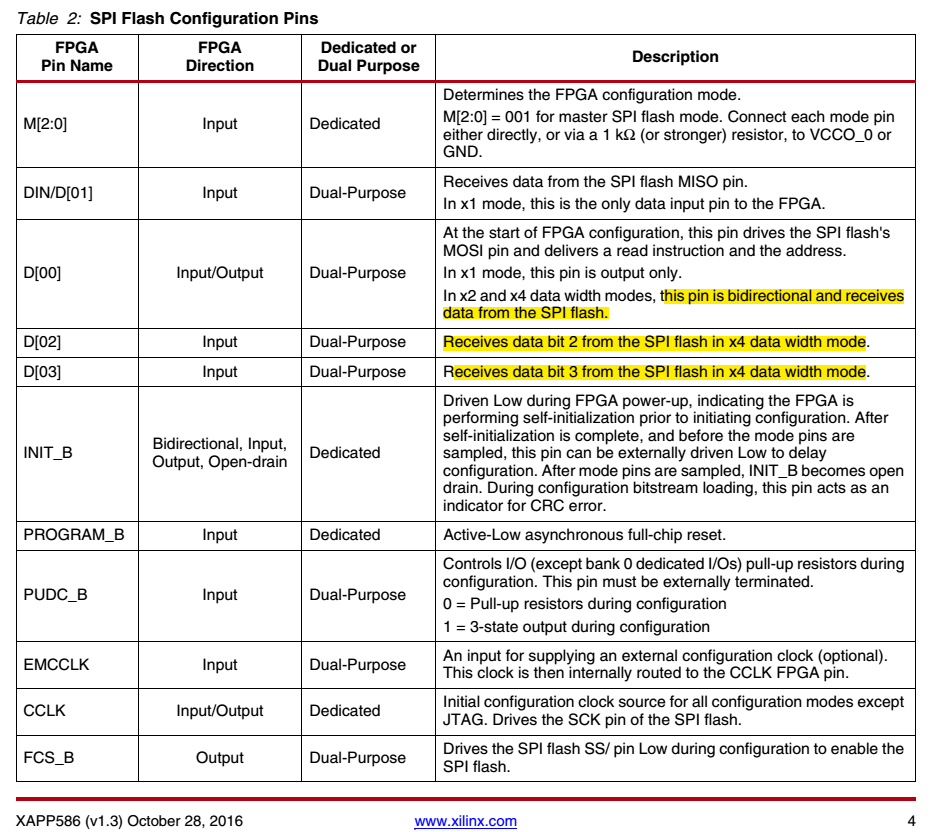

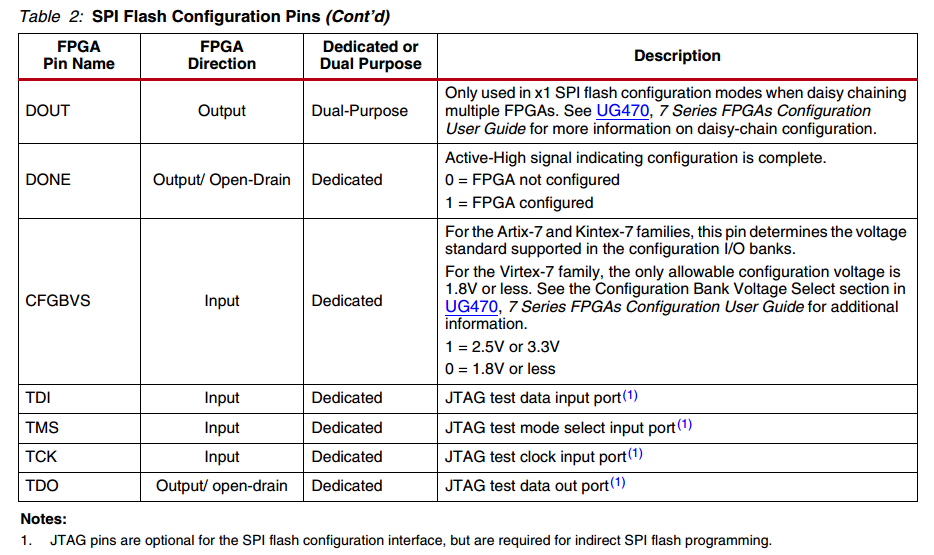

SPI Flash的编程

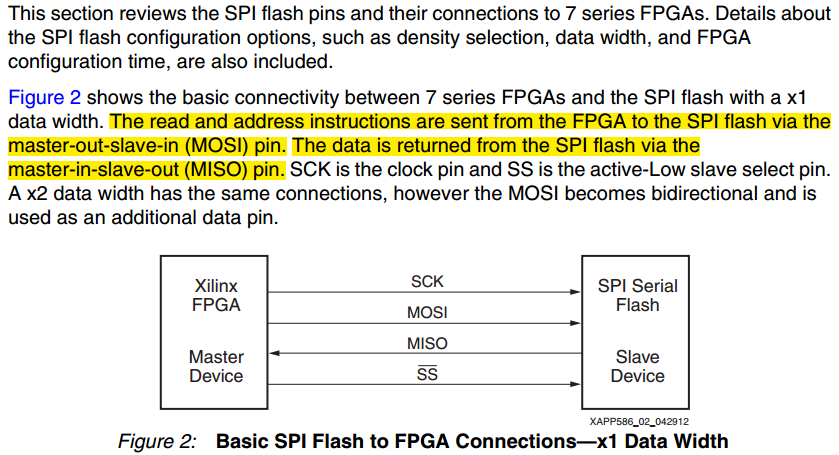

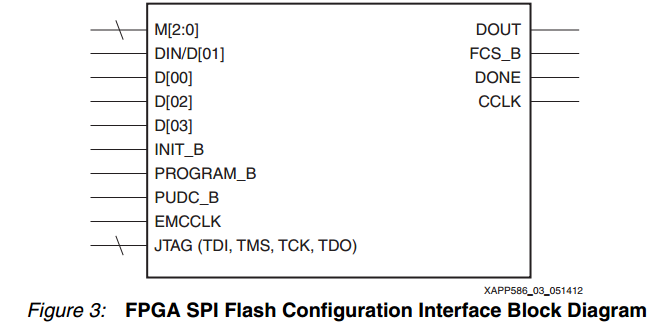

最新的SPI不止有4根信号线,可以增加到支持4bit的数据宽度

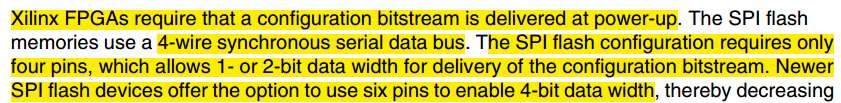

SPI Flash Basics

能够扩展成4bit数据的是MOSI信号

FPGA中关于SPI的使用的更多相关文章

- 如何让FPGA中的SPI与其他模块互动起来

在上一篇文章<FPGA的SPI从机模块实现>中,已经实现了SPI的从机模块,如何通过SPI总线与FPGA内部其他模块进行通信,是本文的主要讨论内容. 一. 新建FPGA内部DAC控制模块 ...

- FPGA中的delay与latency

delay和latency都有延迟的意义,在FPGA中二者又有具体的区别. latency出现在时序逻辑电路中,表示数据从输入到输出有效经过的时间,通常以时钟周期为单位. delay出现在组合逻辑电路 ...

- FPGA中的INOUT接口和高阻态

除了输入输出端口,FPGA中还有另一种端口叫做inout端口.如果需要进行全双工通信,是需要两条信道的,也就是说需要使用两个FPGA管脚和外部器件连接.但是,有时候半双工通信就能满足我们的要求,理论上 ...

- FPGA中的时序分析(四)

常用约束语句说明 关于Fmax 上述是实现Fmax的计算公式,clock skew delay的计算如下图, 就是两个时钟的差值.到头来,影响Fmax的值的大小就是组合逻辑,而Fmax是针对 ...

- 【转】关于FPGA中建立时间和保持时间的探讨

时钟是整个电路最重要.最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错:因而明确FPGA设计中决定系统时钟的因素,尽 ...

- FPGA中浮点运算实现方法——定标

有些FPGA中是不能直接对浮点数进行操作的,仅仅能採用定点数进行数值运算.对于FPGA而言,參与数学运算的书就是16位的整型数,但假设数学运算中出现小数怎么办呢?要知道,FPGA对小数是无能为力的,一 ...

- FPGA中改善时序性能的方法_advanced FPGA design

本文内容摘自<advanced FPGA design>对应中文版是 <高级FPGA设计,结构,实现,和优化>第一章中的内容 FPGA中改善时序,我相信也是大家最关心的话题之一 ...

- Altera FPGA中的pin进一步说明

最近END china上的大神阿昏豆发表了博文 <FPGA研发之道(25)-管脚>,刚好今天拿到了新书<深入理解Altera FPGA应用设计>第一章开篇就讲pin.这里就两者 ...

- FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会.硬件逻辑实现的除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成.因此FPGA实现除法运算并不是一个&qu ...

随机推荐

- react native 之 Android物理返回键

基本用法 根据文档,安卓back键的处理主要就是一个事件监听: BackAndroid.addEventListener('hardwareBackPress', this.onBackPressed ...

- MySQL常见建表选项及约束

阅读目录---MySQL常见的建表选项及约束: 1.create table选项 1.指定列选项:default.comment 2.指定表选项:engine.auto_increment.comme ...

- Oracle密码概要文件,密码过期时间180天修改为3天,相关用户密码是否过期

#Oracle用户密码,概要文件修改测试 #默认的用户使用概要文件,默认概要文件密码过期时间参数180天,修改为3天,对于老的用户来说,是密码过期,还是未发生改变, 对于新用户来说,新设置的密码过期时 ...

- Linux命令学习之路——变更文档拥有者:chown

使用权限:root用户 使用方式:chown [ -cvfRh ] [ --help ] [ --version ] user[ :group ] file... 作用:该命令用于改变文档的拥有者 注 ...

- SVD分解求解旋转矩阵

1.设是两组Rd空间的点集,可根据这两个点集计算它们之间的旋转平移信息. 2.设R为不变量,对T求导得: 令 则 将(4)带入(1)得: 令 则 (相当于对原来点集做减中心点预处理,再求旋转量) 3. ...

- xdoj--1144 (合并模板)--有趣的优先队列(优先队列默认权值最大的数在前面)

我觉得这道题出的很好 区别于“哈夫曼树” 因为事之多合并k个 理论说尽可能多合并. 然后我们看一个简单的例子 4 3 1 2 3 4 ——>6 4——>10 (6+10)=16: 1 2 ...

- lecture2-word2vec-七月在线nlp

离散表示: one-hot bag of words -- 词权重 ~不能表示顺序关系 TF-IDF (Term Frequency - Inverse Document Frequency) [ ...

- HDU 1754:I Hate It(线段树模板)

I Hate It Time Limit: 9000/3000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others) Total ...

- HDU 1711:Number Sequence(KMP模板,求位置)

Number Sequence Time Limit: 10000/5000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others) ...

- 【HDOJ1384】【差分约束+SPFA】

http://acm.hdu.edu.cn/showproblem.php?pid=1384 Intervals Time Limit: 10000/5000 MS (Java/Others) ...