ZYNQ Block Design中总线位宽的截取与合并操作

前言

在某些需求下,数据的位宽后级模块可能不需要原始位宽宽度,需要截位,而某些需求下,需要进行多个数据的合并操作。

在verilog下,截位操作可如下所示:

wire [7:0] w_in;

wire [3:0] w_out;

assign w_out = win[3:0];合并操作可如下所示:

wire [3:0] w_in0;

wire [3:0] w_in1;

wire [7:0] w_out;

assign w_out = {w_in1,w_in0};所以问题就来了:如何在不写代码的情况下在block design设计中实现截取与合并的操作呢?

用到的IP

(1)constant IP。

此IP可以输出可配置位宽的常数,电平可配置0或者1。

(2)concat IP。

此IP可以使得分立的线拼接成单一线输出,相当于verilog描述的拼接操作。输入端口数和位宽均可配置。注意In1会放置在高位,[In1,In0]。

(3)slice IP。

此IP功能跟concat IP相反,会把输入截取想要的位宽输出。相当于verilog的位宽截取操作。输入位宽,输出位宽,截取msb和截取lsb都是可以配置的。

实例

100M网口使用MII接口。可以知道数据tx和rx都是4bit位宽的,但在MII IP接口中,数据位宽为8bit。则需截位与合并。

(1)总线位宽合并。

如下图所示,对于100M的网口使用,rx的高4bit需要接0。则需要使用到constant IP和concat IP。

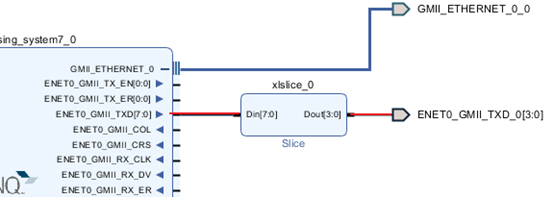

(2)总线位宽截取。

对于100M网口的tx,高位是没用的,则通过slice IP截取低4bit作为输出。

重新生成wrapper,可以看到位宽符合预期,这么做的好处在于无需手动去修改生成的信号位宽,一劳永逸。

以上。

ZYNQ Block Design中总线位宽的截取与合并操作的更多相关文章

- ZYNQ block design警告:[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly.

前言 在Block design中引出AXI接口给外部,检查设计告警如下: [BD 41-968] AXI interface port /axi_lite4 is not associated to ...

- Verilog中变量位宽注意

Verilog中,变量定义方式可以为:reg[位宽-1:0] 数据名:reg[位宽:1] 数据名.其他变量也类似. 以reg变量cnt为例,当cnt位宽为4时,可定义为reg[3:0] cnt,或者定 ...

- C++中输出 位宽和小数点后位数 的控制

要用到这个头文件: <iomanip> setw(x) : 表示控制输出x的位宽 setprecision(x) :表示 控制输出小数点后 x 位 cout.precision(x): 表 ...

- 使用js方法将table表格中指定列指定行中相同内容的单元格进行合并操作。

前言 使用js方法对html中的table表格进行单元格的行列合并操作. 网上执行此操作的实例方法有很多,但根据实际业务的区别,大多不适用. 所以在网上各位大神写的方法的基础上进行了部分修改以适合自己 ...

- s3c2440裸机-内存控制器(二、不同位宽外设与CPU地址总线的连接)

不同位宽设备的连接 black 我们先看一下2440芯片手册上外设rom是如何与CPU地址总线连接的. 8bit rom与CPU地址线的连接 8bit*2 rom与CPU地址线的连接 8bit*4 r ...

- C语言-字、半字、内存位宽相关

1.32位系统:32位系统指的是32位数据线,但是一般地址线也是32位,这个地址线32位决定了内存地址只能有32位二进制,所以逻辑上的大小为2的32次方.内存限制就为4G.实际上32位系统中可用的内存 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 【设计经验】3、ISE中烧录QSPI Flash以及配置mcs文件的加载速度与传输位宽

一.软件与硬件平台 软件平台: 操作系统:Windows 7 64-bit 开发套件:ISE14.7 硬件平台: FPGA型号:XC6SLX45-CSG324 QSPI Flash型号:W25Q128 ...

- Vivado中备份设计好的block design

参考链接 https://blog.csdn.net/dimples_song/article/details/81391615 前言 为了不每次都重新生成block design,避免重复劳动. 可 ...

随机推荐

- Java编程思想,初学者推荐看看

这是一本介绍Java编程思想,如何从面向过程的编程思想转换为面向对象的编程思想.我个人是比较建议新手看一下的,思想掌握了,学起来自然也就会方便很多的,我还有一些Java基础的数,有需要的可以找我要,都 ...

- Linux基础之定时任务

30.1)什么是定时任务 定时任务命令是cond,crond就是计划任务,类似于我们平时生活中的闹钟,定点执行. 30.2)为什么要用crond 计划任务主要是做一些周期性的任务,比如凌晨3点定时备份 ...

- bit、byte、kb、mb、g的区别

1Byte=8bit1KB=1024Byte(字节)=8*1024bit1MB=1024KB1GB=1024MB1TB=1024GB bit是计算机数据的最小单元.要么是0,要么是1. byte 关键 ...

- jdk安装及环境配置

1.下载对应的安装包(我们公司用的是jdk 1.8) 2.选择对应版本,点击安装,在选择安装位置的时候,选择自己对应存放的位置,其他都点击下一步就行了,先安装jdk,后安装jre 3.环境变量,选择 ...

- mybatis的一对多双向映射

连表查询 select id resultType resultMap resultType和resultMap不能同时使用 association 属性 映射到多对一中的“一”方的“复杂类型”属性, ...

- python案例:使用if语句实现一个猜拳游戏

任务要求: 在控制台中提示输入石头.剪刀.布,按回车键,然后给出游戏结果. 分析: 我们知道在游戏规则中,石头克剪刀,剪刀克布,布克石头.但是这在计算机中并不是很好直接的表示,因此我们分别用0.1.2 ...

- Flink Metrics 源码解析

Flink Metrics 有如下模块: Flink Metrics 源码解析 -- Flink-metrics-core Flink Metrics 源码解析 -- Flink-metrics-da ...

- 快速了解Python并发编程的工程实现(下)

关于我 一个有思想的程序猿,终身学习实践者,目前在一个创业团队任team lead,技术栈涉及Android.Python.Java和Go,这个也是我们团队的主要技术栈. Github:https:/ ...

- 服务链路跟踪 && 服务监控

服务链路跟踪 背景 微服务以微出名,在实际的开发过程中,涉及到成百上千个服务,网络请求引起服务之间的调用极其复杂. 当请求不可用或者变慢时,需要及时排查出故障服务点成为了微服务维护的一大难关. 服务链 ...

- copy好文“IT34岁危机破解心法”

在博客园中偶然发现一个好文,收藏并记录以下.在工作中更多的从企业单位用人角度去思考,或许能在职场及职业规划中更加的游刃有余,有的放矢.下面是原文. 本文题目虽是“IT人34岁危机”破解心法,但内容同样 ...