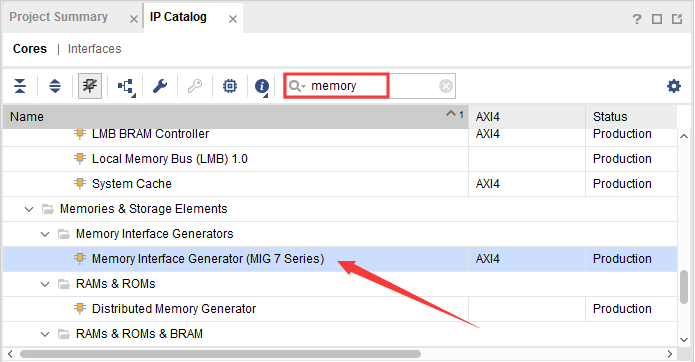

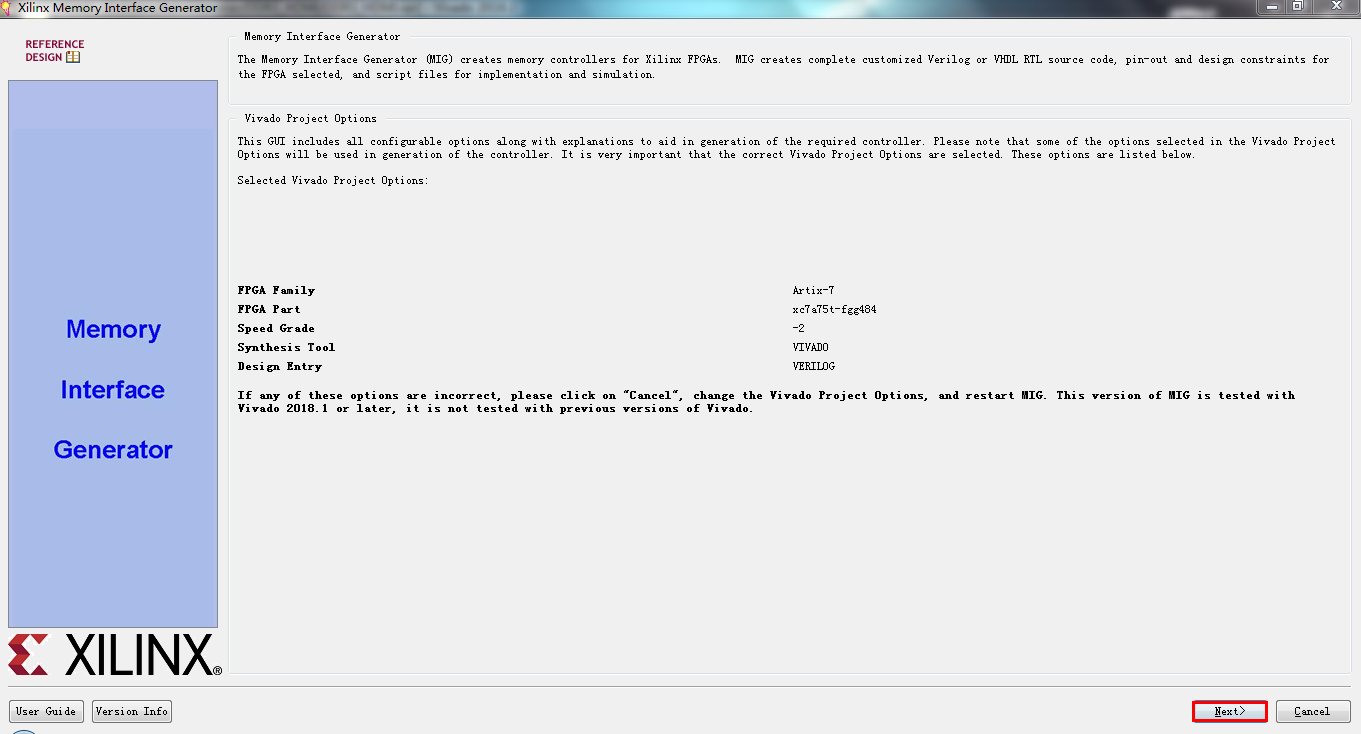

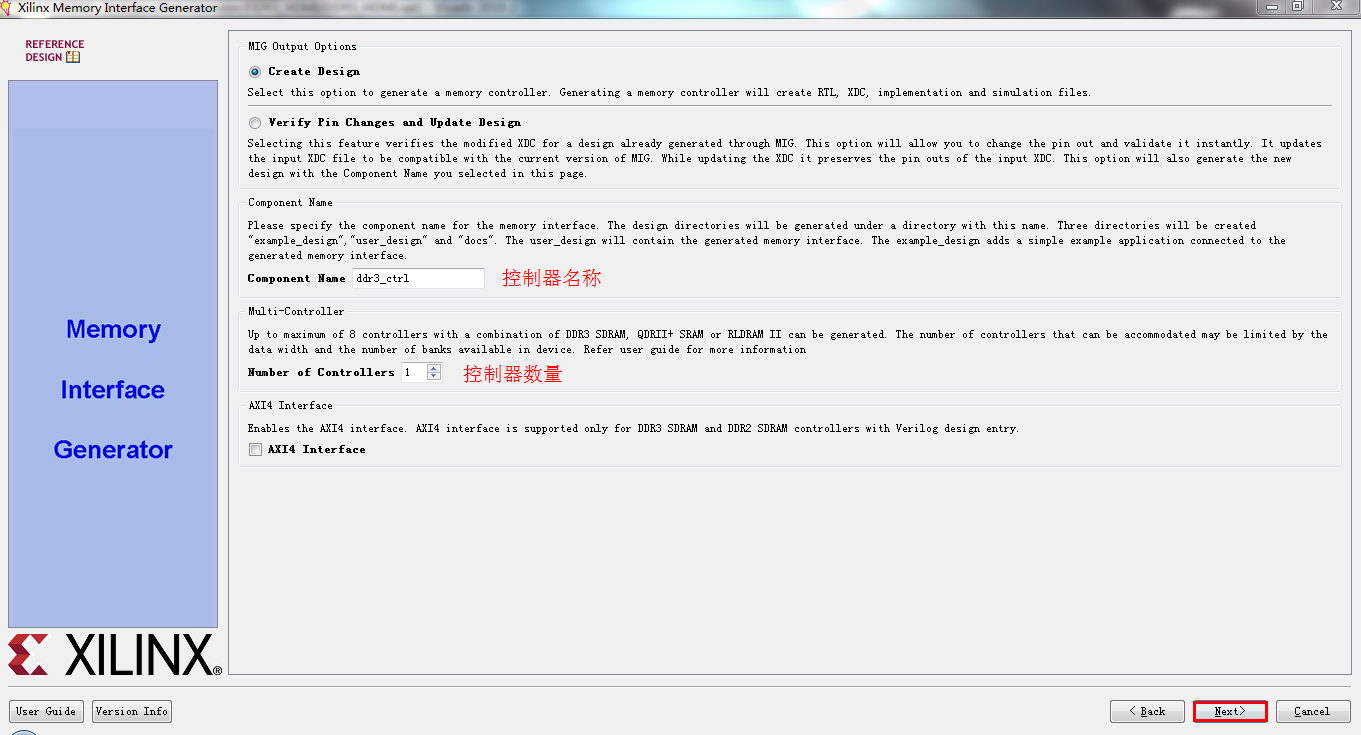

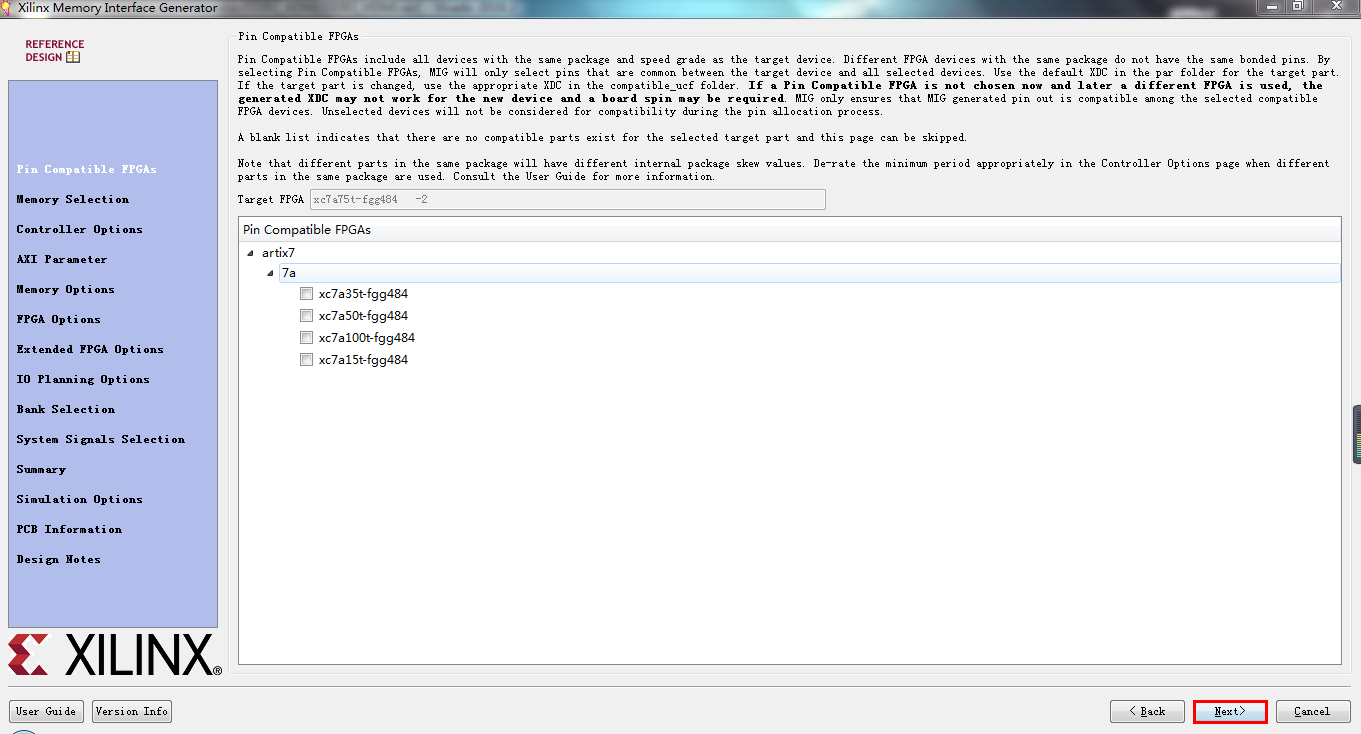

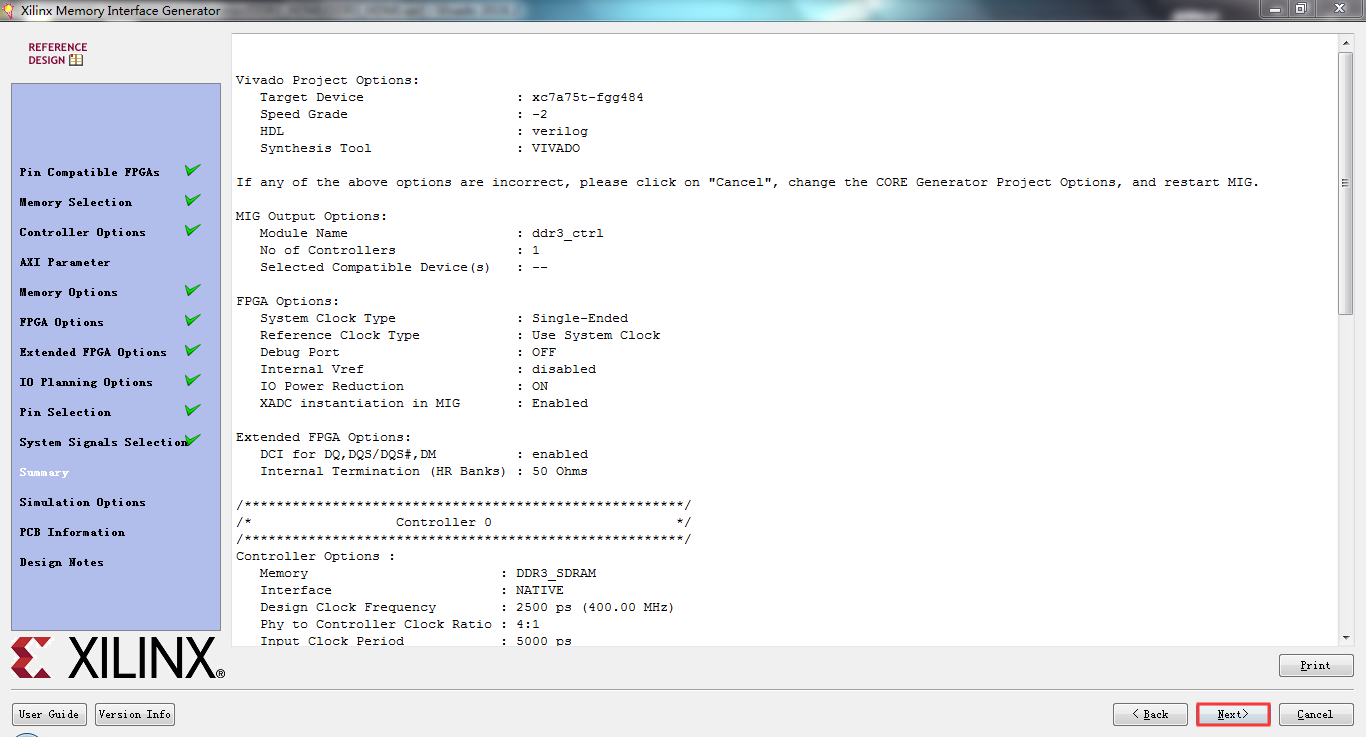

DDR3(1):IP核调取

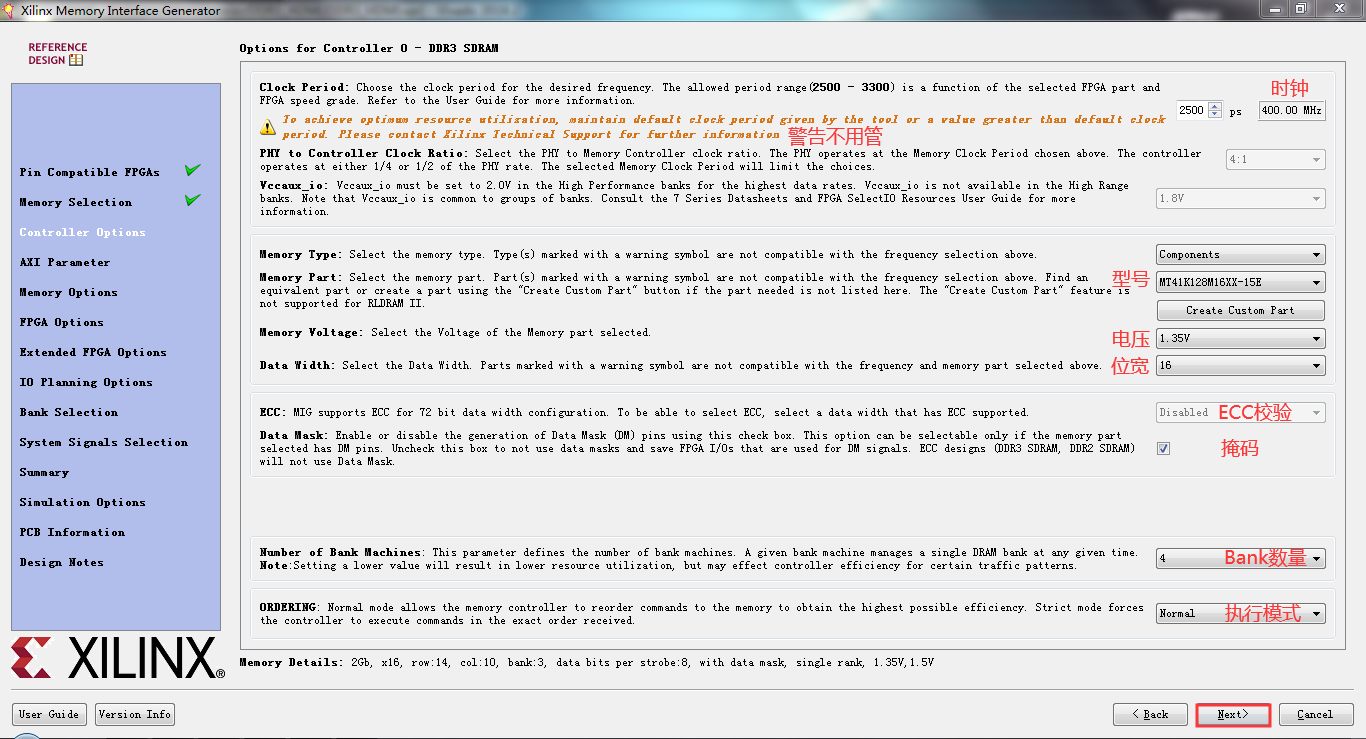

Clock Period : 给DDR3的同步的时钟,此时钟再产生DDR3的800M(400M时钟双沿传递),不用管warning,在此我们设置为 400MHz,若是 FPGA 芯片速度等级不同,则可能该工作频率的范围不一样

Memory Part : 选择 DDR3 SDRAM 的芯片类型,此处需要根据开发板上的芯片类型来选择,若是列表内没有相应的芯片类型,则可以在 Create Custom Part 中根据 DDR3 芯片参数来设定

DDR3的带宽计算 : 400 * 2 * 16 = 12.8 Gbps (400: 控制器 PHY 的时钟, 2: DDR 双沿采样, 16: 16bit,bus 的位宽。)

DDR3控制器是半双工模式(分时读写),平均分配的话每个操作占有 .4Gbps 的理论带宽,实际没有那么多,因为刷新、激活、读写指令等也都会占用周期。因此实际应用我们会*.8来考虑。

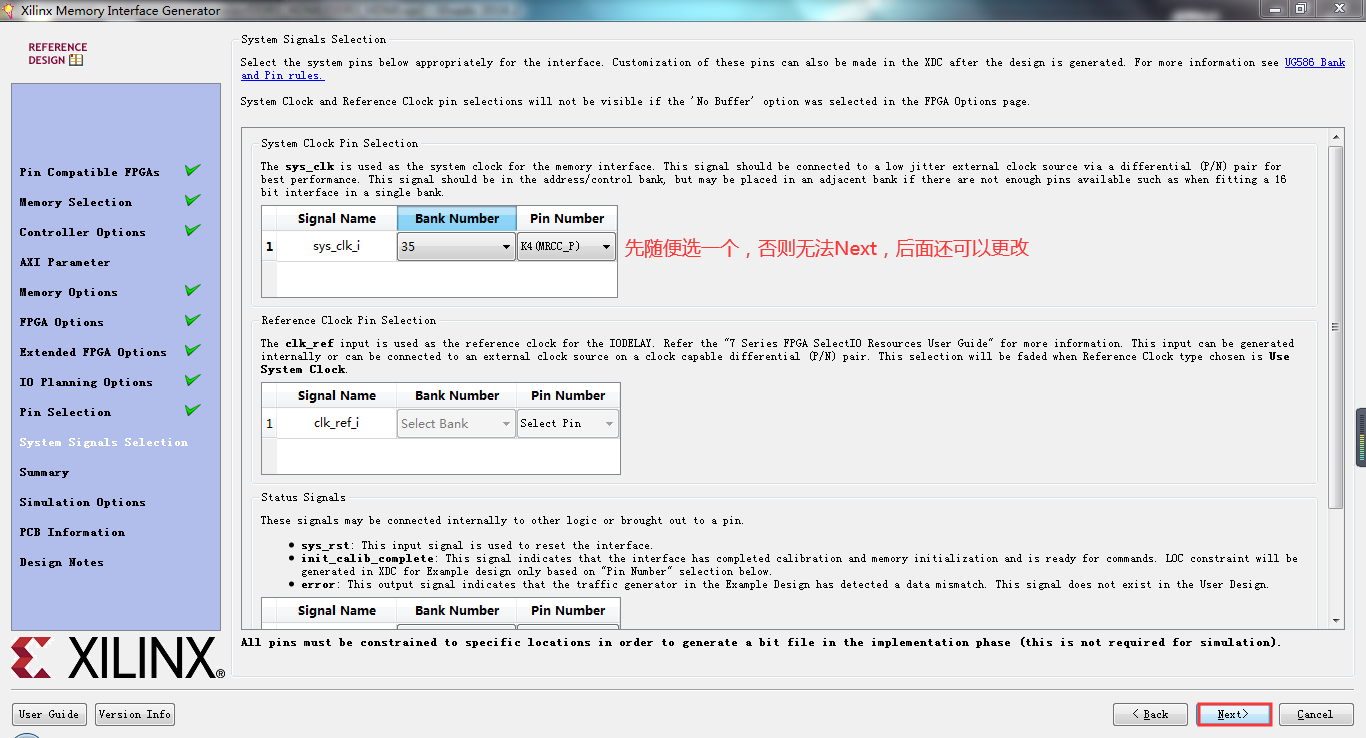

系统时钟

--------------------------------------------------------------------------

single_ended :来源于引脚的单端时钟

deferential :差分时钟

no buffer :来源于 FPGA 内部的时钟。 参考时钟

--------------------------------------------------------------------------

single_ended、deferential、no buffer,

use system clock:只有在 system clock 时钟频率为199MHZ~201MHz 时,才存在该选项。

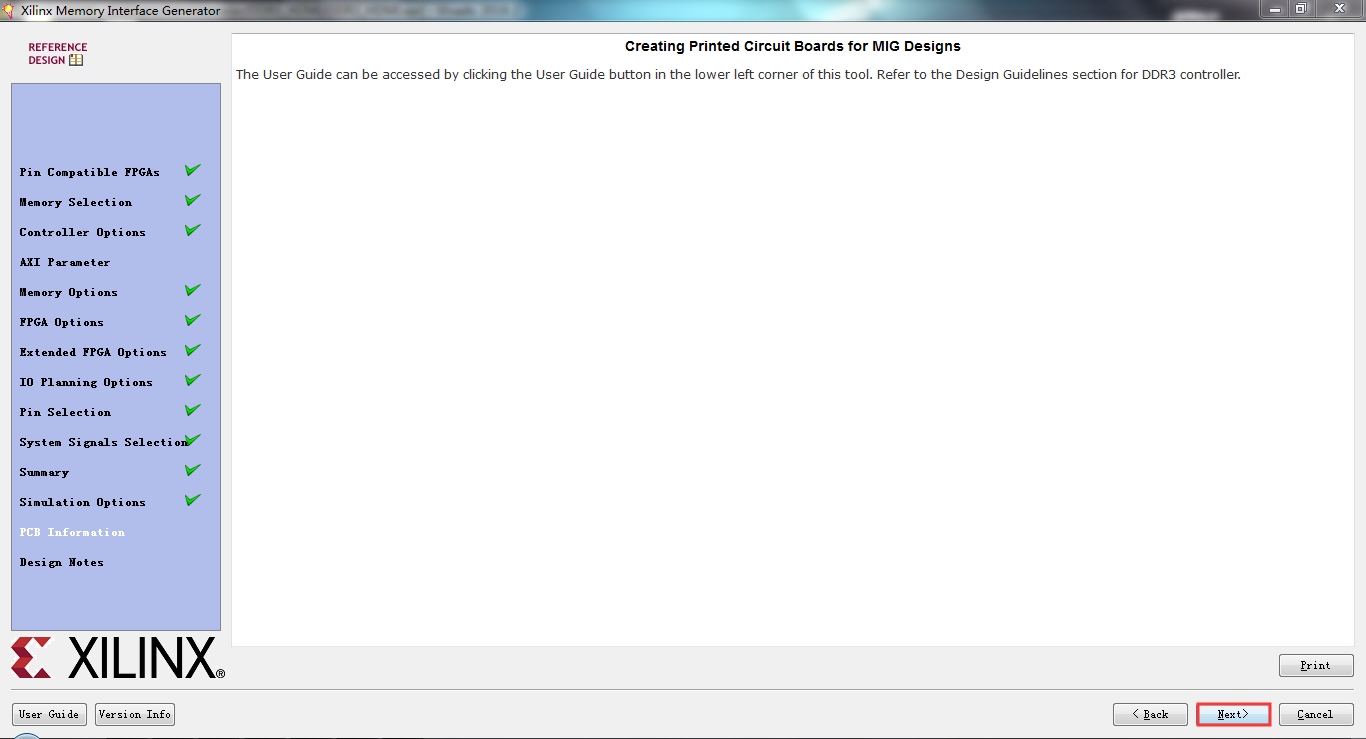

docs : 该IP核相关文档,如使用方法等。

example_design : 该IP核参考例程,仿真模型等。

user_design : 用户可使用的文件,如综合文件、约束文件。

DDR3(1):IP核调取的更多相关文章

- Xilinx DDR3 IP核使用问题汇总(持续更新)和感悟

一度因为DDR3的IP核使用而发狂. 后来因为解决问题,得一感悟.后面此贴会完整讲述ddr3 ip的使用.(XILINX K7) 感悟:对于有供应商支持的产品,遇到问题找官方的流程.按照官方的指导进行 ...

- Lattice 的 DDR IP核使用调试笔记之工程建立

DDR3的IP核的使用相当重要,尤其是对视频处理方面. 下面接收DDR3 的IP 核的生成步骤. 1. 选择DDR IP核的生成路径.名字以及哪种语言之后就可以设置DDR IP 的参数了. 2.选择存 ...

- 在使用FPGA来控制DDR3/DDR2 IP 的时候两个错误的解决办法

对于熟悉Intel FPGA的老(gong)司(cheng)机(shi)来说,外部存储器的控制早已是轻车熟路,但是对于新手,DDR3/DDR2 的IP使用也许并没有那么简单,不过没关系,骏龙的培训网站 ...

- 基于MIG IP核的DDR3控制器(一)

最近学习了DDR3控制器的使用,也用着DDR完成了一些简单工作,想着以后一段可能只用封装过后的IP核,可能会忘记DDR3控制器的一些内容,想着把这个DDR控制器的编写过程记录下来,便于我自己以后查看吧 ...

- Lattice 的 DDR IP核使用调试笔记之DDR 的 仿真

—— 远航路上ing 整理于 博客园.转载请标明出处. 在上节建立完工程之后,要想明确DDR IP的使用细节,最好是做仿真.然后参考仿真来控制IP 核. 仿真的建立: 1.在IP核内的以下路径找到以下 ...

- Lattice 的 Framebuffer IP核使用调试笔记之datasheet笔记

本文由远航路上ing 原创,转载请标明出处. 学习使用以及调试Framebuffer IP 核已经有一段时间了,调试的时候总想记录些东西,可是忙的时候就没有时间来写,只有先找个地方记录下,以后再总结. ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- (转)modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核)

原地址modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核) 1.打开D:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\compxlibgui.e ...

随机推荐

- nginx日志分割及备份

环境:centos7 nginx1.16.1 一.分割及备份的目的 nginx默认将日志信息写在一个文件中,时间一久日志文件中条目越来越多,文件越来越大,不方便查看,备份的时候也不需要备份重复的信息, ...

- NetScaler的常用配置

CITRIX NETSCALER常用功能有:LB,CS,GSLB,SSL LB实现的功能是服务器负载均衡,CS实现基于七层(域名,IP等)的负载均衡,GSLB实现的功能是全局负载均衡,SSL实现的功能 ...

- Python的WSGI(Web Server Gateway Interface)服务器

Python的WSGI(Web Server Gateway Interface)服务器 作者:尹正杰 版权声明:原创作品,谢绝转载!否则将追究法律责任.

- Game Engine Architecture 13

[Game Engine Architecture 13] 1.describe an arbitrary signal x[n] as a linear combination of unit im ...

- window开机启动

C:\Users\sunyues\AppData\Roaming\Microsoft\Windows\Start Menu\Programs\Startup 再次文件夹下写脚本就可 @echo off ...

- GitHub的SSH key配置以及常用的git命令介绍

一. GitHub的SSH key配置 (以windows为例,Mac iOS系统类似) SSH Key 是一种方法来确定受信任的计算机,从而实现免密码登录.Git是分布式的代码管理工具,远程的代码管 ...

- java.util.ConcurrentModificationException异常;java.util.ConcurrentModificationException实战

写代码遇到这个问题,很多博客文章都是在反复的强调理论,而没有对应的实例,所以这里从实例出发,后研究理论: 一.错误产生情况 1 .字符型 (1)添加 public static void main(S ...

- 线程全局修改、死锁、递归锁、信号量、GIL以及多进程和多线程的比较

线程全局修改 x = 100 def func1(): global x print(x) changex() print(x) def changex(): global x x = 50 func ...

- NOIP 2008 传球游戏

洛谷 P1057 传球游戏 洛谷传送门 JDOJ 1536: [NOIP2008]传球游戏 T3 JDOJ传送门 Description 上体育课的时候,小蛮的老师经常带着同学们一起做游戏.这次, ...

- serialize()和new FormData()的区别

serialize()和FormData对象都可将表单数据序列化,后通过ajax异步提交 ,序列化表单就是将form表单中所有name属性序列化成KEY-VALUE的形式,提交到后台,后台以对象相应的 ...