BT.656 NTSC制式彩条生成模块(verilog)

BT.656 NTSC制式彩条生成模块(verilog)

1.知识储备

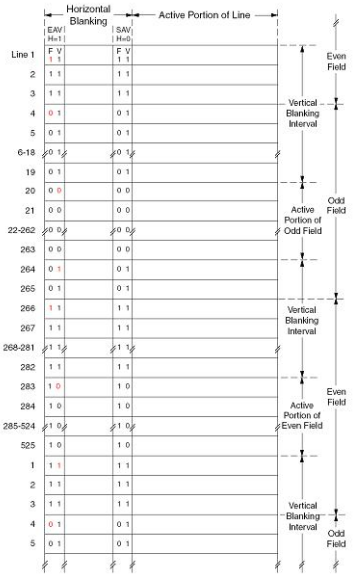

隔行扫描是将一副图像分成两场扫描,第一场扫描第1,2,5,7...等奇数行,第二场扫描2,4,6,8...等偶数行,并把扫奇数行的场称为奇数场,扫偶数行的场称为偶数场,一幅图像经过两次扫描即可。由左到右的扫描称为行扫描,由上到下的扫描称为场扫描。

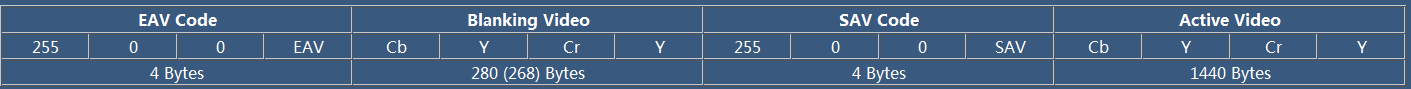

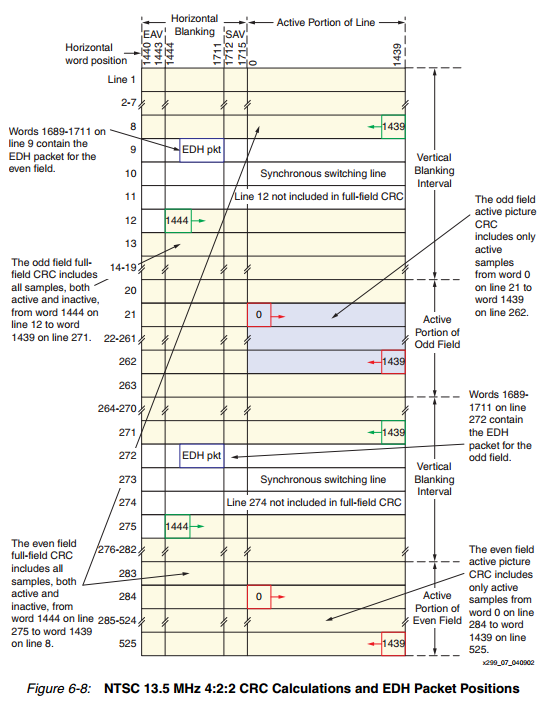

对于标准的8bit BT656(YUV4:2:2)标清制式来说,一帧图像的格式定义如下:

一行是由4个部分组成:行 = 结束码(EAV) + 水平消隐(Horizontal Vertical Blanking) + 起始码(SAV) + 有效数据(Active Video)

注意:实际的工程中彩条每一行像素点的排列并不是这样的,而是(SAV Code ->Active video->EAV Code->Blanking video)

2.代码分析

TPG端口说明:

reset_in:由SDI播出工程内部信号提供。

pclk_in:与播出时钟tx_usrclk对接。

data_out:输出图像数据。

tx_sd_ce:门控时钟(SD-SDI,5/6/5/6)

并且初识化像素位置pixels=1,行位置lines=1,即图像扫描的初始位置。

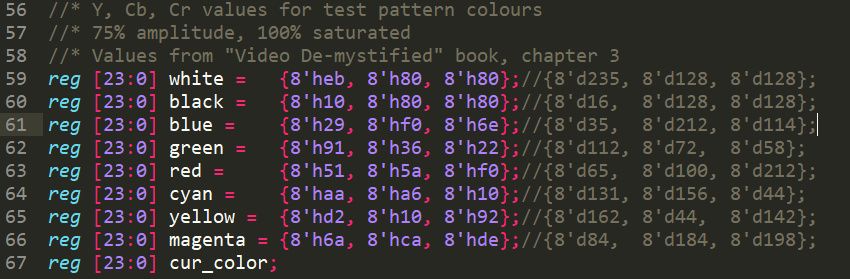

彩条中各种色彩值设定(忽略十进制的数字,部分有误),同时定义了用来存储当前颜色的寄存器cur_color

定义常数,总共有多少行,多少列(1716 ,525)

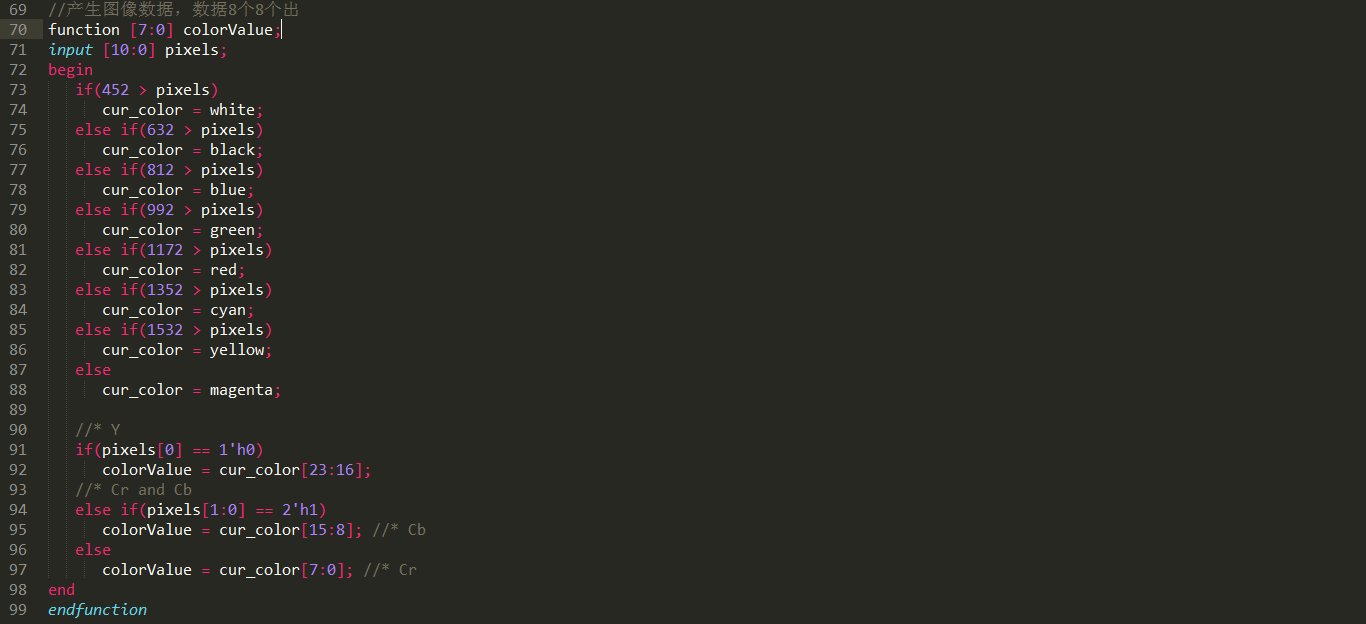

彩条颜色分配函数,通过像素点的位置来分配当前位置的颜色。

有效像素点的排列如下图所示:

pixels初始值为1,则

01:Cb

10:Y

11:Cr

00:Y

01:Cb

通过pixels[0],pixels[1:0]来分割cur_color,得到colorValue.

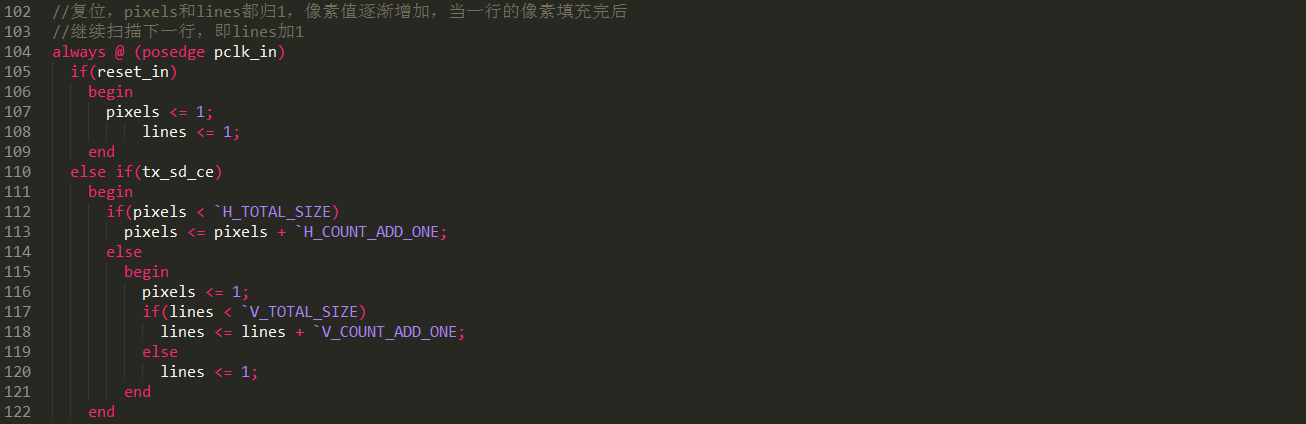

以下always块里面是行扫描和场扫描控制,当一行扫描完成后,pixels回到初始位置,line加1.

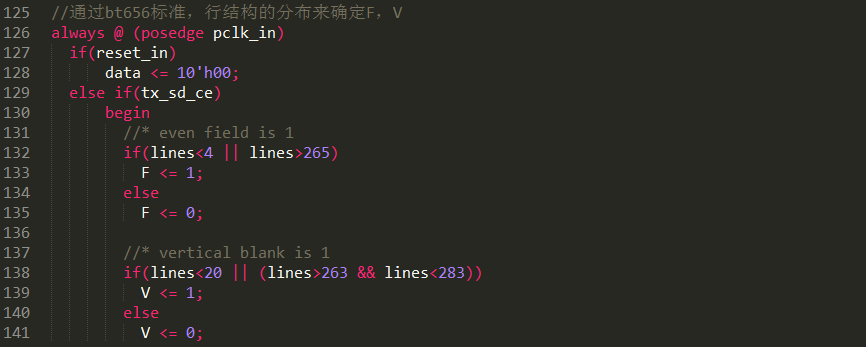

根据行来控制F,V的值:

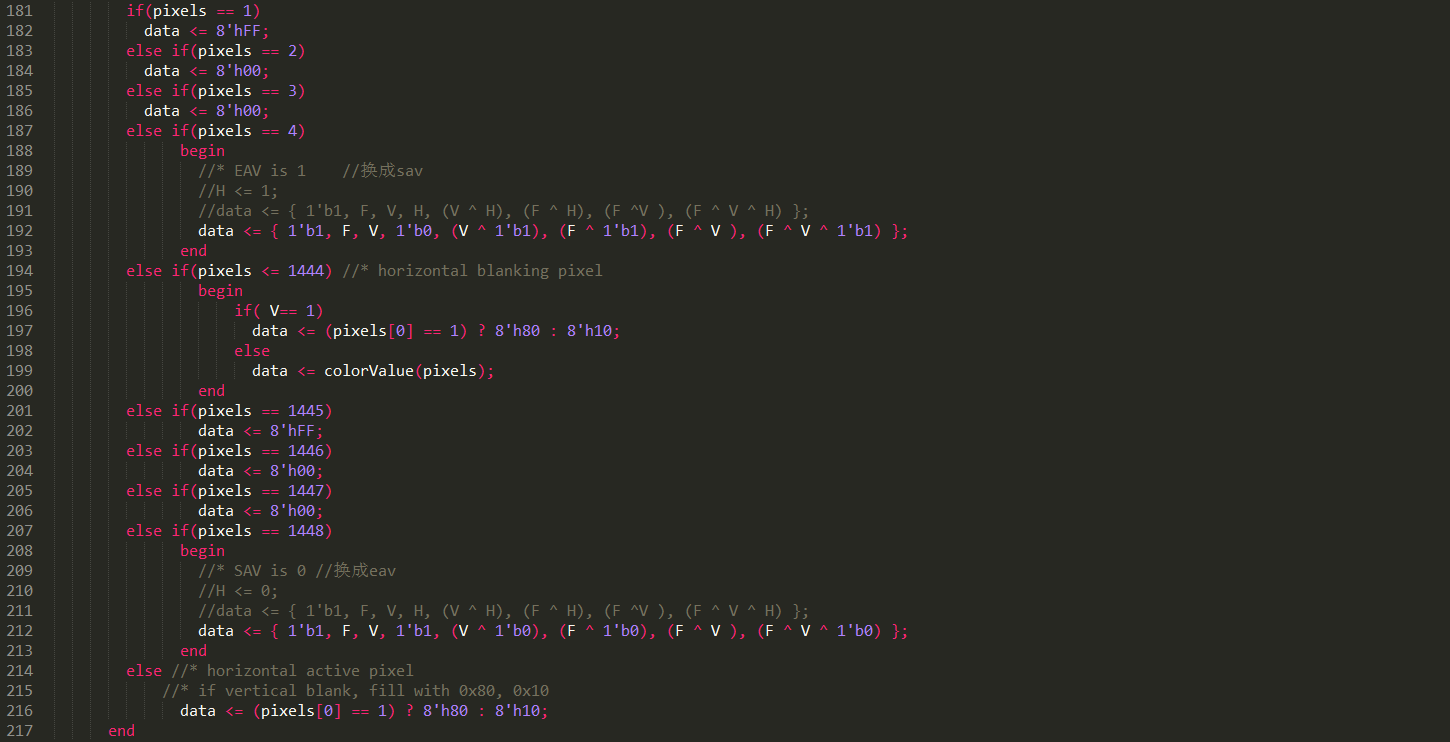

每一行的像素排列,一定要注意顺序SAV(FF,00,00,XY),接下来的是Active video,然后是EAV(FF,00,00,XY),最后是Blanking video,用80,10填充。

视频数据的输出:

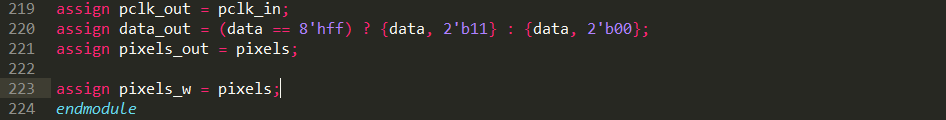

颜色数据是8位的,SDI工程接收的是10bit的数据,如果要对接,就需要进行低位填充,当数据是ff时,低2位填充11,当数据不是ff时,低2位填充00.

module tpg(

reset_in,

pclk_in,

pclk_out,

data_out,

pixels_out,

tx_sd_ce

); input reset_in;

input pclk_in;

input tx_sd_ce;

output pclk_out;

output [:]data_out;

output [:]pixels_out; reg [:] pixels = ;

reg [:] lines = ;

reg [:] data;

reg F, V; wire [:] pixels_w; `define V_TOTAL_SIZE

`define V_ACTIVE_SIZE //* 240 line

`define V_BLANK_SIZE //* 22 line `define H_TOTAL_SIZE

`define H_ACTIVE_SIZE //* 1444 pixel (4(SAV) + 720*2(Y+Cr/Cb))

`define H_BLANK_SIZE //* 272 pixel (4(EAV) + 268) `define H_COUNT_ADD_ONE 'b1

`define V_COUNT_ADD_ONE 'b1 //* Y, Cb, Cr values for test pattern colours

//* 75% amplitude, 100% saturated

//* Values from "Video De-mystified" book, chapter 3

reg [:] white = {'heb, 8'h80, 'h80};//{8'd235, 'd128, 8'd128};

reg [:] black = {'h10, 8'h80, 'h80};//{8'd16, 'd128, 8'd128};

reg [:] blue = {'h29, 8'hf0, 'h6e};//{8'd35, 'd212, 8'd114};

reg [:] green = {'h91, 8'h36, 'h22};//{8'd112, 'd72, 8'd58};

reg [:] red = {'h51, 8'h5a, 'hf0};//{8'd65, 'd100, 8'd212};

reg [:] cyan = {'haa, 8'ha6, 'h10};//{8'd131, 'd156, 8'd44};

reg [:] yellow = {'hd2, 8'h10, 'h92};//{8'd162, 'd44, 8'd142};

reg [:] magenta = {'h6a, 8'hca, 'hde};//{8'd84, 'd184, 8'd198};

reg [:] cur_color; //产生图像数据,数据8个8个出

function [:] colorValue;

input [:] pixels;

begin

if( > pixels)

cur_color = white;

else if( > pixels)

cur_color = black;

else if( > pixels)

cur_color = blue;

else if( > pixels)

cur_color = green;

else if( > pixels)

cur_color = red;

else if( > pixels)

cur_color = cyan;

else if( > pixels)

cur_color = yellow;

else

cur_color = magenta; //* Y

if(pixels[] == 'h0)

colorValue = cur_color[:];

//* Cr and Cb

else if(pixels[:] == 'h1)

colorValue = cur_color[:]; //* Cb

else

colorValue = cur_color[:]; //* Cr

end

endfunction //复位,pixels和lines都归1,像素值逐渐增加,当一行的像素填充完后

//继续扫描下一行,即lines加1

always @ (posedge pclk_in)

if(reset_in)

begin

pixels <= ;

lines <= ;

end

else if(tx_sd_ce)

begin

if(pixels < `H_TOTAL_SIZE)

pixels <= pixels + `H_COUNT_ADD_ONE;

else

begin

pixels <= ;

if(lines < `V_TOTAL_SIZE)

lines <= lines + `V_COUNT_ADD_ONE;

else

lines <= ;

end

end //通过bt656标准,行结构的分布来确定F,V

always @ (posedge pclk_in)

if(reset_in)

data <= 'h00;

else if(tx_sd_ce)

begin

//* even field is 1

if(lines< || lines>)

F <= ;

else

F <= ; //* vertical blank is 1

if(lines< || (lines> && lines<))

V <= ;

else

V <= ; /*

if(pixels <=1440)

begin

if( V== 1)

data <= (pixels[0] == 1) ? 8'h80 : 8'h10;

else

data <= colorValue(pixels);

end

else if(pixels == 1441)

data <= 8'hFF;

else if(pixels == 1442)

data <= 8'h00;

else if(pixels == 1443)

data <= 8'h00;

else if(pixels == 1444)

begin

//* EAV is 1

//H <= 1;

//data <= { 1'b1, F, V, H, (V ^ H), (F ^ H), (F ^V ), (F ^ V ^ H) };

data <= { 1'b1, F, V, 1'b1, (V ^ 1'b1), (F ^ 1'b1), (F ^ V ), (F ^ V ^ 1'b1) };

end

else if(pixels <= 1712)

data <= (pixels[0] == 1) ? 8'h80 : 8'h10;

else if(pixels == 1713)

data <= 8'hFF;

else if(pixels == 1714)

data <= 8'h00;

else if(pixels == 1715)

data <= 8'h00;

else if(pixels == 1716)

begin

//* SAV is 0

//H <= 0;

//data <= { 1'b1, F, V, H, (V ^ H), (F ^ H), (F ^V ), (F ^ V ^ H) };

data <= { 1'b1, F, V, 1'b0, (V ^ 1'b1), (F ^ 1'b1), (F ^ V ), (F ^ V ^ 1'b1) };

end

end

*/

if(pixels == )

data <= 'hFF;

else if(pixels == )

data <= 'h00;

else if(pixels == )

data <= 'h00;

else if(pixels == )

begin

//* EAV is 1 //换成sav

//H <= 1;

//data <= { 1'b1, F, V, H, (V ^ H), (F ^ H), (F ^V ), (F ^ V ^ H) };

data <= { 'b1, F, V, 1'b0, (V ^ 'b1), (F ^ 1'b1), (F ^ V ), (F ^ V ^ 'b1) };

end

else if(pixels <= ) //* horizontal blanking pixel

begin

if( V== )

data <= (pixels[] == ) ? 'h80 : 8'h10;

else

data <= colorValue(pixels);

end

else if(pixels == )

data <= 'hFF;

else if(pixels == )

data <= 'h00;

else if(pixels == )

data <= 'h00;

else if(pixels == )

begin

//* SAV is 0 //换成eav

//H <= 0;

//data <= { 1'b1, F, V, H, (V ^ H), (F ^ H), (F ^V ), (F ^ V ^ H) };

data <= { 'b1, F, V, 1'b1, (V ^ 'b0), (F ^ 1'b0), (F ^ V ), (F ^ V ^ 'b0) };

end

else //* horizontal active pixel

//* if vertical blank, fill with 0x80, 0x10

data <= (pixels[] == ) ? 'h80 : 8'h10;

end assign pclk_out = pclk_in;

assign data_out = (data == 'hff) ? {data, 2'b11} : {data, 'b00};

assign pixels_out = pixels; assign pixels_w = pixels;

endmodule

BT.656 NTSC制式彩条生成模块(verilog)的更多相关文章

- 标准BT.656并行数据结构

转自网络,感谢原作者和转载者. 还有参考:百科http://baike.baidu.com/link?url=bqBT3S7pz_mRJoQE7zkE0K-R1RgQ6FmHNOZ0EjhlSAN_o ...

- ITU-R BT.656 协议

ITU-R BT.601和ITU-R BT.656国际电信联盟(International Telecommunication Union)无线通信部门(ITU-R)制定的标准.严格来说,ITU-R ...

- BT.656视频信号解码

BT.656视频信号解码 BT.656协议标准 ITU-R BT.601和ITU-R BT.656是ITU-R(国际电信联盟)制定的标准.严格来说ITU-R BT.656是ITU-R BT.601 ...

- BT.656

转自http://www.cnblogs.com/s_agapo/archive/2012/04/08/2437775.html 凡是做模拟信号采集的,很少不涉及BT.656标准的,因为常见的模拟视频 ...

- Yii1使用Gii生成模块实现CURD

Yii里Gii的强大就不用说了,可以快速生成模块的Model.Controller来开发.要使用Gii,首先你需要创建好操作的数据表. 第一步:创建数据表 CREATE TABLE `t_knowle ...

- 信号滤波模块verilog代码---UNLOCK,LOCK状态机方式

信号滤波模块verilog代码 `timescale 1ns / 1ps /////////////////////////////////////////////////////////////// ...

- thinkphp3.2自动生成模块BIND_MODULE

thinphp3.2中提供了自定义生成模块与控制器的常量,分别是BIND_MODULE,BUILD_CONTROLLER_LIST 在 index.php 文件中定义 BIND_MODULE,BUIL ...

- TP自动生成模块目录

TP自动生成模块目录 例如我想在项目中增加一个AdminI模块 只需要在入口文件index.php中添加: define('BIND_MODULE','Admin'); 再访问127.0.0.1项目就 ...

- 微信小程序条码、二维码生成模块

代码地址如下:http://www.demodashi.com/demo/13994.html 一.前期准备工作 软件环境:微信开发者工具 官方下载地址:https://mp.weixin.qq.co ...

随机推荐

- 3d的 一些公式

1. 3d围绕 z轴旋转 x,y 变换公式: // α β x = r cosα y = r sinα x' = r cos (α+β) y' = r sin (α+β) x' = r (cosα c ...

- MySQL的架构与历史

MySQL的最主要特性是它的存储引擎架构,这种架构设计将查询处理以及其他系统任务和数据的存储/提取相分离. MySQL最上层服务是一些如连接处理,授权认证,安全等. MySQL的核心服务功能大部分度在 ...

- JavaScript循环语句-6---for语句,while语句的应用逻辑

JavaScript循环语句 学习目标 1.掌握for语句的语法结构 2.掌握for语句的应用逻辑 for语句 语法: For(语句1:语句2:语句3){ 被执行的代码块: } 语句1:在循环(代码块 ...

- UDP方式实现广域网的P2P通信

最近在研究P2P通信,希望能够穿透路由器. 当前的做法只是使用TCP协议进行客户端与服务器端通信,使用UDP协议进行客户端之间的打洞操作,UDP的方式的源码在下方. 一直没有实现TCP的打洞,如果有实 ...

- Codeforces 978E:Bus Video System

题目链接:http://codeforces.com/problemset/problem/978/E 题意 一辆公交车,在每站会上一些人或下一些人,车的最大容量为w,问初始车上可能有的乘客的情况数. ...

- linux cent os 6 的安装

目前,只有图片,没有仔细写,这是在虚拟机内的安装:

- java-类与类,类与接口,接口与接口的关系

1.类与类: - 继承关系,只能单继承,可以多层继承. 2.类与接口: - 实现关系,可以单实现,也可以多实现. - 并且还可以在继承一个类的同时实现多个接口. - * 例:class Demo ex ...

- 2017.4.4 TCP/IP协议栈

OSI和TCP/IP的各层协议总结: TCP/IP在封装和传输数据时,各层所做的工作:

- <jsp:include>动作元素,附:最易出错的一点

先定义一个date.jsp,再定义一个main.jsp.用<jsp:include plage = "相对url地址" flush = "true"> ...

- Redis源码剖析--列表t_list实现

Redis中的列表对象比较特殊,在版本3.2之前,列表底层的编码是 ziplist 和 linkedlist 实现的, 但是在版本3.2之后,重新引入了一个 quicklist 的数据结构,列表的底层 ...