Xilinx源语-------FDRE

1、源语---FDRE

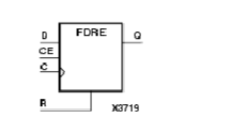

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。在时钟的上升沿数据被加载进入D触发器的输入。

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg1 (

.C (clk), // 同步时钟

.D (data_sync0), //异步数据输入

.Q (data_sync1), //同步数据输出

.CE ('b1), //时钟使能信号

.R ('b0) //复位信号输入,高电平有效

);

由于数据可能与时钟存在着不同步的情况,尤其是在对同步精度要求高的场合,一般还是用多次FDRE源语使得数据、控制信号等同步,例如在一个三态网数据同步模块中使用了四个D触发器进行数据同步:

`timescale 1ps / 1ps (* dont_touch = "yes" *)

module tri_mode_ethernet_mac_0_sync_block #(

parameter INITIALISE = 'b0,

parameter DEPTH =

)

(

input clk, // clock to be sync'ed to

input data_in, // Data to be 'synced'

output data_out // synced data

); // Internal Signals

wire data_sync0;

wire data_sync1;

wire data_sync2;

wire data_sync3;

wire data_sync4; (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg0 (

.C (clk),

.D (data_in),

.Q (data_sync0),

.CE ('b1),

.R ('b0)

); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg1 (

.C (clk),

.D (data_sync0),

.Q (data_sync1),

.CE ('b1),

.R ('b0)

); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg2 (

.C (clk),

.D (data_sync1),

.Q (data_sync2),

.CE ('b1),

.R ('b0)

); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg3 (

.C (clk),

.D (data_sync2),

.Q (data_sync3),

.CE ('b1),

.R ('b0)

); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg4 (

.C (clk),

.D (data_sync3),

.Q (data_sync4),

.CE ('b1),

.R ('b0)

); assign data_out = data_sync4; endmodule

Xilinx源语-------FDRE的更多相关文章

- 关于各种BUF源语的研究

关于各种BUF源语的研究 资料来源: 单端信号需要用到的BUF 关于这些源语的约束: 增大驱动电流 关于管脚的上拉与下拉约束: ODDR的两种操作模式 关于ODDR输出时钟的应用 为什么ODDR需要这 ...

- FPGA同步复位异步复位

今天看了篇博客, 是拿altera的芯片和软件作例子的,讲同步异步复位的: http://blog.sina.com.cn/s/blog_bff0927b0101aaii.html 还有一个博客, h ...

- Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟篇

xilinx的7系列FPGA根据不同的器件类型,集成了GTP.GTX.GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及最 ...

- 瘋耔java语言笔记

一◐ java概述 1.1 ...

- 多线程的学习与python实现

学习了进程与线程,现对自己的学习进行记录. 目录: 一.进程与线程的概念,以及联系与区别 二.多线程 三.python中多线程的应用 四.python实例 五.参考文献 一.进程与线程的概念.以及联系 ...

- Half Sync And Half Async 半同步半异步模式

如题,这是一个典型的CS结构的模式,至少曾经在CS结构中用过,只是没用好.当年用UDP死活都处理不过来网络命令,用此模式轻松解决. 此模式是典型的三层架构,同步层在一个线程内处理业务逻辑:异步层接受并 ...

- Android系统在超级终端下必会的命令大全(adb shell命令大全)

. 显示系统中全部Android平台: android list targets . 显示系统中全部AVD(模拟器): android list avd . 创建AVD(模拟器): android c ...

- Make和Makefile

无论是在Linux还是在Unix环境中,make都是一个非常重要的编译命令.不管是自己进行项目开发还是安装应用软件,我们都经常要用到make或make install.利用make工具,我们可以将大型 ...

- 初识Attention机制(NLP领域)

Attention 机制. 参考:https://blog.csdn.net/xiewenbo/article/details/79382785 要是关注深度学习在自然语言处理方面的研究进展,我相信你 ...

随机推荐

- 字符编码、python2和python3编码的区别

目录 字符编码 文本编辑器存储信息的过程 python解释器解释python代码的流程 python解释器与文本编辑器的异同 不同编码格式存入与读取数据的过程 乱码的分析 python2和python ...

- B1016. 部分 A+B

题目描述 正整数A的"D(为1位整数)部分"定义由A中所有D组成的新整数P,例如给定A=3862767,D=6,则A的"6部分" P是66,因为A中有2个6,现 ...

- sql中count(1)和count(*)有区别吗

count(*) 对 innodb 而言,它需要把数据从磁盘中读取出来然后累计计数:而 MyISAM 引擎把一个表的总行数存在了磁盘上,所以执行 count(*) 会直接返回这个数,如果有 where ...

- MAL参会的笔记1

上周末去参加了著名的MAL.今年在天津主场,于是省去了路费问题. 来的都是平时看到论文中的大佬. 不过最大收获是收割了几个idea. 再就是知道了几个自己之前孤陋寡闻的顶会,比如COLT,VIS等等.

- tweenMax+如何让数字由初始值动画到结束的值

html: <div class="wz1">0</div> css: .wz1{ width: 114px; height: 30px; position ...

- 奇偶选择器:使用odd和even属性实现表格单双行颜色相间和不同

一.奇偶选择器 表格在呈现数据的时候我们为了方便观看,而隔行显示不同的颜色,虽然可以用用类选择器 class实现这种效果,但是未免太过麻烦,为了更加简便地表现这种特殊的效果我们需要用到一种特殊的选择器 ...

- STM32开发板的TIM3开启和关闭

关闭定时器中断要考虑好多情况 1)关闭定时器时,定时器是否在处在工作状态 2)关闭定时器时,定时器是否正好进入中断,造成关闭程序出现断层,进而无法实现完整关闭程序,此时可以使用高一级别的外部中断强制进 ...

- Activiti7入门(五)

1 创建流程 首先选中存放图形的目录(本次我们选择 resources 下的 bpmn 目录),点击菜单: New-BpmnFile,如下图所示: 起完名字 holiday 后(默认扩展名为 bpmn ...

- 解决报错:The server time zone value 'Öйú±ê׼ʱ¼ä' is unrecognized

Cannot create PoolableConnectionFactory (The server time zone value 'Öйú±ê׼ʱ¼ä' is unrecognized . ...

- Supervised pre-trainning有监督预训练

如我们有一个分类任务,数据库很小,这时还是需要通过预训练来避免深度模型的过拟合问题的,只不过预训练是通过在一个大的数据库上(比如imagenet),通过有监督的训练来完成的.这种有监督预训练加小的数据 ...