Make a DAC with a microcontroller's PWM timer

http://www.edn.com/design/analog/4337128/Make-a-DAC-with-a-microcontroller-s-PWM-timer

Many embedded-microcontroller applications require generation of analog signals. An integrated or stand-alone DAC fills the role. However, you can often use PWM signals for generating the required analog signals. You can use PWM signals to create both dc and ac analog signals. This Design Idea shows how to use a PWM timer to simultaneously create a sinusoid, a ramp, and a dc voltage. A PWM signal is a digital signal with fixed frequency but varying duty cycle. If the duty cycle of the PWM signal varies with time and you filter the PWM signal, the output of the filter is an analog signal (Figure 1).

If you build a PWM DAC in this manner, its resolution is equivalent to the resolution of the PWM signal you use to create the DAC. The PWM output signal requires a frequency that is equivalent to the update rate of the DAC, because each change in PWM duty cycle is the equivalent of one DAC sample. The frequency the PWM timer requires depends on the required PWM signal frequency and the desired resolution. The required frequency is FCLOCK=FPWM×2n, where FCLOCK is the required PWM-timer frequency, FPWM is the PWM-signal frequency, and n is the desired DAC resolution in bits.

depicts a circuit that delivers a 250-Hz sine wave, a 125-Hz ramp, and a dc signal. The desired sampling rate is 8 kHz (32 samples for each sine-wave cycle (16× oversampled), and 64 samples for each ramp cycle (32× oversampled)). These figures result in a required PWM-signal frequency of 8 kHz and a required PWM clock frequency of 2.048 MHz. It is usually best for the PWM signal frequency to be much higher than the desired bandwidth of the signals to be produced. Generally, the higher the PWM frequency, the lower the order of filter required and the easier it is to build a suitable filter. This design uses Timer B of the MSP430 in 16-bit mode and in "up" mode, in which the counter counts up to the contents of capture/compare register 0 (CCR0) and then restarts at zero. CCR0 is loaded with 255, thereby giving the counter an effective 8-bit length. You can find this register and others in a DAC demonstration program for the MSP430 microcontroller. Click here to download the program.

CCR1 and output TB1 produce the sine wave. CCR2 and TB2 generate the ramp, and CCR3 and TB3 yield the dc value. For each output, the output mode is the reset/set mode. In this mode, each output resets when the counter reaches the respective CCRx value and sets when the counter reaches the CCR0 value. This scheme provides positive pulses equivalent to the value in CCRx on each respective output. If you use the timer in 8-bit mode, the reset/set output mode is unavailable for the PWM outputs because the reset/set mode requires CCR0. The timer's clock rate is 2.048 MHz. Figure 3

shows the sine and ramp waveforms. The sine wave in this example uses 32 samples per cycle. The sample values are in a table at the beginning of the program. A pointer points to the next value in the sine table, so that, at the end of each PWM cycle, the new value of the sine wave is written to the capture/compare register of the PWM timer.

The ramp in this example does not require a table of data values. Rather, the ramp simply increments the duty cycle for each cycle of the PWM signal until it reaches the maximum and then starts over at the minimum duty cycle. This gradual increase in PWM-signal duty cycle results in a ramp voltage when the signal passes through a filter. You control the dc level by simply setting and not changing the value of the PWM-signal duty cycle. The dc level is directly proportional to the duty cycle of the PWM signal. Figure 2 shows the reconstruction filters used for each signal in this example. The filter for the ac signals is a simple two-pole, stacked-RC filter, which is simple and has no active components. This type of filter necessitates a higher sampling rate than would be required if the filter had a higher order. With the type of filter shown in Figure 2, you should use at least a 16× oversampling rate.

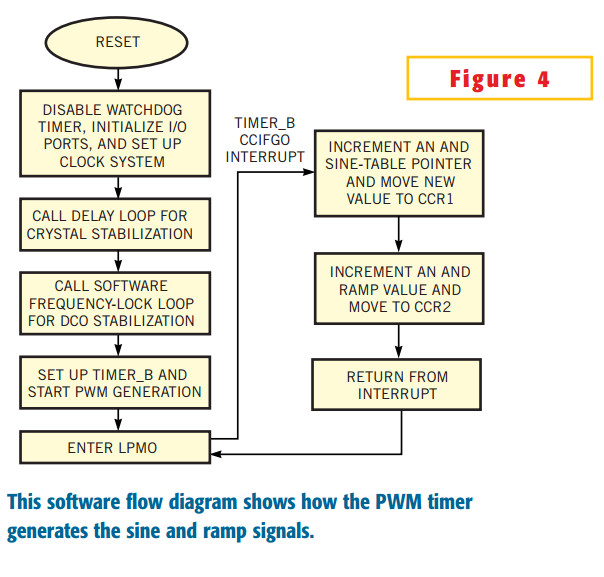

The filter yields its best response when R2>>R1. Also, setting the cutoff frequency too close to the bandwidth edge causes a fair amount of attenuation. To reduce the amount of attenuation in the filter, set the cutoff frequency above the bandwidth edge but much lower than the frequency of the PWM signal. The filter for the dc value serves for charge storage rather than ac-signal filtering. Therefore, it uses a simple, single-pole RC filter. Figure 4

shows the software flow for the DAC. After a reset, the routine stops the watchdog timer, configures the output ports, and sets up the clock system. Next, the software calls a delay to allow the 32,768-Hz crystal to stabilize to calibrate the DCO (digitally controlled oscillator).

Next, the routine calls the calibration routine to set the operating frequency to 2.048 MHz. After the DCO calibration, the program sets up Timer_B, CCR1 and CCR2 for PWM generation and then starts the timer. Finally, the MSP430 goes into low-power mode 0 (LPM0) to conserve power. The CPU wakes up to handle each CCIFG0 interrupt from the PWM timer and then re-enters LPM0. (See references 1, 2, and 3 for more information on the DCO and the MSP430 family.)

Make a DAC with a microcontroller's PWM timer的更多相关文章

- 【STM32】PWM DAC基本原理(实验:PWM实现DAC)

虽然STM32F103ZET6具有内部DAC,但是也仅仅只有两条DAC通道,并且STM32还有其他的很多型号是没有DAC的.通常情况下,采用专用的D/A芯片来实现,但是这样就会带来成本的增加. 不过S ...

- Create a DAC from a microcontroller's ADC

Few microcontrollers include a DAC. Although you can easily find an inexpensive DAC to control from ...

- Cortex-A9 PWM Timer

PWM定时器 4412时钟为我们提供了PWM定时器,在4412中共有5个32位的定时器,这些定时器可发送中断信号给ARM子系统.另外,定时器0.1.2.3包含了脉冲宽度调制(PWM),并 ...

- PWM DAC vs. Standalone

http://analogtalk.com/?p=534 http://analogtalk.com/?p=551 Posted by AnalogAdvocate on April 09, 2010 ...

- PWM DAC Low Pass Filtering

[TI博客大赛][原创]LM3S811之基于PWM的DAC http://bbs.ednchina.com/BLOG_ARTICLE_3005301.HTM http://www.fpga4fun.c ...

- how to generate an analog output from a in-built pwm of Atmega 32AVR microcontrloller?

how to generate an analog output from a in-built pwm of Atmega 32AVR microcontrloller? you need a re ...

- M451 PWM对照数据手册分析

PWM_T Struct Reference Control Register » Pulse Width Modulation Controller(PWM) typedef struct { ...

- 说说M451例程之PWM的寄存器讲解

M451提供了两路PWM发生器.每路PWM支持6通道PWM输出或输入捕捉.有一个12位的预分频器把时钟源分频后输入给16位的计数器,另外还有一个16位的比较器.PWM计数器支持向上,向下,上下计数方式 ...

- 说说M451例程之PWM

/**************************************************************************//** * @file main.c * @ve ...

随机推荐

- Code Conventions for the JavaScript Programming Language

This is a set of coding conventions and rules for use in JavaScript programming. It is inspired by t ...

- ZOJ 3537 Cake(凸包+区间DP)

题目链接:http://acm.zju.edu.cn/onlinejudge/showProblem.do?problemCode=3537 题目大意:给出一些点表示多边形顶点的位置,如果不是凸多边形 ...

- Ubuntu 16.04 使用docker资料汇总与应用docker安装caffe并使用Classifier(ros kinetic+usb_cam+caffe)

Docker是开源的应用容器引擎.若想简单了解一下,可以参考百度百科词条Docker.好像只支持64位系统. Docker官网:https://www.docker.com/ Docker - 从入门 ...

- 课堂实验-模拟实现Sort

课堂实验 模拟实现Linux下Sort -t : -k 2的功能.参考 Sort的实现. 代码如下: /** * Created by Administrator on 2017/5/20. */ i ...

- PHP5.6中php-fpm的配置、启动、关闭和重启

转:http://blog.csdn.net/field_yang/article/details/52401994 该文主要讲述:如何配置PHP-fpm.常见报错解决方法和php-fpm的启动.关闭 ...

- 一步一步学习IdentityServer4 (5) .NETCore2.0 Swagger

首先添加nuget: Swashbuckle.AspNetCore services.AddSwaggerGen(c => { c.SwaggerDoc("v1", new ...

- Java语法知识总结

一:java概述: 1991 年Sun公司的James Gosling等人开始开发名称为 Oak 的语言,希望用于控制嵌入在有线电视交换盒.PDA等的微处理器: 1994年将Oak语言更名为Java: ...

- 基于Json.NET自己实现MVC中的JsonValueProviderFactory

写了博文ASP.NET MVC 3升级至MVC 5.1的遭遇:“已添加了具有相同键的项”之后,继续看着System.Web.Mvc.JsonValueProviderFactory的开源代码. 越看越 ...

- 002 Ajax中传输格式为HTML

一: 1.介绍 返回的数据可以直接插入到需要的地方. 2.优缺点 二:程序大纲 1.结构 三:程序 1.css body { background: #ffb url("logo.png&q ...

- SVM 的推导、特点、优缺点、多分类问题及应用

SVM有如下主要几个特点: (1) 非线性映射是SVM方法的理论基础,SVM利用内积核函数代替向高维空间的非线性映射: (2) 对特征空间划分的最优超平面是SVM的目标,最大化分类边际的思想是SV ...