关于FIFO异步复位的问题

关于FIFO异步复位的问题

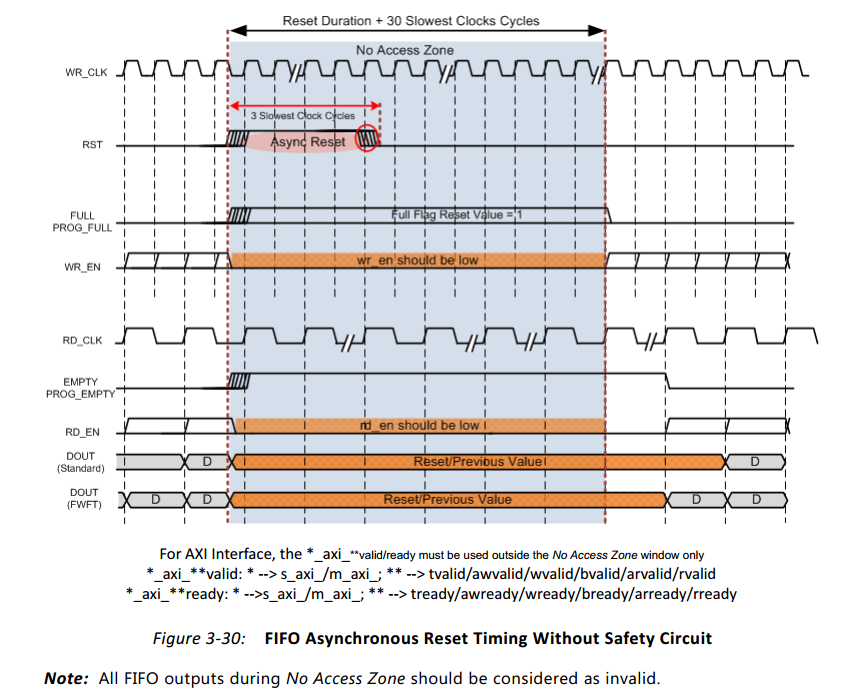

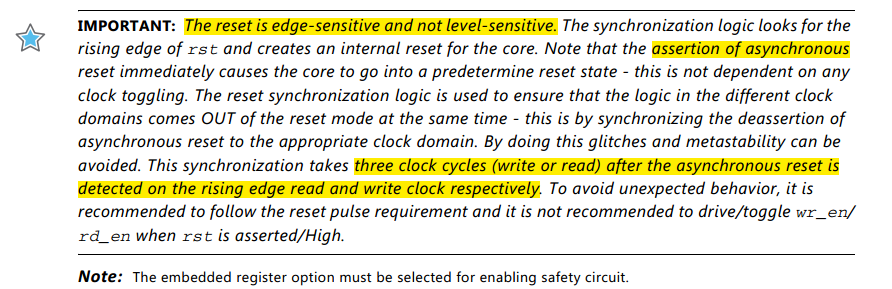

FIFO异步复位的宽度,需要保证至少3个较慢时钟的时钟周期长度。

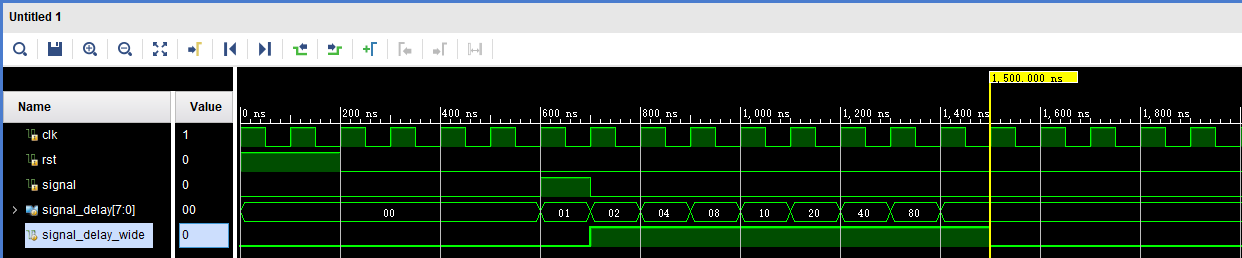

怎样对一个脉冲加宽呢?

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/08/08 19:03:20

// Design Name:

// Module Name: signal_wide

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module signal_wide( input wire clk,

input wire rst,

input wire signal

); reg [:] signal_delay = ;

reg signal_delay_wide = ;

always @ (posedge clk or posedge rst)

begin

if(rst)

begin

signal_delay <= 'b0;

signal_delay_wide <= 'b0;

end else

begin

signal_delay <= {signal_delay[:],signal};

signal_delay_wide <= | signal_delay;

end

end endmodule /* add_force {/signal_wide/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_wide/rst} -radix hex {1 0ns} {0 200ns}

add_force {/signal_wide/signal} -radix hex {0 0ns} {1 600ns} {0 700ns} */

关于FIFO异步复位的问题的更多相关文章

- FPGA同步复位异步复位

今天看了篇博客, 是拿altera的芯片和软件作例子的,讲同步异步复位的: http://blog.sina.com.cn/s/blog_bff0927b0101aaii.html 还有一个博客, h ...

- FPGA设计中的异步复位、同步释放思想

1.一个简单的异步复位例子: module test( input clk, input rst_n, input data_in, output reg out ); always@(posedge ...

- 7.FPGA中的同步复位与异步复位

1.异步复位 always @ ( posedge sclk or negedge s_rst_n ) if ( !s_rst_n ) d_out <= 1'b0; else d_out < ...

- 用4bit的counter看同步复位与异步复位

先看看这个同步复位 //date: 2013/8/20 //designer :pengxiaoen module counter_4 ( clock,reset, out ); input rese ...

- ALTERA器件中复位电路实现之-异步复位同步化

所谓异步复位同步化,就是我们通常说的异步复位同步撤除. 为了避免纯粹的同步复位和纯粹异步复位的问题,可以使用一种叫做同步化的异步复位,我们称其为第三类复位.这种复位完全结合了异步复位和同步复位的优势, ...

- verilog 异步复位代码

module reset_sync (input clk, input reset_in, output reset_out); (* ASYNC_REG = 'b1; (* ASYNC_REG = ...

- FIFO存储器

FIFO( First In First Out)简单说就是指先进先出.由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜.作为一种新型大规模集成电路,FIFO芯片 ...

- USB小白学习之路(12) Cy7c68013A固件之Slave FIFO(转)

Cy7c68013固件之Slave FIFO 转自:http://blog.csdn.net/zengshaoqing/article/details/53053539 选择SlaveFIFO传输方式 ...

- LATTICE 存储之FIFO的使用

坑,,以后填 对于Lattice 的 FIFO 存储器分为两种,见下图: 这两个的主要区别是一个后面加DC一个不加,那这个DC是什么意思呢??DC这里是Dual Clock的意思,也就是双时钟的意 ...

随机推荐

- linux小计

一.查看远程主机开放端口命令 nc -zv 10.10.79.89 5151 二.远程登录ssh/scp yum install sshpass sshpass -p youpassword scp ...

- servlet之servlet(二)

·servlet用于创建返回基于客服请求的动态页面(整个).部分页面.与数据库交互 ·servlet接口: 继承servlet接口后,要在web.xml中配置和映射servlet.配置servlet初 ...

- jq常用

1.文本框.密码框.隐藏域.文本域(id换成对应的,value属性存在,才能利用attr(‘value’) 获取值,否则返回undefined): 1.1 获取—>$(“#text”).val( ...

- redis命令String类型(四)

String 字符串类型 命令: 1> 赋值 语法:set key value 比如:set test 123 2> 取值 语法:get key 比如:get test 3> 取值并 ...

- ISAPI筛选器及对ASP源文件的保护

ISAPI筛选器及对ASP源文件的保护 2009-04-21 01:45:57 标签:ISAPI 筛选器 ASP 源文件 保护 摘要:本文介绍了利用ISAPI筛选器保护ASP源文件的方法,并给出一个实 ...

- chrome window 下的所有key josn

["postMessage","blur","focus","close","parent",&qu ...

- 开发Canvas 绘画应用(三):实现对照绘画

需求分析 在我的毕设中,提出了视图引导的概念,由两部分功能组成: (1)可以对照着图片进行绘画,即将图片以半透明的方式呈现在绘图板上,然后用户可以对照着进行绘画: (2)可以直接将简笔画图片直接拖拽到 ...

- 使用 requests

基本实例 #利用requests库发送get请求 import requests r = requests.get('http://httpbin.org/get') print(r.text) 利用 ...

- Java中对Array数组的常用操作

目录: 声明数组: 初始化数组: 查看数组长度: 遍历数组: int数组转成string数组: 从array中创建arraylist: 数组中是否包含某一个值: 将数组转成set集合: 将数组转成li ...

- 初学mysql 那些记不住的命令

修改密码: https://dev.mysql.com/doc/refman/5.7/en/resetting-permissions.html MySQL 5.7.6 之后: ALTER USER ...