Arria10中的IOPLL与fPLL

最近在用Arria10。从480降到270的过程中,IOPLL出现问题,大概是说几个Bank的IOPLL已经被占用,没有空间再给别的IOPLL去适配。

因为在工程中,所用的PLL多达35个之多,其中明确为自己手动例化的IOPLL为8个,DDR占用3个Bank所以也会占用3个IOPLL。

一时之间不知道从哪里下手,于是笔者理了下思路,觉得应该搞明白Arria10 PLL的分布,果不其然,收获颇多。

以下主要以Arria10 270为例。

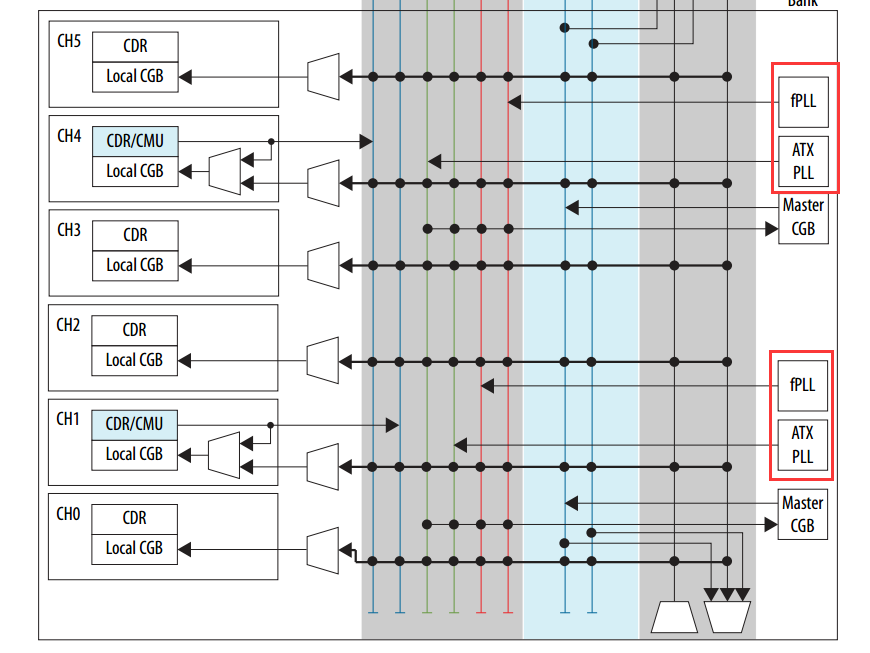

首先要搞清楚的是Arria10中的PLL共有多少个,分别分布在什么位置。从图1看GX270的有8个IOPLL和8个fPLL。从图2和图4可以看到

GX270共有8个IO Bank和4个高速接口Bank。从图3和图5可以看到一个IO Bank有一个IOPLL,一个高速接口Bank有2个fPLL和个ATX PLL(有待研究)。

图1

图2

图3

图4

图5

那现在的问题是我已经使用了11个IOPLL,是否可以把部分IOPLL转成fPLL呢?接下下要了解下PLL的特征:

(1)The fPLLs are located adjacent to the transceiver blocks in the HSSI banks. Each HSSI

bank contains two fPLLs. You can configure each fPLL independently in conventional

integer mode or fractional mode.

(2)The fPLL and I/O PLL clock outputs can drive all clock networks.

(3)The dedicated clock input pins can be either differential clocks or single-ended clocks

for I/O PLL. When you use the dedicated clock input pins as single-ended clock inputs,

only CLK_[2,3][A..L]_[0,1][p,n]pins have dedicated connections to the PLL.

fPLLs only support differential clock inputs.

(4)The I/O PLLs are located adjacent to the hard memory controllers and LVDS serializer/

deserializer (SERDES) blocks in the I/O banks. Each I/O bank contains one I/O PLL.

从以上几个特征来看,fPLL完全可以实现IOPLL的所有功能,只是在输入上要保证必须为差分。

在工程中一个HSSI Bank有两输入部分,每一部分要用到一个fPLL,刚好可以,但是例外的是有一个Bank还有一个输出部分,也要用一个fPLL.

一个HSSI Bank中的fPLL有两个,如果在这个Bank中要使用到两个以上的fPLL应该怎么办呢?这里也引出一个问题,是不同的HSSI Bank之间的fPLL能否共用?

很幸运,笔者很快从Arria10 Transciver PHY User Giude中找到了3.2.4 Reference Clock Network部分,内容如下:

The reference clock network distributes a reference clock source to either the entire

left or right side of the FPGA where the transceivers reside. This allows any reference

clock pin to drive any transmitter PLL on the same side of the device. Designs using

multiple transmitter PLLs which require the same reference clock frequency and are

located along the same side of the device, can share the same dedicated reference

clock (refclk) pin

很明显,在同一个Block中的fpLL可以被任一个参考时钟所驱动。

Arria10中的IOPLL与fPLL的更多相关文章

- Arria10中PHY的时钟线结构

发送器时钟网络由发送器PLL到发送器通道,它为发送器提供两种时钟 高速串行时钟——串化器的高速时钟 低速并行时钟——串化器和PCS的低速时钟 在绑定通道模式,串行和并行时钟都是由发送器的PLL提供给发 ...

- Arria10中的OCT功能

OCT是什么? 串行(RS)和并行(RT) OCT 提供了 I/O 阻抗匹配和匹配性能.OCT 维持信号质量,节省电路板空 间,并降低外部组件成本. Arria 10 器件支持所有 FPGA 和 HP ...

- cyclone IV中DDR的一个疑惑

的生成的DDR2 IP中DDR的时钟竟然是双向的,而在arria10中生成的DDR4则是输出,而DDR2的datasheet上也指出ck和ck#是输入,不知为什么? inout mem_clk , i ...

- Python开源框架

info:更多Django信息url:https://www.oschina.net/p/djangodetail: Django 是 Python 编程语言驱动的一个开源模型-视图-控制器(MVC) ...

- Arria10调试问题集之——480转成270中DDR4 IP重新生成的问题

在把FPGA器件从480修改成270时DDR4报错: Error (16383): Silicon revision parameter for the following EMIF/PHYLite ...

- Arria10收发器校正

收发器的模拟和数字部分都需要校正来补偿过程,电压和温度(PTV)带来的变化. Arria10使用PreSICE来执行校正过程. 校正主要包括上电校正和用户校正两方面: 上电校正在器件上电时自动执行 ...

- IOPLL动态重配

连接 Avalon -MM接口 mgmt_waitrequest:当 PLL 重配置进程开始后,此端口变高并在 PLL 重配置期间保持高电平. PLL 重配置进程完成后,此端口变低. I/O PLL重 ...

- fPLL结构及动态配置

输入参考时钟 从上图可以看到参考时钟输入的几种类型. 注意:fPLL的校正是由CLKUSR来驱动的,这个时钟必须要保持稳定. 参考时钟利用器 N计数器 N计数器会把参考时钟利用器输出进行分 ...

- mapreduce中一个map多个输入路径

package duogemap; import java.io.IOException; import java.util.ArrayList; import java.util.List; imp ...

随机推荐

- mysql导入慢解决方法

[mysqldump]max_allowed_packet = 512M [mysqld] interactive_timeout = 120 innodb_change_buffering=alli ...

- 转换 transform

转换 定义: 1.转换是使元素改变形状.尺寸和位置的一种效果 2.又称为变形,即,可以向元素应用 2D 或 3D 转换,从而对元素进行旋转.缩放.移动或倾斜 3.2D转换:使元素在 X 轴和 Y 轴平 ...

- 使用java5的注解和Sping/AspectJ的AOP 来实现Memcached的缓存

使用java5的注解和Sping/AspectJ的AOP 来实现Memcached的缓存 今天要介绍的是Simple-Spring-Memcached,它封装了对MemCached的调用,使MemCa ...

- 在浏览器中运行java applet

最近在看java applet,在eclipse中可以正常运行,于是想试试在浏览器中运行.但途中遇到很多问题,网上很多解答也不全面,于是想把自己的解决过程记录下来. [1]首先,编写的applet程序 ...

- prometheus 通过企业微信接收告警

准备工作 step 1: 访问网站 注册企业微信账号(不需要企业认证). step 2: 访问apps 创建第三方应用,点击创建应用按钮 -> 填写应用信息: prometheus 配置: # ...

- hdu 5129 (枚举) The E-pang Palace

题目;http://acm.hdu.edu.cn/showproblem.php?pid=5128. 给你n个点,问能否组成两个不相交的与坐标轴平行的矩形,能就输出两矩形的面积和,不能就输出一个字符串 ...

- Redhat Linux网卡配置与绑定

Redhat Linux的网络配置,基本上是通过修改几个配置文件来实现的,虽然也可以用ifconfig来设置IP,用route来配置默认网关,用hostname来配置主机名,但是重启后会丢失. 相关的 ...

- C单链表操作

#include <stdio.h> #include <stdlib.h> #define ElemType int #define Status int #define O ...

- 清晰易懂!关于PS入门的超详细笔记!

给大家分享一篇关于PS入门的超详细笔记!原理讲解清晰明了,虽不是新版本解析,但都是新手学习PS必掌懂的一些知识点,灰常的实用,转走收藏学习! 编辑:千锋UI设计 来源:PS学堂

- PHD实时数据对象

PHD实时数据库在化工制造业的应用 PISDK 开发包 电力企业信息化